Chapter4: The Processor

Sequential Elements(순차적 요소) -> 레지스터

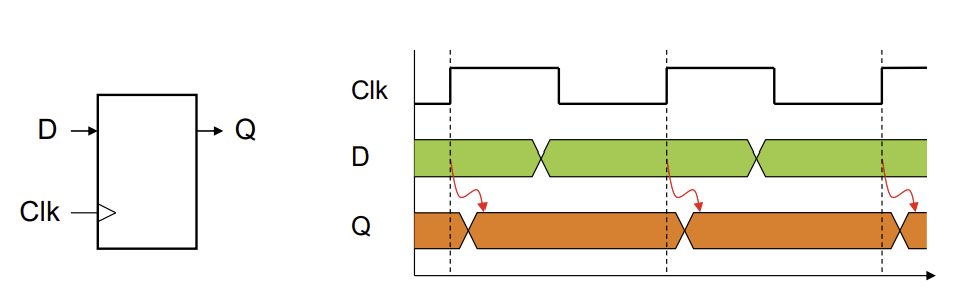

그림: 엣지 트리거(데이터를 클록 신호에 따라 저장하는 회로)의 동작

클록신호(Clk), 입력 데이터(D), 출력(Q)간의 관계를 나타냄

=> 입력 신호 D가 Clk가 1로 상승하는 순간에 D값이 Q로 전달됨(전달된 값은 다음 upbit가 될 때까지 유지되고, upbit 들어오면 데이터가 변함)

- 레지스터(register): 회로(circuit)에서 데이터를 저장하는 역할

- 클록 신호를 사용하여 저장된 값을 언제 업데이트 할지 결정함

- Edge-triggered: 클록 신호가 0에서 1로 변경될 때 값을 업데이트함

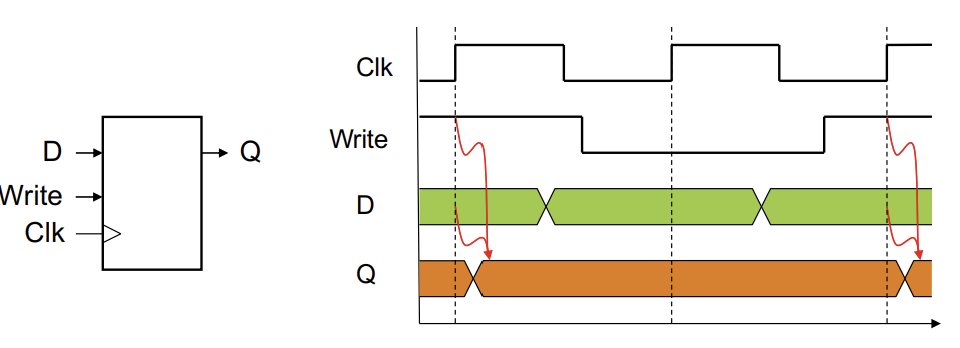

쓰기 제어 기능을 갖춘 레지스터(Register with Write Control)

- 쓰기 제어 입력이 1일때만 클록 엣지에서 업데이트됨

- 저장된 값은 나중에 필요할 때 사용됨

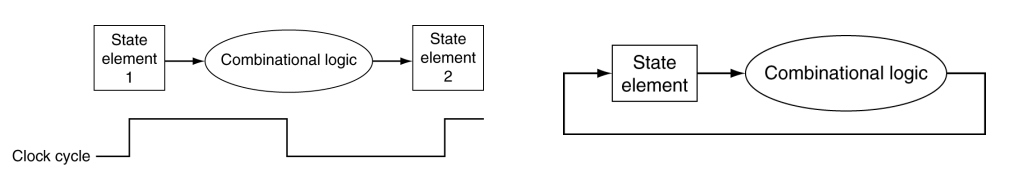

클로킹 방법론(Clocking Methodology)

-

조합 논리(combinational logic)는 클록 사이클동안 데이터를 변환함

- 클록 엣지 사이에서 변환이 이루어짐

- 입력은 상태 요소(state elements)에서 받아오고, 출력은 상태 요소로 전달됨

- 가장 긴 지연 시간이 클록 주기를 결정함

-

조합 논리는 데이터 변환을 위한 것(입력 신호 들어오면 연산 수행하여 출력 생성)

-

순차 논리(레지스터)는 데이터를 특정 시점에만 넣거나 저장하고 싶을 때를 위한 것

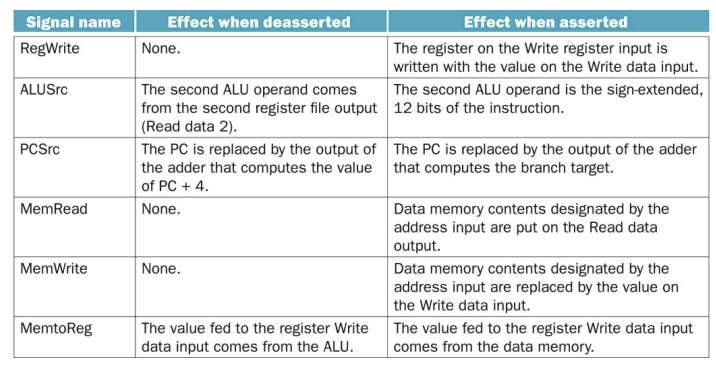

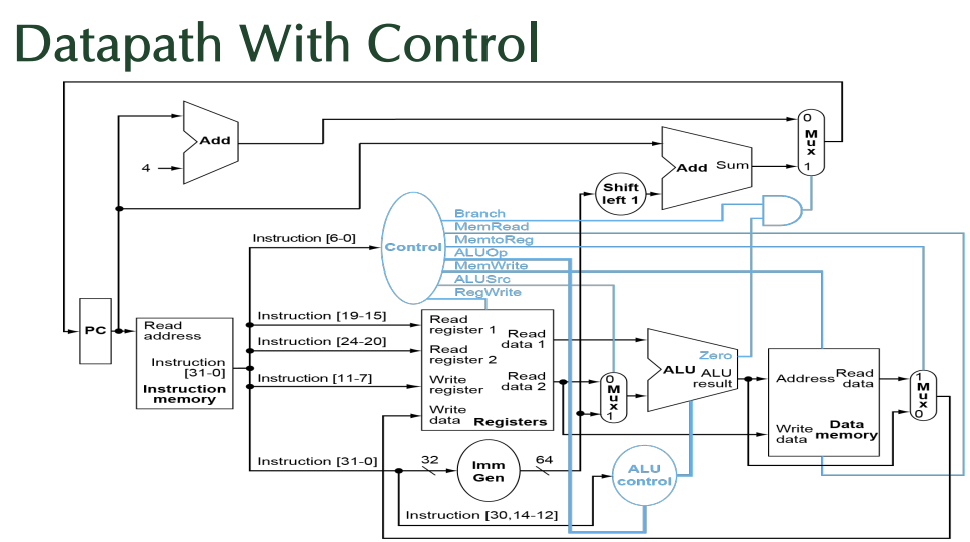

CPU의 6개의 주요 제어 신호(Main Control Unit)

어떤 역할하는 control unit인지 알아야함

CPU 데이터 경로 및 명령어 실행 흐름 나타내는 회로 다이어그램 비교

- Datapath With Control

- 데이터 경로 전체와 제어 신호 결합된 모습 (전체)

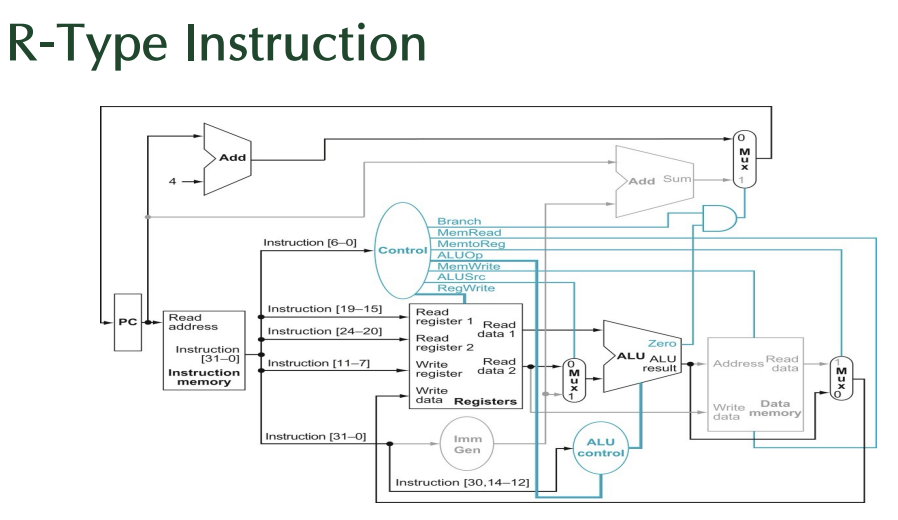

- R-Type Instruction

- R-Type 명령어는 CPU가 산술 연산과 논리 연산을 수행하는 명령어를 설명

- ALU에서 두 레지스터 값을 연산하여 결과를 다시 레지스터에 저장하는 과정이 포함됨

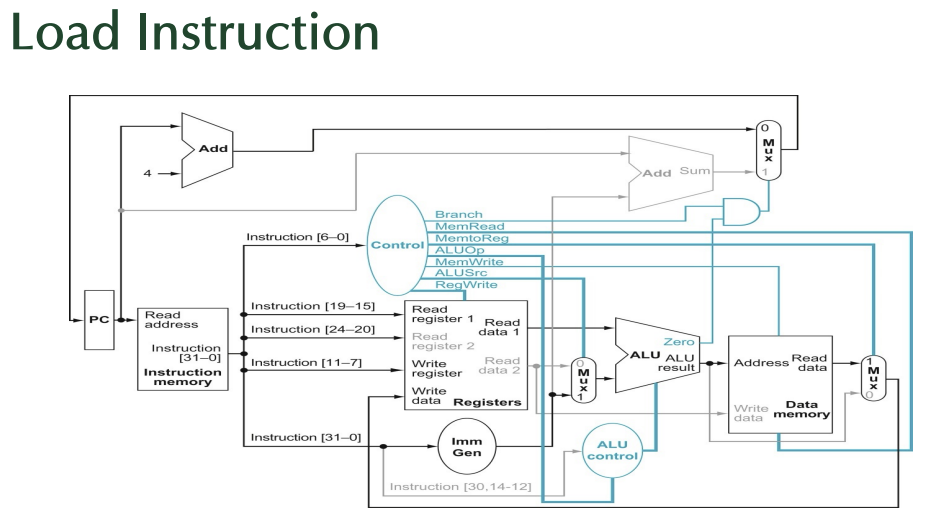

- Load Instruction

- 로드 명령어를 처리하는 데이터 경로

- 메모리에서 데이터를 읽어와 레지스터에 저장하는 명령어로, 메모리 접근을 다루는 경로가 포함됨

- Branch-on-Equal Instruction

- 분기 명령어에 대한 데이터 경로

- 조건이 참일 때 분기하는 명령어(ex.beq)를 처리하는 회로로, ALU의 출력이 0일 경우 PC(program counter: 프로그램에서 다음에 실행할 명령어의 주소 저장하는 레지스터)가 갱신됨

+) Mux: 멀티플렉서

- 선택 신호에 따라 여러 입력 중 하나를 선택하여 출력하는 회로 소자

An Overview of Pipelining

(파이프라이닝 시간 계산 어떻게?)

- 파이프라이닝: cpu에서 명령어를 여러 단계로 나누어 동시에 처리하는 기술 => 각 단계가 다른 명령어를 처리하도록 하여 동시에 여러 명령어를 병렬 시행!!

RISC-V Pipeline 단계

- 다섯 단계로, 각 단계(stage)에서 한 번의 작업(step)을 수행함

- IF (Instruction Fetch): 메모리에서 명령어를 인출함

- ID (Instruction Decode & Register Read): 명령어를 해돌가혹 레지스터에서 값을 읽어옴

- EX (Execute Operation or Calculate Address): 연산을 수행 or 메모리 주소 계산

- MEM (Memory Access): 메모리에서 피연사자에 접근

- WB (Write Back): 연산결과를 레지스터에 다시 씀

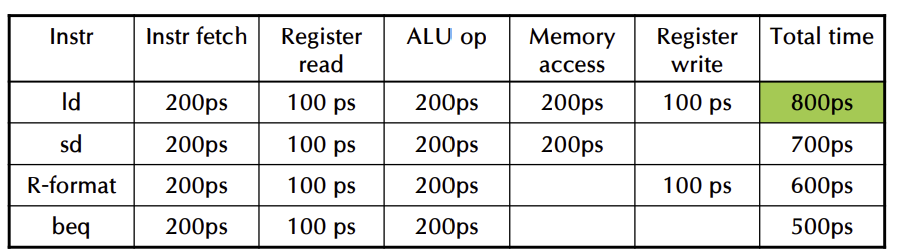

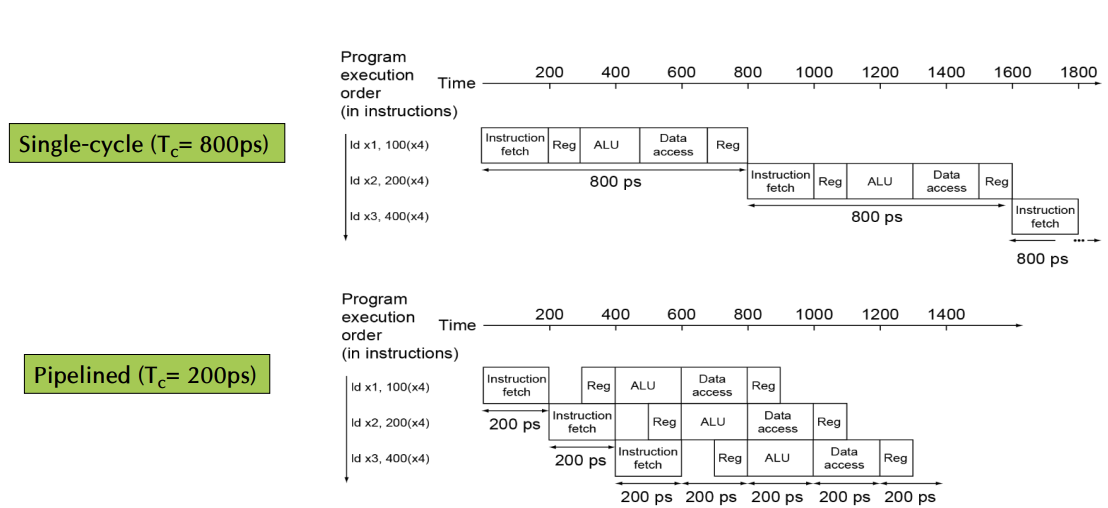

Pipeline Performance

- stage의 시간을 가정

- 레지스터 읽기 or 쓰기: 100ps 소요

- 다른 단계들: 200ps

파이프라인 데이터 경로(pipelined datapath)와 단일사이클 데이터 경로(single-cycle datapath) 비교

-

단일 사이클: 각 명령어가 하나의 클록 사이클 내에서 완료되야함

- 실행시간: 각 명령어가 걸리는 모든 단계의 시간의 합 & 모든 명령어는 동일한 클록 주기를 따름

- 따라서, 시간 제일 오래걸리는 ld에 맞춤

- 클록 사이클 시간: 800ps

-

파이프라인: 각 명령어가 여러 단계로 나뉘어 동시에 실행됨

- 실행시간: 각 단계는 독립 시행 -> 다음 명령어는 하나의 stage 끝날 때마다 바로 실행됨

- 따라서, 각 단계의 최대 지연 시간에 의해 결정됨(명령어의 각 단계중 제일 긴 단계가 200ps)

- 클록 사이클 시간: 200ps

파이프라인 속도 향상(Pipeline Speedup)

- 파이프라인이 균형을 이루면

- 각 단계가 동일한 시간동안 실행됨

- 파이프라인 방식에서의 걸리는 명령어 시간 = 비파이프라인 방식에서의 명령어 시간 ÷ 단계 수

- 파이프라인이 균형을 이루지 않으면, 속도 향상은 줄어듦

- 속도 향상은 처리량 증가로 인한 것

- 지연시간(각 명령어의 처리 시간)은 줄어들지 x

Hazards

- 다음 사이클에서 새로운 명령어의 실행을 방해하는 상황

=> 파이프라인에서 명령어가 병렬시행되어 명령어 간의 충돌, 의존성 문제 발생하면 CPU의 파이프라인 처리 속도가 저하됨 - 주요 3가지 유형

- Structure Hazards (구조적 충돌)

- 특정 명령어가 필요로 하는 자원이 바쁠 때

- Data Hazards (데이터 의존성)

- 이전 명령어의 데이터 처리가 완료되기 전까지 기다려야하는 상황일 때

- Control Hazards (제어 흐름 충돌)

- 분기 명령어로 인해 이전 명령어에 따라 제어가 달라지는 상황일 때

- Structure Hazards (구조적 충돌)

Structure Hazards

- 자원 사용에 대한 충돌(특정 명령어가 필요로 하는 자원이 바쁠 때)

- RISC-V 파이프라인에서 단일 메모리를 사용할 경우:

- load, store: 데이터를 접근해야함

- fetch: load,store하는 사이클동안 명령어 인출이 지연되야함

- 이로 인해 파이프라인 "버블"이 생김

- 버블, 스톨: 파이프라인의 실행이 잠시 멈추는 상황

- 이로 인해 파이프라인 "버블"이 생김

- 파이프라인 데이터 경로에서 필요한 점!

- 명령어 메모리와 데이터 메모리를 분리 o

- 명령어 메모리와 데이터 캐시를 분리 o

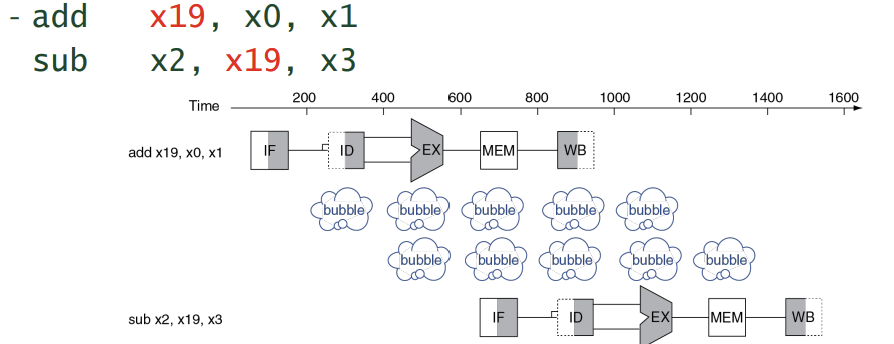

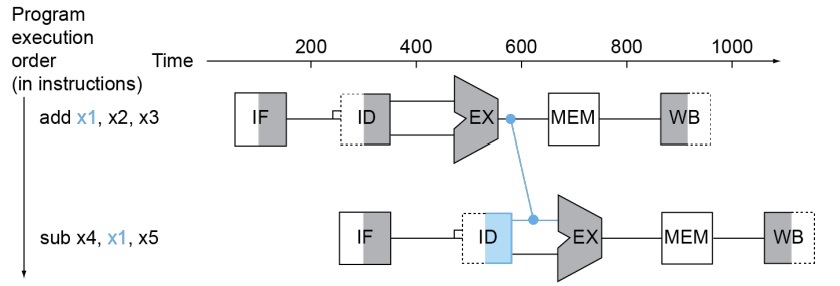

Data Hazards

- 명령어가 이전 명령어의 데이터 접근이 완료되기를 기다려야 하는 상황일 때

solution1: Forwarding(Bypassing)

- 포워딩으로 해결 된 경우

- 포워딩으로 해결 x 경우

- 파이프라인에서 연산 결과를 계산한 즉시 사용하는 방법

- 결과가 레지스터에 저장될 때까지 기다리지 않고 즉시 사용하게함

- 데이터 경로에 추가 연결을 사용하여 -> 연산 완료되자마자 전달함

- 만약 값이 필요한 시점에 아직 계산이 완료되지 x다면?

- 상황: 바로 직후 명령어에서 로드된 값을 필요로할 때(load-data 의존성 문제)- 포워딩으로 문제 해결 불가(buble이 생기고 데이터를 과거로 전달 할 수 없기 때문에)

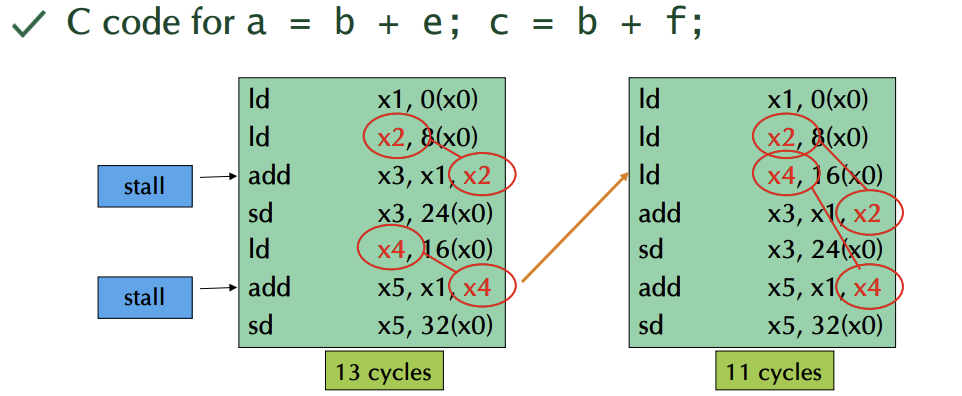

solution2: 코드 스케줄링으로 스톨 피하기

- 스톨을 피하기 위해 코드를 재배열

-로드된 결과를 즉시 사용하는 명령어와 그 사이에 다른 명령어를 배치하여 load-use 의존성 해결!! - ex. a = b + e; c = b + f;에서 코드 재배열 통해 b+e가 a에 저장되기 전에 b와 f를 연산하여 스톨을 피함!

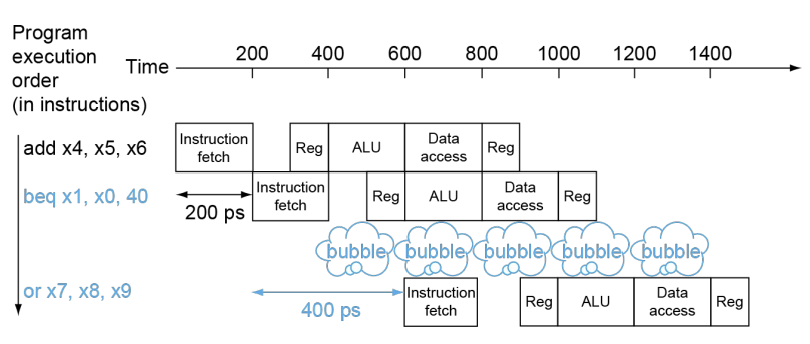

Control Hazards

- Branch(분기) 명령어가 control(제어)의 흐름을 결정함

- 다음 명령어의 Fetch가 분기 결과에 의존하게 됨

- 파이프라인은 항상 올바른 명령어를 인출할 수 없음

- 분기의 ID 단계가 진행중일 때 여전히 다음 명령어를 알 수 없을 수 있음

- RISC-V 파이프라인에서:

- 파이프라인 초기 단계에서, 레지스터를 비교하고 분기 대상을 계산하는 작업을 해야함

- ID 단계에서 비교와 계산을 수행할 하드웨어가 추가되야함

solution1: 분기에서의 스톨 (Stall on Branch)

- 분기 결과가 결정될 때까지 다음 명령어 인출을 기다림

solution2: 분기 예측 (Branch Prediction)

- 파이프라인이 길어질수록 분기 결과를 빠르게 정할 수 없음 & 스톨 인해 성능 저하 커짐

- 따라서, 그냥 분기의 결과를 예측해버리고 예측이 틀렸을 때에만 스톨 발생하게 함

- RISC-V 파이프라인에서:

- 분기가 발생하지 않는 것으로 예측

- 분기 이후 명령어를 지연없이 인출(fetch)