학습 범위

컴퓨터의 네 가지 핵심 부품 중 CPU에 대해 알아가는 시간이다.

CPU의 작동 원리

ALU와 제어장치

ALU

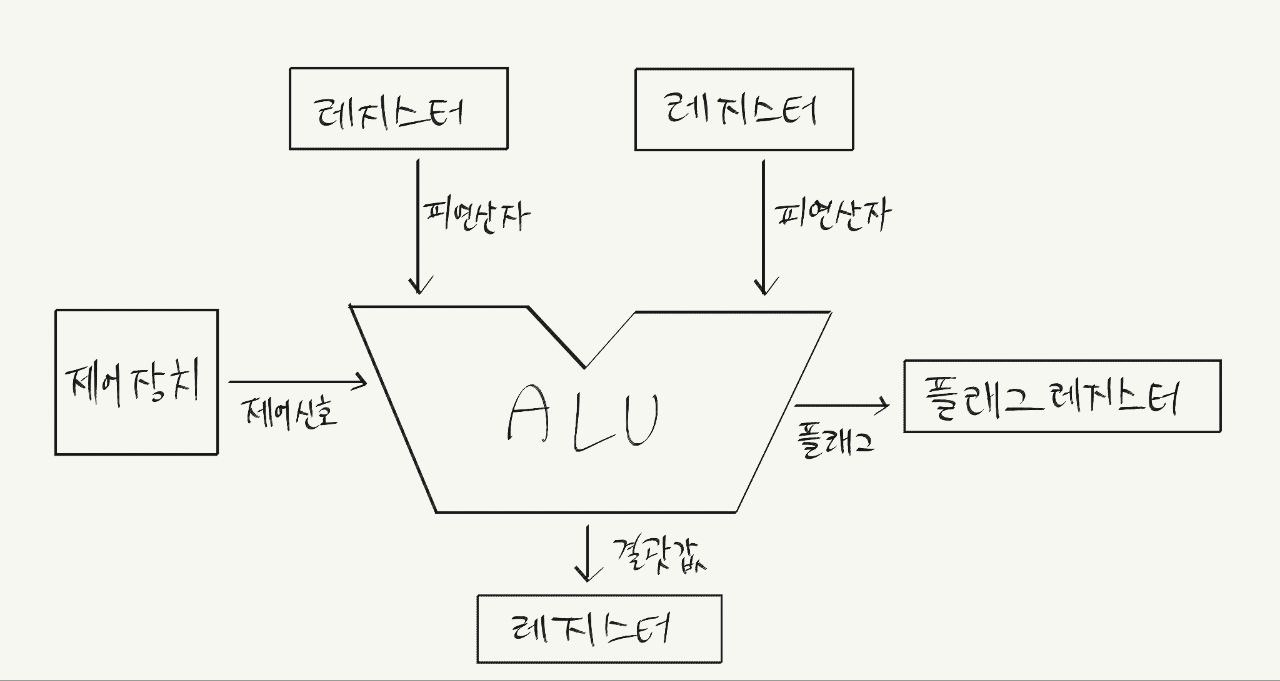

지난 시간에 알아본 바와 같이 ALU는 CPU 내부에 있는 산술논리연산장치로,

계산을 하기 위해 존재하는 부품이다.

ALU가 어떤 정보를 받아들이고 내보내는지 도식화하여 표현하면 다음과 같다.

계산을 하기 위해서는 수행할 연산과 피연산자가 필요하기에

제어장치로부터 수행할 연산을, 레지스터로부터 대상이 되는 피연산자를 받아들인다.

ALU에서 산술 연산, 논리 연산 등의 연산이 수행되고 나면 그 결과값이 레지스터에 임시 저장된다.

이 때, 연산 결과에 대한 추가적인 정보를 전달하기 위해 플래그 flag 를 사용하는데

이러한 플래그들은 플래그 레지스터 flag register 라는 특별한 레지스터에 저장된다.

ALU가 내보내는 대표적인 플래그는 다음과 같다.

| 종류 | 의미 | 사용 |

|---|---|---|

| 부호 플래그 | 연산 결과의 부호. | 결과값이 음수라면 1, 양수라면 0. |

| 제로 플래그 | 연산 결과가 0인지 여부. | 결과값이 0이라면 1, 그 외의 값이라면 0. |

| 캐리 플래그 | 연산 결과 올림수나 빌림수 발생 여부. | 올림수/빌림수 발생 시 1, 미발생 시 0. |

| 오버플로우 플래그 | 오버플로우 발생 여부. | 오버플로우 발생 시 1, 미발생 시 0. |

| 인터럽트 플래그 | 인터럽트 가능 여부. | 인터럽트 가능 시 1, 불가능 시 0. |

| 슈퍼바이저 플래그 | 커널 모드인지 사용자 모드인지 여부. | 커널 모드 실행 시 1, 사용자 모드 실행 시 0. |

인터럽트와 슈퍼바이저는 아직 배우지 않았으니 일단 그런 게 있다, 하고 넘어가도록 하자.

ALU 내부에는 계산을 위한 다양한 회로가 존재하지만,

우리는 구체적인 컴퓨터 회로는 다루지 않을 것이므로 그런 게 있다, 하는 정도만 알고 넘어가자.

대표적인 계산 회로로는 다음과 같은 것들이 있다.

- 가산기 := 덧셈을 위한 계산 회로

- 보수기 := 뺄셈을 위한 계산 회로

- 시프터 := 시프트 연산을 위한 계산 회로

- 오버플로우 검출기 := 오버플로우 발생 여부 확인을 위한 계산 회로

제어장치

ALU에 수행할 연산을 전달하는 제어장치에 대해 알아보도록 하겠다.

엄밀히 말하면 ALU뿐만 아니라 컴퓨터의 여러 부분에 제어 신호를 내보내고 명령어를 해석하는 장치지만.

제어장치는 기본적으로 제어 신호를 내보내고 명령어를 해석하는 부품이며,

여기서 제어 신호는 컴퓨터 부품들을 관리하고 작동시키기 위한 일종의 전기 신호다.

제어장치는 CPU 구성 요소 중 가장 정교하게 설계된 부품으로, 제조사마다 고유의 방식을 사용한다.

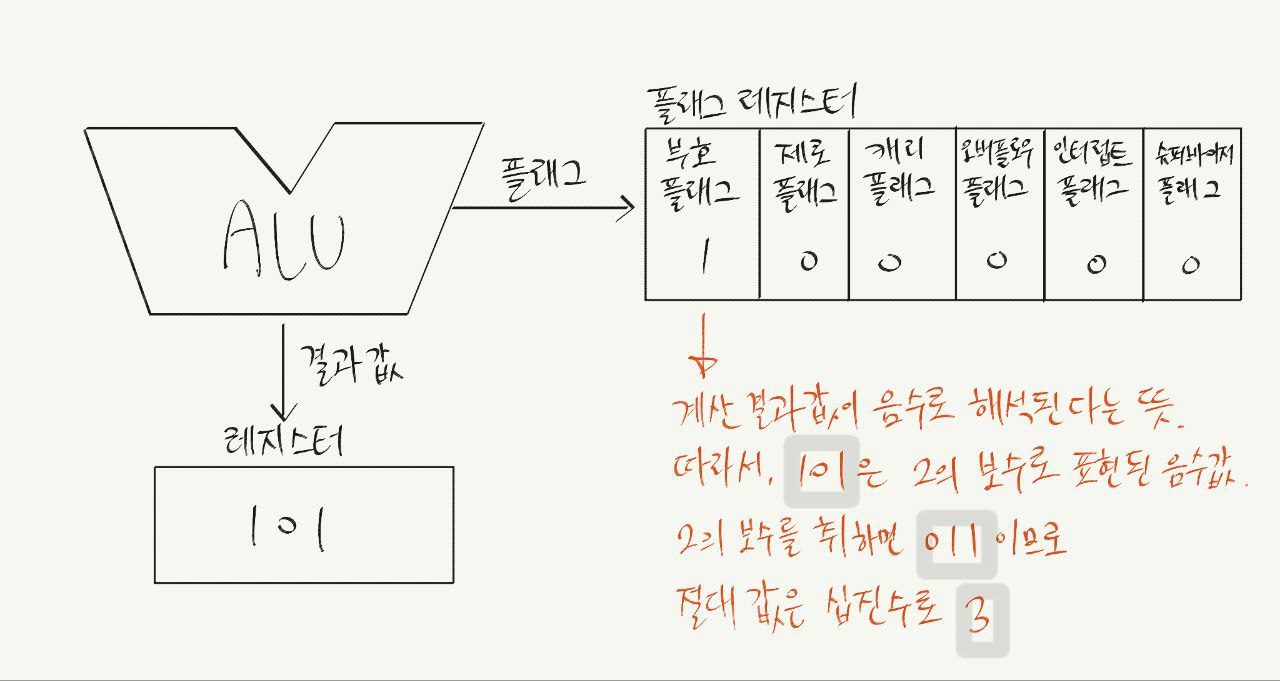

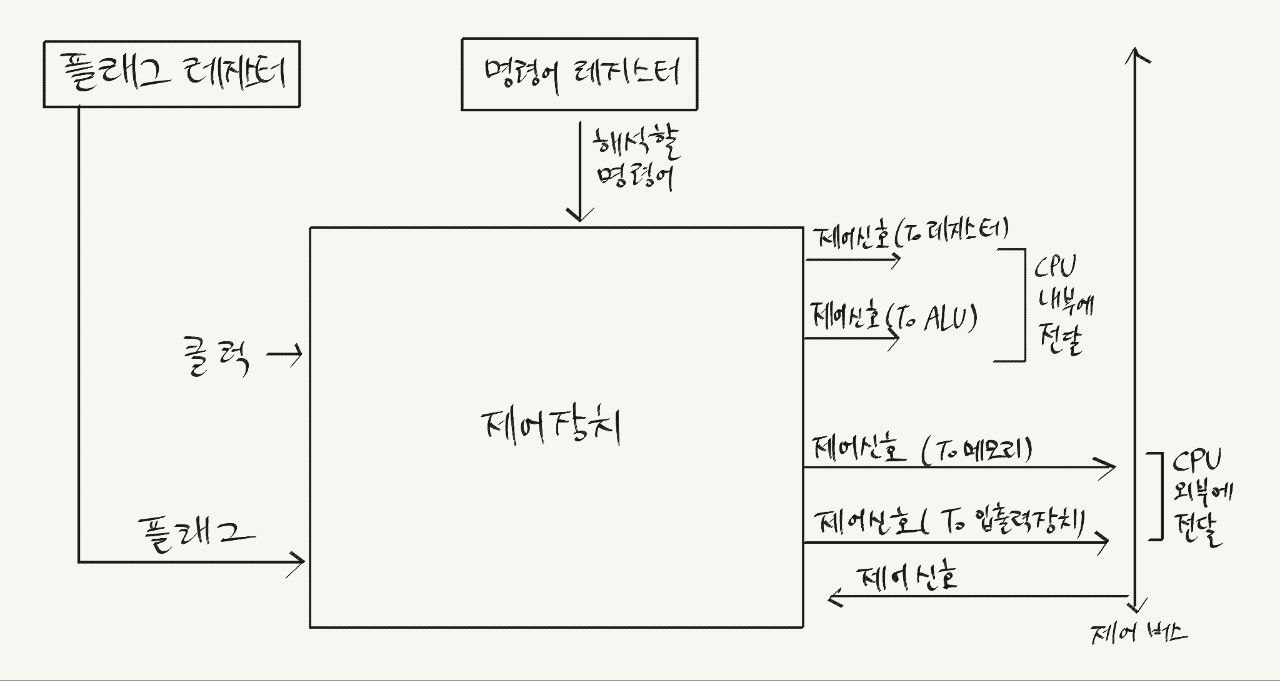

제어장치가 어떤 정보를 받아들이고 내보내는지 도식화하여 표현하면 다음과 같다.

제어장치는 다음과 같은 정보를 받아들인다.

- 클럭 신호

클럭 clock 이란 컴퓨터의 부품을 일사불란하게 움직일 수 있게 하는 시간 단위를 의미.

클럭 주기에 맞춰 클럭 동안 특정 동작을 수행하므로,

정보를 읽어오거나 내보낼 때도 받아들인 클럭 신호를 기준으로 동작한다. - 해석해야 할 명령어

명령어 레지스터라는 특별한 레지스터에 저장되어 있는 명령어를 받아와서 해석한다.

이를 기반으로 다른 부품들에 제어 신호를 보내게 된다. - 플로그 레지스터 속 플러그 값

제어 신호 발생 시 이 값을 참고. - 시스템 버스, 그중에서 제어 버스로 전달된 제어 신호

CPU 외부 장치에서 제어 신호를 발생시키기도 한다.

그리고 다음과 같은 정보를 내보낸다.

- CPU 외부에 전달하는 제어 신호

- 메모리에 전달 ⇒ 메모리에 저장된 값을 읽거나 새로운 값을 쓸 때

- 입출력장치(보조기억장치 포함)에 전달 ⇒ 입출력장치의 값을 읽거나 새로운 값을 쓸 때

- CPU 내부에 전달하는 제어 신호

- ALU에 전달 ⇒ 수행할 연산을 지시할 때

- 레지스터에 전달 ⇒ 레지스터 간 데이터를 이동하거나 레지스터에 저장된 메모리를 해석할 때

더 알아보기

레지스터

제조사마다 CPU 구현 방식이 달라 상용화된 CPU 속 레지스터들은 CPU마다 이름, 크기, 종류가 다르다.

구체적인 특정 제품의 레지스터를 알고 싶다면 제조사 홈페이지나 공식 문서 등에서 확인할 수 있다.

여기서는 많은 CPU가 공통적으로 포함하고 있는 여덟 개의 레지스터를 다루도록 하겠다.

- 프로그램 카운터 PC; Program Counter

다음에 메모리에서 가져올 명령어의 주소를 저장.

일부 CPU에서는 명령어 포인터 IP; Instruction Pointer 라고도 불린다.

기본적으로 저장된 값이 명령어가 차지하고 있는 크기만큼 증가하지만

특정 메모리 주소로 실행 흐름을 이동하는 명령어를 만나면 해당 메모리 주소를 갖는다. - 명령어 레지스터 IR; Instruction Register

방금 메모리에서 읽어 들인 명령어를 저장.

제어장치에서 이를 받아들이고 해석하여 제어 신호를 내보낸다. - 메모리 주소 레지스터 MAR; Memory Address Register

CPU가 읽어 들이고자 하는 주소 값을 주소 버스로 보낼 때 메모리 주소를 임시 저장. - 메모리 버퍼 레지스터 MBR; Memory Buffer Register

데이터, 명령어 등 메모리와 주고받을 값을 저장.

데이터 버스로 주고받기 전후에 메모리에 쓸 값과 메모리로부터 전달받은 값을 임시 저장.

일부 CPU에서는 메모리 데이터 레지스터 MDR; Memory Data Register 라고도 불린다. - 플래그 레지스터

ALU 연산 결과 또는 CPU 상태에 대한 부가적인 정보 저장. - 범용 레지스터

다양하고 일반적인 상황에서 자유롭게 사용 가능. - 스택 포인터

스택 주소 지정 방식이라는 주소 지정 방식에서 사용.

스택의 맨 윗부분의 주소를 저장하여, 데이터를 넣고 뺄 때마다 데이터가 차지하는 공간만큼 값이 변한다. - 베이스 레지스터

변위 주소 지정 방식, 그 중에서도 베이스 레지스터 주소 지정 방식이라는 주소 지정 방식에서 사용.

"스택 주소 지정 방식"과 "변위 주소 지정 방식"이라는 생소한 개념이 언급되었다.

이에 대해 간단히 알아보도록 하자.

- 스택 주소 지정 방식

스택과 스택 포인터를 이용한 주소 지정 방식.

마지막으로 저장한 값의 주소를 스택 포인터가 가리키고 있으며,

그로부터 얼마나 아래 저장되어 있는지를 통해 필요한 데이터를 알아낸다.

스택은 메모리를 스택처럼 사용하기 위해 지정되어 있는 스택 영역이라는 곳에 존재. - 변위 주소 지정 방식

오퍼랜드 필드의 값을 변위 삼아 특정 레지스터 값을 더하여 유효 주소를 얻어내는 주소 지정 방식.- 상대 주소 지정 방식

오퍼랜드와 프로그램 커운터의 값을 더하여 유효 주소를 얻는 방식.

실행하려는 명령어와 데이터의 상대적 위치를 변위로 사용.

모든 코드를 실행하는 게 아닌, 분기하여 특정 주소의 코드를 실행할 때 주로 사용. - 베이스 주소 지정 방식

오퍼랜드와 베이스 레지스터의 값을 더하여 유효 주소를 얻는 방식.

베이스 레지스터 속 기준 주소로부터의 상대적 위치를 변위로 사용.

- 상대 주소 지정 방식

더 알아보기

【↗[컴퓨터 공학 기초 강의] 10강. CPU의 내부 구성 - 레지스터】

【↗[저자 GitHub] 대중적인 CPU―Intel x86과 ARM―의 레지스터】

명령어 사이클과 인터럽트

명령어 사이클

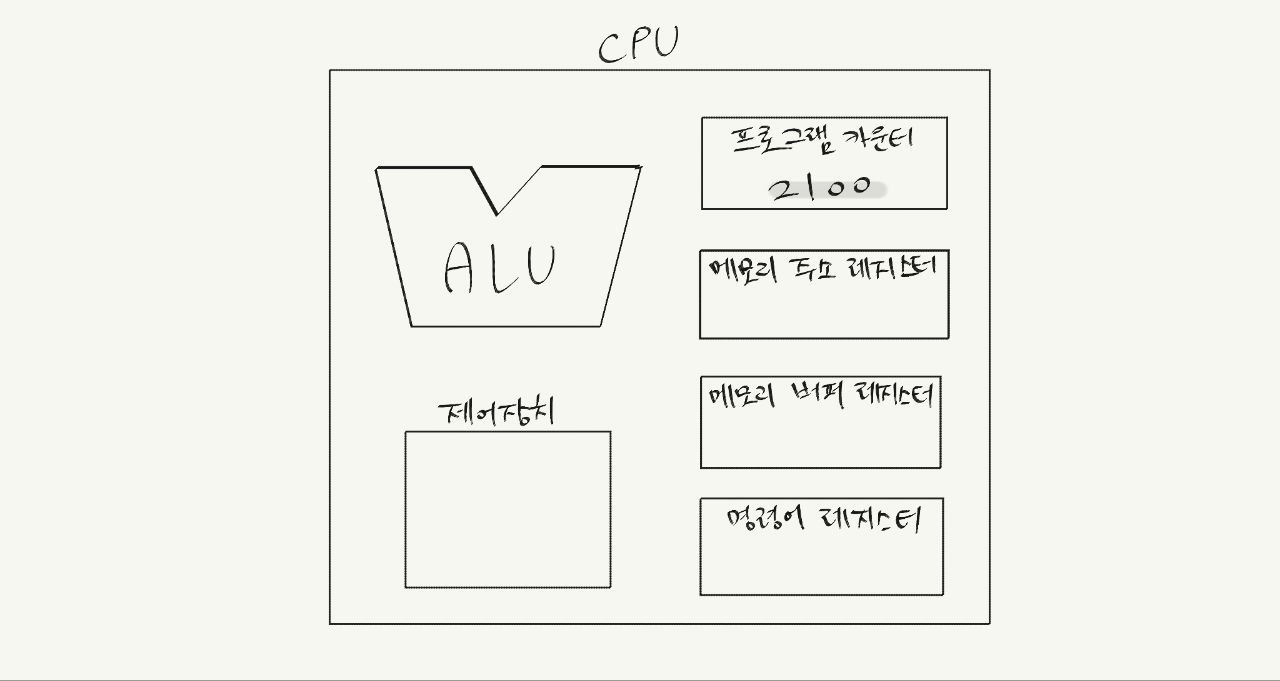

CPU는 명령어 사이클 instruction cycle 을 반복하며 명령어를 처리해나가며,

때로는 이 사이클이 끊기는 인터럽트 interrupt 가 발생하곤 한다.

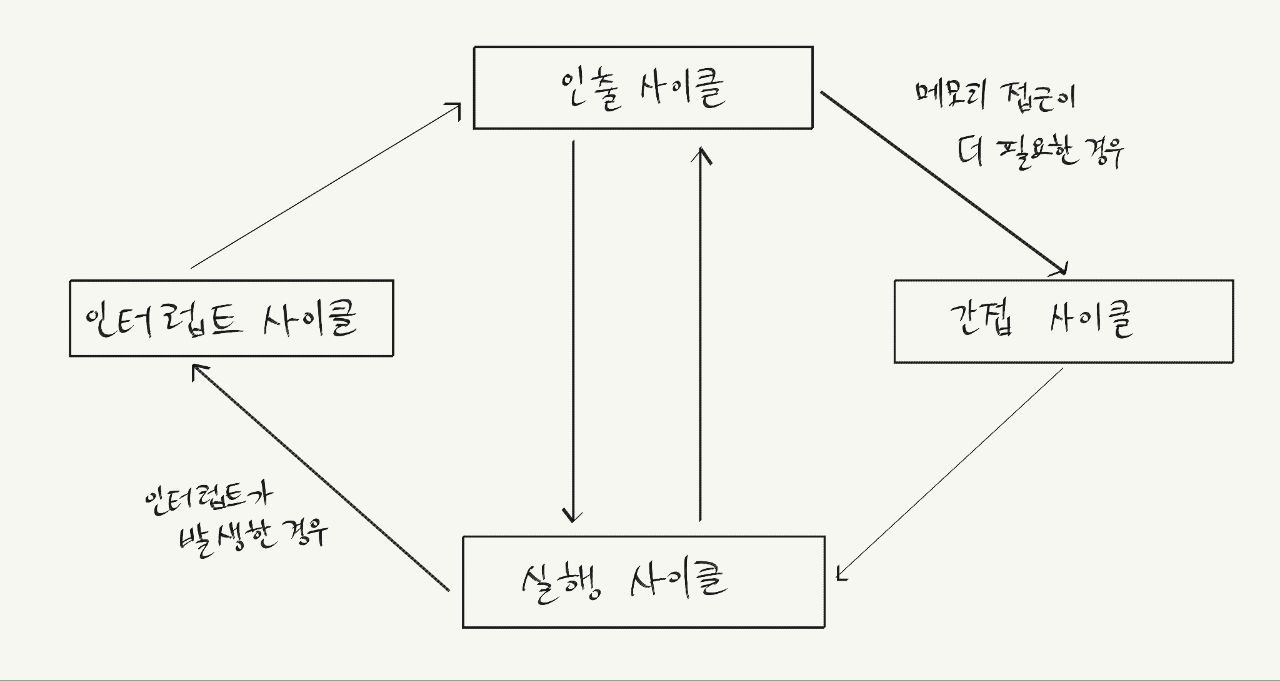

명령어 사이클은 다음과 같은 단계로 이루어진다.

- 인출 사이클 fetch cycle

메모리에 있는 명령어를 CPU로 가지고 오는 단계.

프로그램 카운터의 값을 메모리 주소 레지스터에 복사한 뒤

제어 버스와 주소 버스를 통해 해당 메모리의 값을 요청하고,

데이터 버스를 통해 메모리 버퍼 레지스터에 받아온 값을 명령어 레지스터에 복사한다. - 실행 사이클 execution cycle

CPU로 가져온 명령어를 실행하는 단계.

제어장치가 명령어 레지스터에 담긴 값을 해석하고, 제어 신호를 발생시킨다. - 간접 사이클 indirect cycle

명령어 실행을 위해 메모리 접근이 한 번 더 필요한 경우,

실행 사이클 이전에 필요한 값을 가져오는 단계.

인출 사이클에서처럼 값을 받아와 범용 레지스터에 복사한다.

명령어에 따라 필요한 경우에만 수행한다. - 인터럽트 사이클 interrupt cycle

인터럽트가 발생한 경우에만 수행하며, 이를 처리하는 단계.

여기서 "인터럽트"에 대해 좀 더 알아보자.

인터럽트

인터럽트는 CPU로 하여금 수행 중인 작업을 중단하게 하는 신호로, 다음과 같이 구분된다.

- 동기 인터럽트 synchronous interrupts

CPU에 의해 발생하는 인터럽트.

예외 exception 이라고도 불린다.

프로그래밍에서 "예외 처리"를 한다고 할 때 바로 그 예외.

이것을 적절하게 처리한 후 본래 하던 작업으로 되돌아와 실행을 재개한다.- 폴트 fault

예외 처리 직후, 예외가 발생한 명령어부터 실행 재개.

인터럽트를 발생시킨 원인을 해결한 뒤 해당 명령어를 다시 실행한다. - 트랩 trap

예외 처리 직후, 예외가 발생한 명령어 다음 명령어부터 실행 재개.

인터럽트를 발생시킨 명령어는 실패했다고 치고, 다음 것을 마저 이어간다.

주로 디버깅할 때 중단점을 만들기 위해 사용. - 중단 abort

실행 중인 프로그램을 강제로 중단시킬 수밖에 없는 심각한 오류 발견 시 발생.

본래 하던 작업으로 돌아오지 않고 중단시킨다. - 소프트웨어 인터럽트 software interrupt

시스템 호출이 발생했을 때 발생.

이건 나중에 시스템 호출에 대해 배울 때 알아보도록 하자.

- 폴트 fault

- 비동기 인터럽트 asynchronous interrupts

일반적으로 말하는 인터럽트로, 하드웨어 인터럽트 hardware interrupts 라고도 한다.

명령어를 효율적으로 처리하기 위해 사용.

ex. CPU보다 속도가 느린 입출력 작업을 기다릴 때 지속적으로 완료 여부를 물어보기 보다는, 다른 일을 하고 있다가 입출력 작업 완료 인터럽트를 받으면 필요한 입출력 작업을 수행한다.

비동기 인터럽트를 처리하는 순서는 다음과 같다.

- 입출력장치에서 CPU로 인터럽트 요청 신호 전송

- CPU는 실행 사이클을 마치고 인출 사이클 시작 전 항상 인터럽트 여부 확인

- CPU는 인터럽트 요청을 확인하고 인터럽트 플래그를 통해 인터럽트 받아들일 수 있는지 확인

- 인터럽트를 받아들일 수 있다면 지금까지의 작업 백업

- CPU는 인터럽트 벡터를 참조하여 인터럽트 서비스 루틴 실행

여기서 중요한 키워드를 따로 살펴보면,

- 인터럽트 요청 신호

CPU에 인터럽트 가능 여부를 확인하기 위한 신호. - 인터럽트 플래그 interrupt flag

CPU가 인터럽트를 받아들일지 무시할지 결정하는 플래그.

어떤 인터럽트는 이 플래그가 무시하기로 설정되어 있어도 무조건 실행된다. - 인터럽트 서비스 루틴 ISR; Interrupt Service Routine

인터럽트를 처리하기 위한 프로그램으로, 인터럽트 종류에 따라 어떻게 처리해야 할지 정보를 담고 있다.

인터럽트 핸들러 interrupt handler 라고도 한다.

이것을 실행하고 나면 본래 하던 작업으로 되돌아가는데,

이를 위해 인터럽트 서비스 루틴 실행 전, 기존에 하던 작업과 관련된 레지스터 정보는 스택에 백업된다. - 인터럽트 벡터 interrupt vector

특정 인터럽트 발생 시 실행해야 할 인터럽트 서비스 루틴을 식별하기 위한 정보.

인터럽트 요청 신호를 보내는 장치에서 데이터 버스를 통해 CPU로 전달한다.

이 모든 과정을 포함한 명령어 사이클을 간단히 도식화하면 다음과 같다.

더 알아보기

CPU 성능 향상 기법

빠른 CPU를 위한 설계 방법

우리는 앞서 컴퓨터 부품들이 클럭 신호에 맞춰 동작한다는 이야기를 했다.

그렇다면 이 신호의 주기를 보다 빠르게 한다면 CPU의 명령어 사이클의 반복 속도도 빨라지고

전반적인 컴퓨터 속도가 빨라지는 것 아닐까?

⇒ 실제로 클럭 속도가 높은 CPU는 일반적으로 성능이 좋다.

클럭 신호가 1초에 번 전달된다면 클럭 속도는 Hz[헤르츠] 라고 한다.

CPU의 기본 속도(Base)가 2.5GHz라면, 1초에 2.5×10=25억 번의 클럭이 반복됨을 의미한다.

CPU는 평소에는 기본 속도를 유지하다가 고성능을 요하는 순간에는 속도를 높이곤 하는데,

최대 클럭 속도를 강제적으로 끌어올리는 기법을 오버클럭킹 ovverclocking 이라고 한다.

다만, 클럭 속도를 너무 끌어올리면 발열 문제가 심각해진다.

보다 안전한 방법으로 CPU 성능을 높이는 방법으로는 CPU의 코어와 스레드 수를 늘리는 방법이 있다.

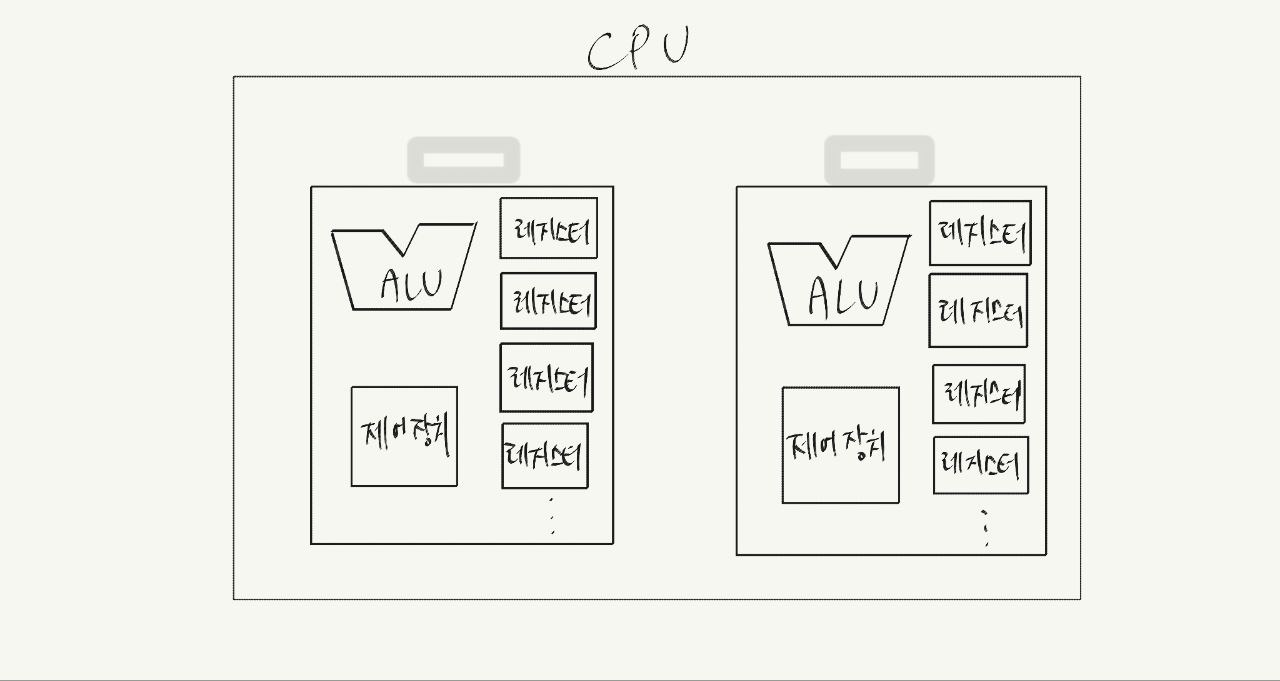

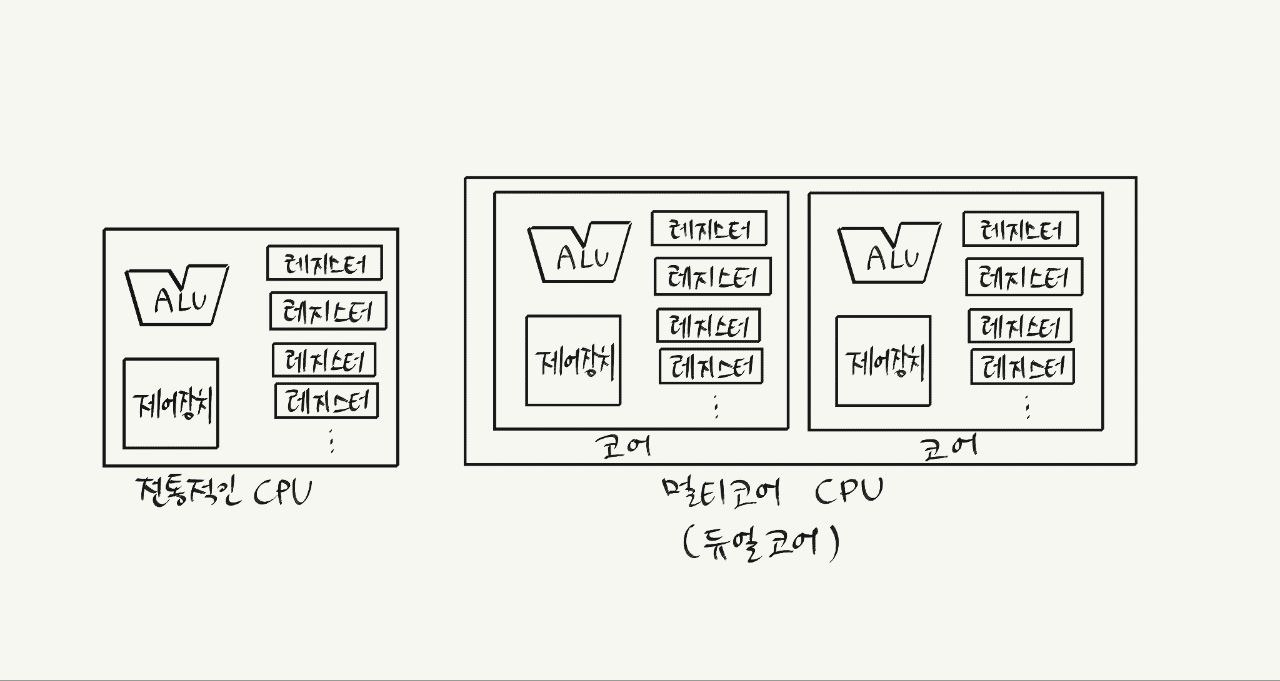

전통적인 관점에서의 CPU는 "명령어를 실행하는 부품" 하나로 이루어져 있는데

기술의 발전으로 현대의 CPU는 이를 여러 개 가질 수 있다.

이러한 부품을 코어 core 라고 하며,

코어를 여러 개 가진 CPU를 멀티코어 CPU multi-core CPU 또는 멀티코어 프로세서라고 하며

그 개수에 따라 듀얼코어, 쿼드코어와 같이 부른다.

다만, 코어를 늘인다고 그에 비례하여 성능이 좋아지지는 않으며 어느 정도 좋아질 뿐이다.

그리고 명령어를 적절하게 분배하지 못한다면 성능에 유의미한 영향을 주지 못한다.

스레드 thread 의 경우, 사전적 의미로는 "실행 흐름의 단위"라는 뜻인데,

CPU에서의 스레드는 프로그래밍에서의 스레드와 용례가 다르므로 헷갈리지 않도록 주의하자.

CPU에서 사용되는 하드웨어적 스레드와 프로그래밍에서 사용되는 소프트웨어적 스레드를 구분해서 살펴보자.

- 하드웨어적 스레드

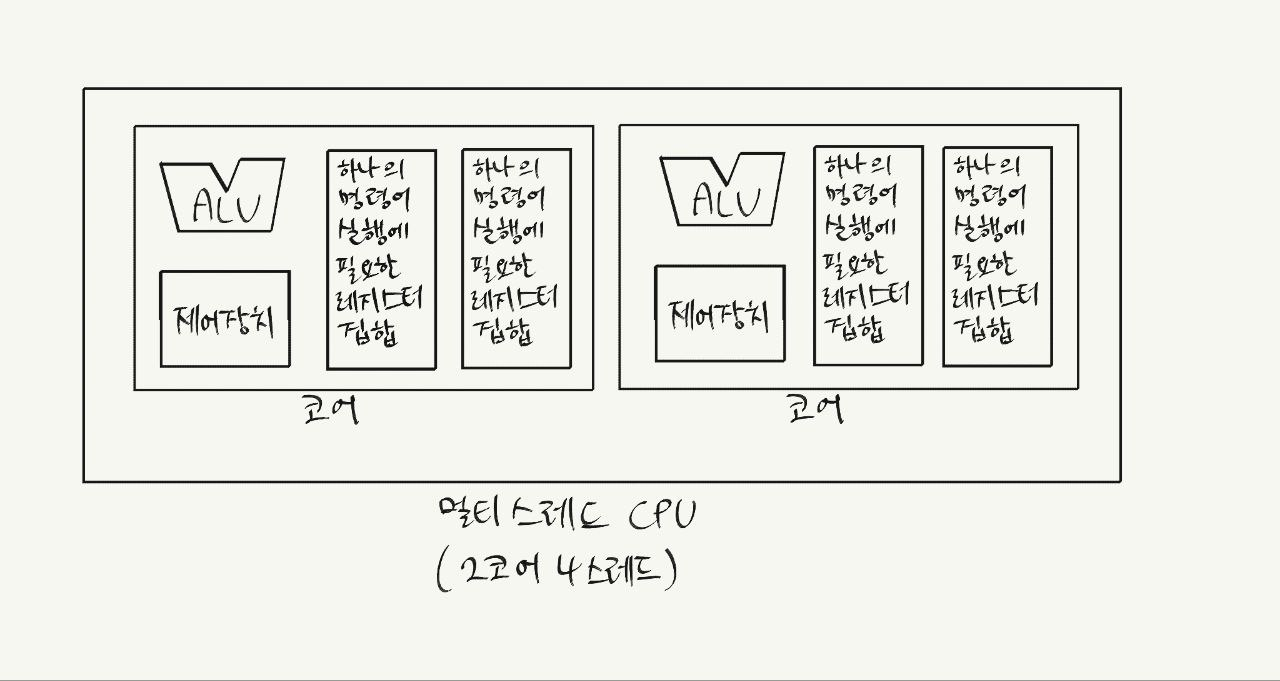

스레드는 하드웨어적으로 "하나의 코어가 동시에 처리하는 명령어 단위"를 의미한다.

우리가 앞에서 다룬 CPU는 1코어 1스레드 CPU였지만 여러 스레드를 지원하는 코어도 있다.

2스레드 코어를 2개 가진 CPU는 2코어 4스레드 CPU로서, 한 번에 네 개의 명령어 처리가 가능하다.

이런 CPU를 멀티스레드 CPU multithread CPU 또는 멀티스레드 프로세서라고 한다.

(인텔에서는 자사 멀티스레드 기술에 하이퍼스레딩 hyper-threading 이라는 이름을 붙였다.) - 소프트웨어적 스레드

스레드는 소프트웨어적으로 "하나의 프로그램에서 독립적으로 실행되는 단위"를 의미한다.

프로그래밍, 운영체제 등에서 접하는 일반적인 스레드 개념.

멀티스레드 프로세서의 핵심은 레지스터다.

하나의 명령어를 처리하기 위해 꼭 필요한 레지스터를 여러 개 만들어

하나의 코어에서 여러 개의 명령어를 동시에 실행할 수 있도록 한다.

프로그램 관점에서는 스레드가 하나의 CPU처럼 보여 논리 프로세서 logic processor 라고도 한다.

더 알아보기

명령어 병렬 처리 기법

CPU의 성능을 높이기 위해서는 클럭 속도를 높이고 멀티코어, 멀티스레드를 지원하는 것도 중요하지만

가지고 있는 CPU 자원을 낭비하지 않고 잘 사용할 수 있도록 하는 것도 중요하다.

명령어 병렬 처리 기법을 통해 CPU를 쉬지 않고 작동시키는 방법에 대해 알아보겠다.

대표적인 명령어 병렬 처리 기법으로는 명령어 파이프라이닝, 슈퍼스칼라, 비순차적 명령어 처리 등이 있다.

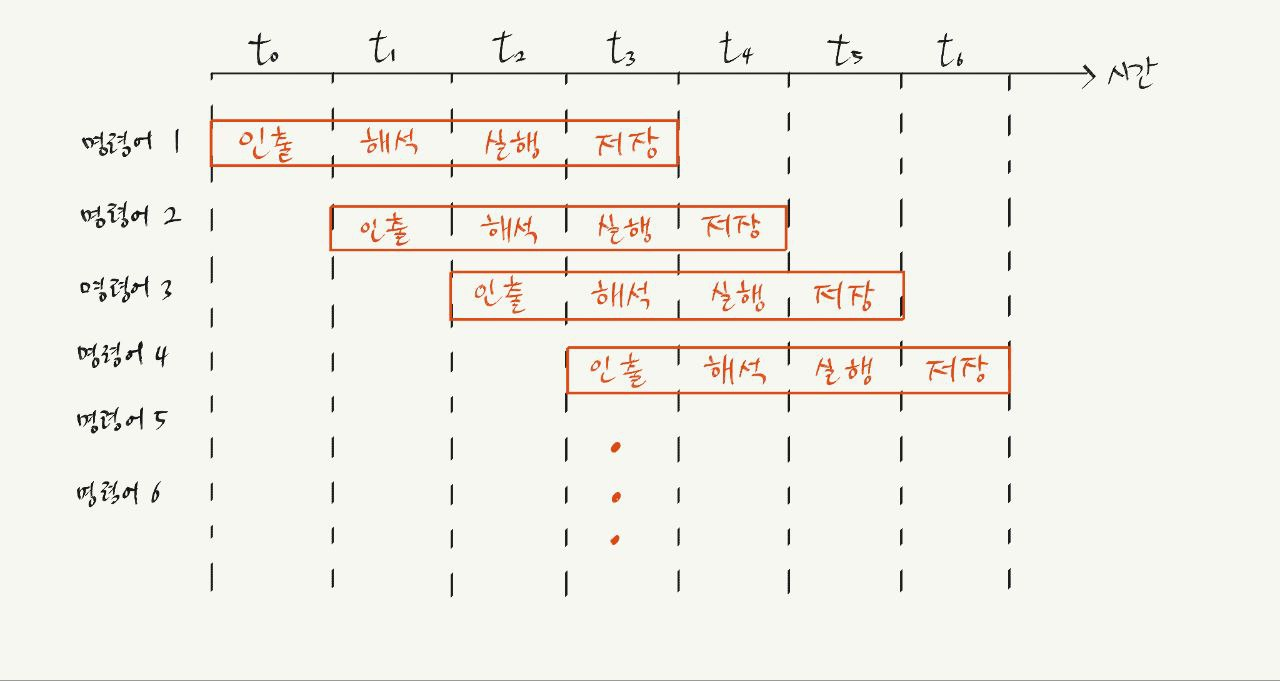

명령어 파이프라이닝 instruction pipelining

명령어 처리 과정을 클럭 단위로 명령어 인출/명령어 해석/명령어 실행/결과 저장 단계로 나눌 때

같은 단계가 겹치지 않는다면 CPU는 각 단계를 동시에 실행할 수 있다는 점을 이용.

이를 간단히 도식화하면 다음과 같다.

직렬적으로 실행했다면 명령어 4개를 실행하는 데 16클락이 소비되었겠지만

이와 같이 실행하면 6클락만에 명령어 4개를 처리할 수 있다.

다만, 몇 가지 상황에서 성능 향상에 실패할 수 있는데,

이를 파이프라인 위험 pipeline hazard 이라고 부른다.

명령어 파이프라이닝은 이러한 파이프라인 위험을 피하는 범위 내에서 명령어를 병렬 처리한다.

- 데이터 위험 data hazard

병렬적으로 처리하고자 하는 명령어 간에 데이터 의존성이 있을 경우 발생.

이전 명령어에 의해 변조된 값을 이후 명령어에서 사용할 경우 발생할 수 있다. - 제어 위험 control hazard

분기 등의 이유로 프로그램 실행 흐름이 바뀌어 미리 인출해둔 명령어를 사용할 수 없을 때 발생.

분기 예측 branch prediction 기법을 통해 완화할 수 있지만 한계는 있다. - 구조적 위험 structural hazard

병렬적으로 처리하고자 하는 명령어들이 동일한 CPU 부품을 사용하고자 할 때 발생.

자원 위험 resource hazard 라고도 한다.

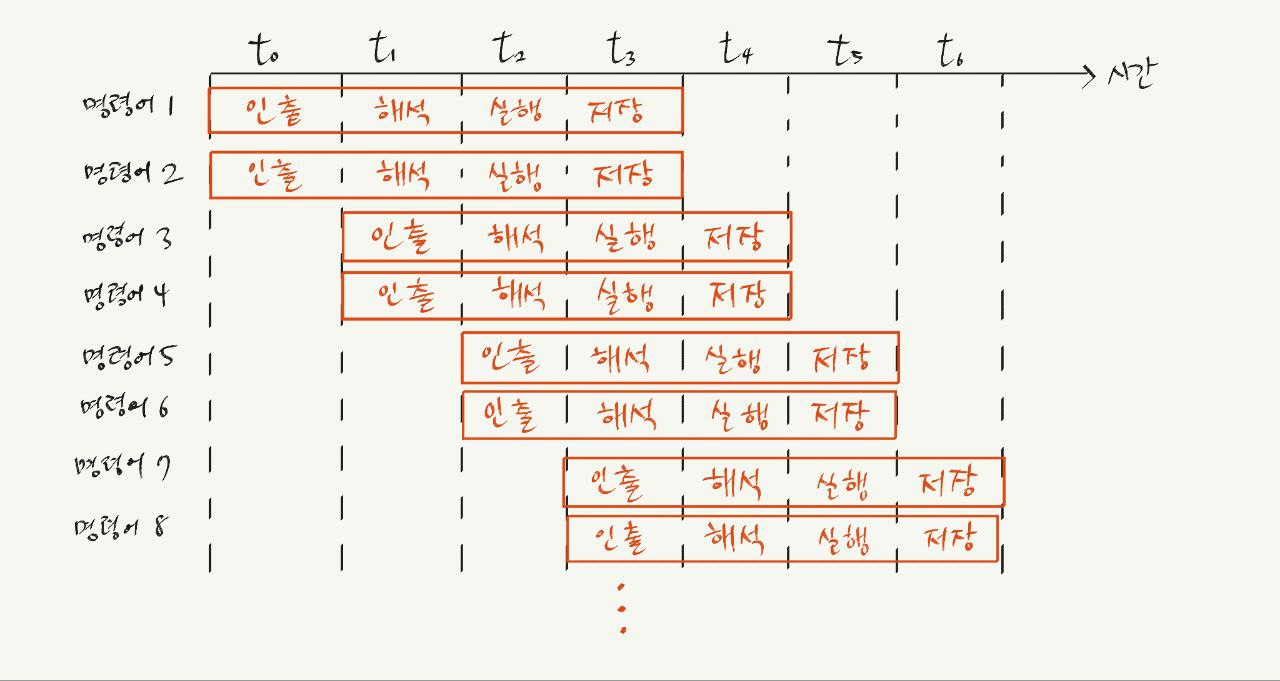

슈퍼스칼라 superscalar

CPU 내부에 여러 개의 파이프라인을 포함한 구조.

명령어 파이프라이닝 방식을 여러 개의 파이프라인에서 수행하는 것.

이를 간단히 도식화하면 다음과 같다.

이러한 방식의 처리가 가능한 CPU를 슈퍼스칼라 CPU 또는 슈퍼스칼라 프로세서라고 한다.

이론적으로는 파이프라인 개수에 비례하여 처리 속도가 빨라지지만, 파이프라인 위험 등의 변수 존재.

하나의 파이프라인을 사용할 때에 비해 파이프라인 위험을 피하기가 더 까다로워 고도의 설계 필요.

비순차적 명령어 처리 OoOE; Out-of-Order Excution

명령어를 순차적으로 실행하지 않는 기법.

데이터 위험 등의 이유로 다음 명령어를 실행하지 못할 때

이후 명령어 중 해당 명령어 및 사이의 명령어들과 데이터 의존성을 가지지 않은 명령어를 먼저 실행.

이전 명령어의 실행을 기다리며 파이프라인이 멈춰있는 시간을 최소화하기 위한 기법이다.

어떤 명령어들이 서로 데이터 의존성을 가지고 있는지, 순서를 바꿔 실행할 수 있는지 판단 필요.

더 알아보기

CISC와 RISC

명령어는 기본적으로 연산 코드와 오퍼랜드로 구성되어 있지만

구체적인 구조, 사용 가능한 연산, 주소 지정 방식 등은 CPU마다 차이가 있다.

CPU가 이해할 수 있는 명령어들의 모음을

명령어 집합 instruction set 또는 명령어 집합 구조 ISA; Instruction Set Architecture 라고 하는데,

CPU마다 ISA가 다를 수 있는 것이다.

ISA가 다른 CPU끼리는 어셈블리어가 다르며 서로의 명령어를 이해할 수 없다.

ISA가 다르면 언어가 다를 때 문화가 다른 것처럼

제어장치가 명령어를 해석하는 방식, 사용되는 레지스터 종류 및 개수, 메모리 관리 방법 등

부차적으로 달라지는 요소들이 있다.

현대 ISA의 양대 산맥인 CISC와 RISC에 대해 알아보도록 하자.

CISC

Complex Istruction Set Computer의 약자로,

"복잡한 명령어 집합을 활용하는 컴퓨터"를 의미한다.

대표적인 CISC 기반의 ISA로는 x86, x86-64가 있다.

복잡하고 다양한 수의 가변 길이 명령어 집합을 사용한다.

메모리에 접근하는 주소 지정 방식도 다양하며, 특별한 상황에서만 사용되는 방식도 있다.

다양하고 강력한 명령어를 활용하는 만큼 하나의 명령어가 구체적인 무언가를 지시하여

적은 수의 명령어로도 하고자 하는 것을 작동시킬 수 있다.

또한 메모리 공간을 절약할 수 있어 메모리를 최대한 아끼며 개발해야 하던 시절에 인기가 높았다.

다만, 그 복잡성 때문에 명령어의 크기 및 수행 시간이 일정하지 않으며

한 단계 내에서 여러 클럭 주기를 필요로 하는 경우도 있다.

이러한 비규격화로 인해 명령어 파이프라인을 구현하기 난해하다.

복잡하고 다양한 명령어를 지원하는 것에 비해

자주 쓰이는 20%의 명령어가 전체 명령어의 80%가량을 차지한다.

RISC

Reduced Instruction Set Computer의 약자로,

CISC의 한계로부터 얻은 교훈을 기반으로 만들어졌다.

- 원활한 파이프라이닝을 위해 명령어 길이 및 수행 시간이 짧고 규격화되어 있어야 한다.

- 어차피 자주 쓰이는 명령어만 줄곧 사용하니 자주 쓰이는 명령어를 작고 빠르게 만드는 것이 중요하다.

RISC는 CISC에 비해 명령어 종류가 적으며,

짧고 규격화된 명령어, 되도록 1클럭 내외로 실행되는 명령어를 지향한다.

그리하여 규격화된 적은 수의 고정 길이 명령어 집합을 사용한다.

대표적인 RISC 기반의 ISA로는 ARM이 있다.

파이프라이닝에 최적화되도록 구현하였으며,

메모리에 직접 접근하는 명령어가 load, store 두 가지로 제한되는 만큼

메모리 접근을 단순화하고 최소화를 추구한다.

메모리 접근보다 레지스터를 적극 활용하여 레지스터를 이용하는 연산이 많고

그만큼 범용 레지스터의 개수도 많은 편이다.

구체적인 명령을 위해 지시해주어야 하는 것이 상대적으로 많아

필요한 동작을 하기 위해 CISC에 비해 많은 양의 명령어를 사용한다.

더 알아보기

미션 수행하기

이번 주 미션

- 기본 미션 | p. 125의 확인 문제 2번, p. 155의 확인 문제 4번 풀고 인증하기

- 선택 미션 | Ch.05(05-1) 코어와 스레드, 멀티 코어와 멀티 스레드의 개념을 정리하기

기본 미션

미션은 P.125의 2번 문제와 P.155의 4번 문제뿐이지만, 이왕 학습하고 확인 문제를 푸는 거 다 풀어보자.

P.110~111 [04-1 | ALU와 제어장치] 확인 문제

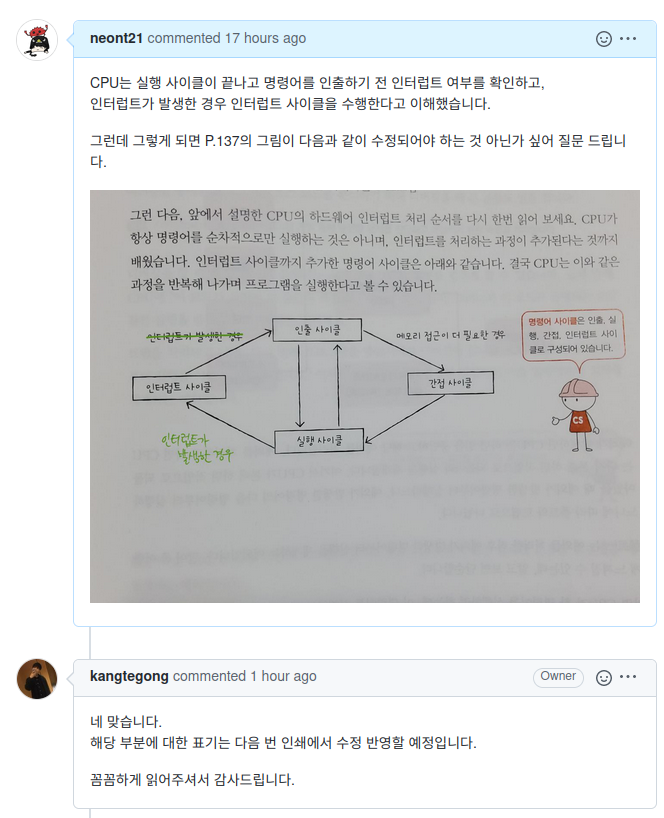

- 아래와 같은 플래그 레지스터를 가진 CPU가 있다고 가정해봅시다. 이 CPU의 ALU가 연산한 결과가 다음과 같을 때 계산 결과를 십진수로 말해보세요.

-3

- 다음 중 제어장치와 관련도니 설명 중 옳지 않은 것을 고르세요.

① 제어장치는 제어 버스로 제어 신호를 내보냅니다.

② 제어장치는 제어 신호를 통해 ALU에게 연산을 지시합니다.

③ 제어장치는 클럭 신호를 받아들입니다.

④ 제어장치는 CPU 내에서 산술 연산과 논리 연산을 담당하는 부분입니다. → 그건 ALU에 대한 설명.

- 아래 그림에서 ①, ②, ③에 들어갈 알맞은 단어를 채워 보세요.

① 플래그 레지스터

② 명령어 레지스터

③ 제어 버스

- CPU의 구성 요소로 적절하지 않은 것을 고르시오.

① ALU

② 레지스터

③ 제어장치

④ 하드 디스크 → 이건 주변 장치.

P.124~125 [04-2 | 레지스터] 확인 문제

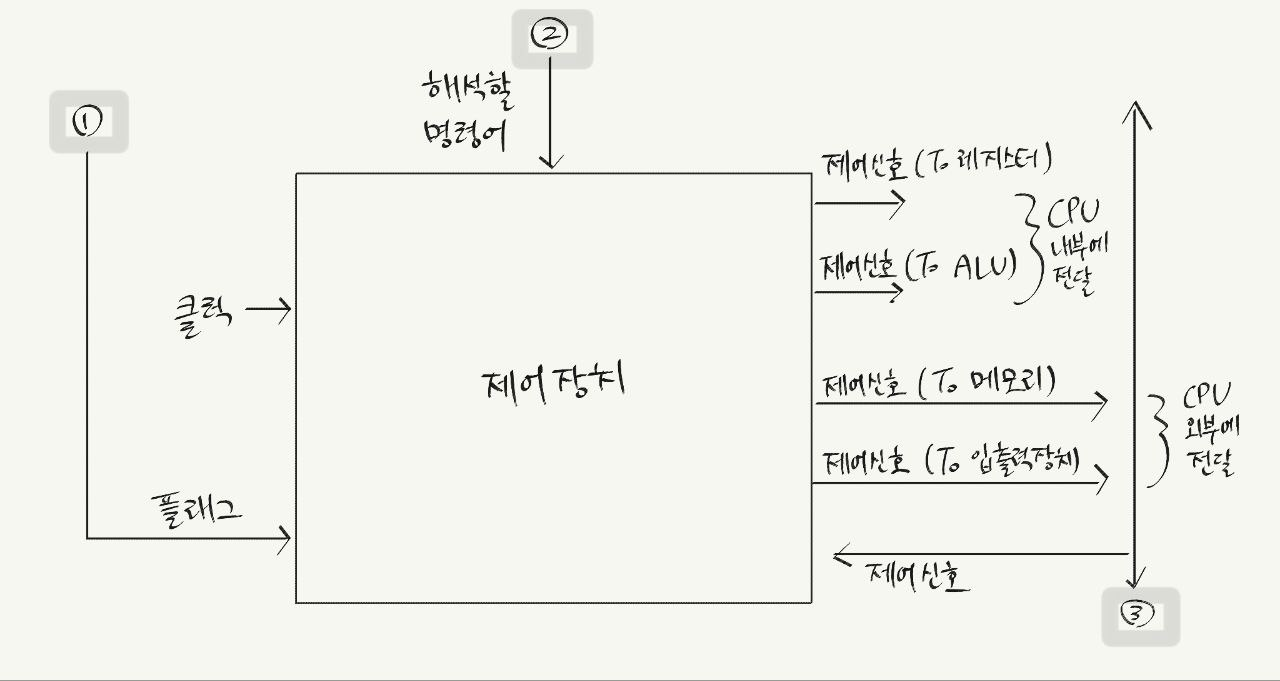

- 현재 프로그램 카운터에 저장된 값이 아래와 같을 때 CPU가 다음으로 읽어 들일 메모리 주소는 몇 번지일까요?

프로그램 카운터는 다음에 실행할 명령어의 주소를 가지고 있으므로 2100번지.

- 설명에 맞는 레지스터를 보기에서 찾아 빈칸을 채워 보세요.

[보기|프로그램 카운터, 명령어 레지스터, 플래그 레지스터, 범용 레지스터]

- [① 플래그 레지스터 ]: 연산 결과 혹은 CPU 상태에 대한 부가 정보를 저장하는 레지스터

- [② 프로그램 카운터 ]: 메모리에서 가져올 명령어의 주소를 저장하는 레지스터

- [③ 범용 레지스터 ]: 데이터와 주소를 모두 저장할 수 있는 레지스터

- [④ 명령어 레지스터 ]: 해석할 명령어를 저장하는 레지스터

(요것이 이번주 기본 미션!!)

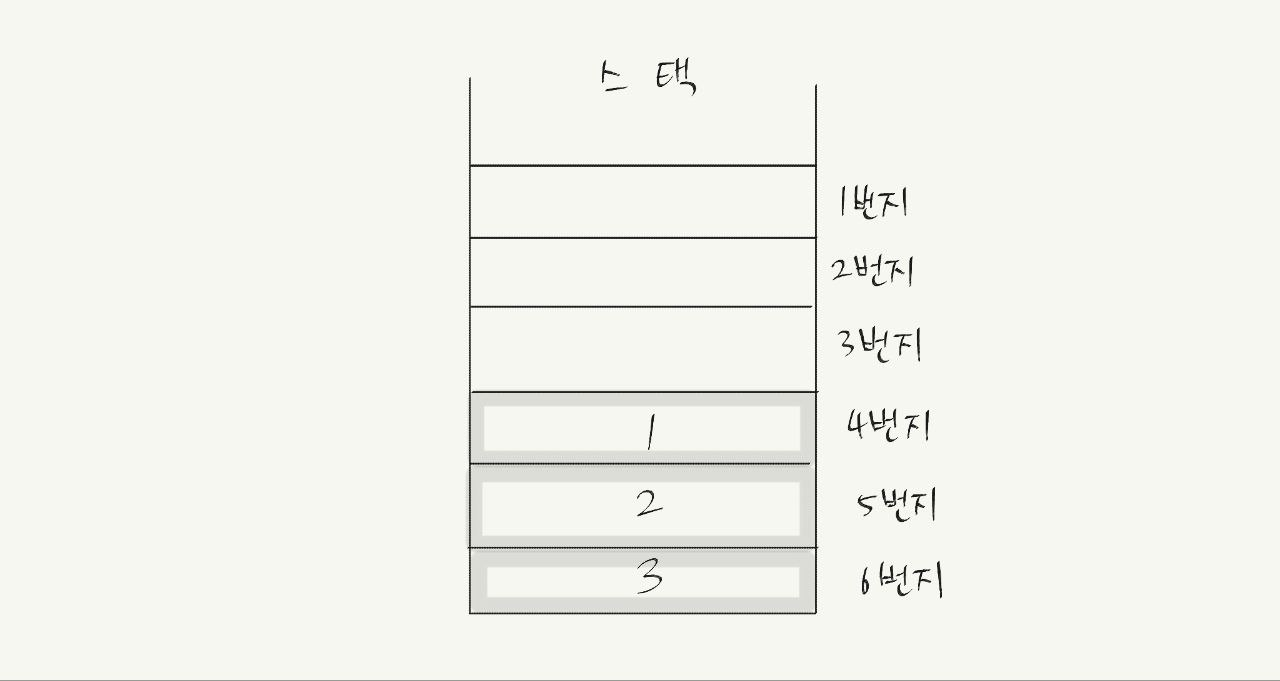

- 현재 아래와 같은 스택을 가리키는 스택 포인터가 있다고 가정해 봅시다. 이 스택에서 데이터를 두 번 빼내게 되었을 때 스택 포인터에 저장되는 주소는 몇 번지일까요?

스택 포인터는 스택의 맨 윗부분의 주소를 가지고 있으므로 6번지.

- 레지스터에 대한 설명으로 옳은 것을 고르세요.

① 산술 연산과 논리 연산을 수행하는 부품입니다. → 이건 ALU.

② 제어 신호를 발생시킵니다. → 이건 제어 장치.

③ 명령어를 해석합니다. → 이건 제어 장치.

④ CPU 내에 있는 작은 임시 저장 장치입니다.

P.140~141 [04-3 | 명령어 사이클과 인터럽트] 확인 문제

- 명령어 사이클에 대한 설명으로 옳지 않은 것을 고르세요.

① 명령어 사이클은 인출, 간접, 실행, 인터럽트 사이클로 구성됩니다.

② 인출 사이클은 메모리에서 실행할 명령어를 CPU로 가져오는 과정을 의미합니다.

③ 간접 사이클은 피연산자의 실제 주소를 찾기 위해 메모리 내의 데이터를 한 번 더 인출하는 과정을 의미합니다.

④ 인터럽트 사이클은 프로그램의 순차적인 흐름을 이어 나가게 합니다. → 순차적인 흐름을 벗어나게 한다.

- 인터럽트에 대한 설명으로 옳지 않은 것을 고르세요.

① 인터럽트는 프로그램의 정상적인 실행 흐름을 방해하는 기능입니다.

② CPU는 입출력 작업 도중에도 명령어를 효율적으로 처리하기 위해 하드웨어 인터럽트를 사용할 수 있습니다.

③ 모든 인터럽트는 인터럽트 비트를 설정함으로써 막을 수 있습니다. → 막을 수 없는 인터럽트도 존재한다.

④ CPU는 인터럽트를 처리하기 위해 인터럽트 서비스 루틴을 수행합니다.

- 다음 빈칸에 알맞은 말을 〈보기〉에서 찾아 써 보세요.

[보기| 인터럽트 서비스 루틴, 인터럽트 벡터, 인터럽트 요청 신호]

"CPU는 인터럽트를 처리하기 위해 하던 작업을 잠시 백업한 뒤 [ 인터럽트 서비스 루틴 ]라는 프로그램을 실행합니다."

- 명령어 사이클에서 인출 사이클에 대한 설명으로 옳은 것을 고르세요.

① CPU가 명령어를 실행하는 단계입니다. → 이건 실행 사이클.

② CPU가 명령어를 메모리로부터 가져오는 단계입니다.

③ 예기치 못한 상황에 대처하는 단계입니다. → 이건 인터럽트 사이클.

④ CPU가 작동을 멈추는 단계입니다. → 이건 인터럽트 사이클.

- CPU가 프로그램을 실행하던 도중 하드웨어 인터럽트가 발생했습니다. 이때 CPU가 수행할 동작으로 올바른 것을 고르세요(프래그 레지스터 속 인터럽트 비트는 활성화되어 있다고 가정하겠습니다).

① 프로그램을 종료합니다.

② 인터럽트를 처리하기 전에 실행하던 프로그램을 마저 실행합니다.

③ 수행하던 작업을 잠시 백업한 뒤 인터럽트 서비스 루틴을 실행하고 다시 수행하던 작업으로 되돌아옵니다.

④ 보조기억장치에 저장된 정보를 초기화합니다.

P.154~155 [05-1 | 빠른 CPU를 위한 설계 기법] 확인 문제

- 클럭에 대한 설명 중 옳지 않은 것을 고르세요.

① CPU는 클럭 신호에 맞춰 작동합니다.

② 클럭 신호는 CPU의 속도 단위입니다.

③ 클럭 신호를 높여도 컴퓨터 부품은 발열 없이 빠르게 작동합니다. → 빠르게 작동하지만 발열이 있다.

④ 클럭 신호는 항상 일정하게 유지되지 않습니다.

- 멀티코어와 멀티스레드에 대한 설명 중 옳지 않은 것을 고르세요.

① 코어는 명령어를 인출하고 해석하고 실행하는 부품의 집합입니다.

② 스레드는 코어가 처리할 수 있는 작업 단위입니다.

③ 여러 개의 스레드를 처리할 수 있다면 하나의 프로그램을 동시에 처리할 수 있습니다.

④ 하나의 코어는 하나의 스레드만 처리할 수 있습니다. → 멀티스레드 프로세서의 경우 여러 개의 스레드를 처리할 수 있다.

- 스레드와 관련한 설명으로 보기에서 알맞은 말을 찾아 써 넣으세요.

[보기| 소프트웨어, 하드웨어, 시스템 버스]

"스레드에는 [ⓙ 소프트웨어 ]적 스레드와 [② 하드웨어 ]적 스레드가 있습니다."

- 다음 그림은 멀티코어 CPU를 간략하게 도식화한 그림입니다. 빈칸에 알맞은 용어를 써 넣으세요.

빈 칸에 공통적으로 들어갈 용어는 코어.

(요것이 이번주 기본 미션!!)

P.165 [05-2 | 명령어 병렬 처리 기법] 확인 문제

- 명령어 파이프라이닝에 대한 설명으로 옳지 않은 것을 고르세요.

① 명령어 파이프라이닝은 명령어를 병렬적으로 처리하는 기법입니다.

② 슈퍼스칼라는 단일한 명령어 파이프라인을 이용하여 명령어를 처리하는 기법입니다. → 여러 개의 파이프라인 이용!

③ 제어 위험은 프로그램 카운터의 갑작스러운 변화에 의해 발생합니다.

④ 데이터 위험은 명령어 간의 데이터 의존성에 의해 발생합니다.

- 다음 보기를 바탕으로 올바른 정의를 짝지으세요.

[보기|슈퍼스칼라, 비순차적 명령어 처리]

- [① 비순차적 명령어 처리 ]: 순서를 바꾸어 명령어를 실행하는 기법

- [② 슈퍼스칼라 ]: 여러 개의 파이프라인을 이용하여 명령어를 동시에 처리하는 기법

P.175 [05-3 | CISC와 RISC] 확인 문제

- CISC에 대한 설명 중 올바르지 않은 것을 고르세요.

① 명령어의 규격화가 어렵습니다.

② RISC보다 다양하고 강력한 기능을 가진 명령어들이 있습니다.

③ 적은 수의 명령어로 프로그램을 수행합니다.

④ 일반적으로 명령어 주소 지정 방식의 종류가 적습니다. → 다양한 명령어 주소 지정 방식!

- RISC에 대한 설명 중 올바르지 않은 것을 고르세요.

① CISC보다 프로그램을 실행하는 명령어 수가 적습니다. → 명령어 다양성이 낮아 더 많은 명령어 필요.

② CISC보다 다양한 메모리 접근 방식이 있습니다. → RISC의 메모리 접근 방식은 읽기/쓰기로 제한적.

③ CISC보다 파이프라이닝에 유리합니다.

④ CISC보다 명령어의 크기가 규격화되어 있습니다.

선택 미션

코어와 멀티 코어

코어는 CPU 내에서 "명령어를 실행하는 부품"이다.

[ ALU + 제어장치 + 개의 레지스터 ] 의 묶음으로 구성된다.

전통적인 CPU 관점에서는 CPU에 하나의 코어만 존재하여 코어와 CPU의 구분이 없었으나

기술의 발전으로 코어를 여러 개 포함하고 있는 CPU가 만들어지며 코어라는 개념이 새로 자리잡았다.

이 때, "코어를 여러 개 포함하고 있는" 것을 멀티 코어라고 하며,

그러한 CPU를 멀티코어 CPU 혹은 멀티코어 프로세서라고 한다.

코어의 개수에 따라 두 개면 듀얼코어, 네 개면 쿼드토어, ...와 같이 표현하기도 한다.

멀티 코어를 이용할 땐 효율적인 실행을 위해 각 코어에 업무가 균등하게 분배될 수 있도록 하는 게 중요하다.

스레드와 멀티 스레드

스레드는 "하나의 코어가 동시에 처리하는 명령어 단위"이다.

하나의 명령어를 실행하기 위해 꼭 필요한 레지스터를 중복하여 제작하면

하나의 코어 내에서 여러 개의 스레드를 실행할 수 있게 되는데

이와 같이 "하나의 코어 내에서 여러 개의 스레드를 실행하는" 것을 멀티 스레드라고 하며,

그러한 CPU를 멀티스레드 CPU 혹은 멀티스레드 프로세서라고 한다.

두 개의 스레드를 실행할 수 있는 코어 네 개를 가지고 있다면 4코어 8스레드 CPU와 같이 표현하기도 한다.

스레드는 프로그램 관점에서 보기엔 개별 CPU처럼 보여 "논리 프로세서"라고도 불린다.

여담

도식이 이상해서 질문드렸더니 다음 인쇄 때 수정하신다고 답변 받았다.