Verilog 문법 및 간단한 모듈 작성법에 대해 글을 쓰기로 하였다.

개발 환경은 아래와 같다.

- Windows 10 x64

- Icarus Verilog v12.0 (iverilog)

- GTKWave Analyzer v3.3.108 (gtkwave)

1. Icarus Verilog & GTK Wave 설치 방법

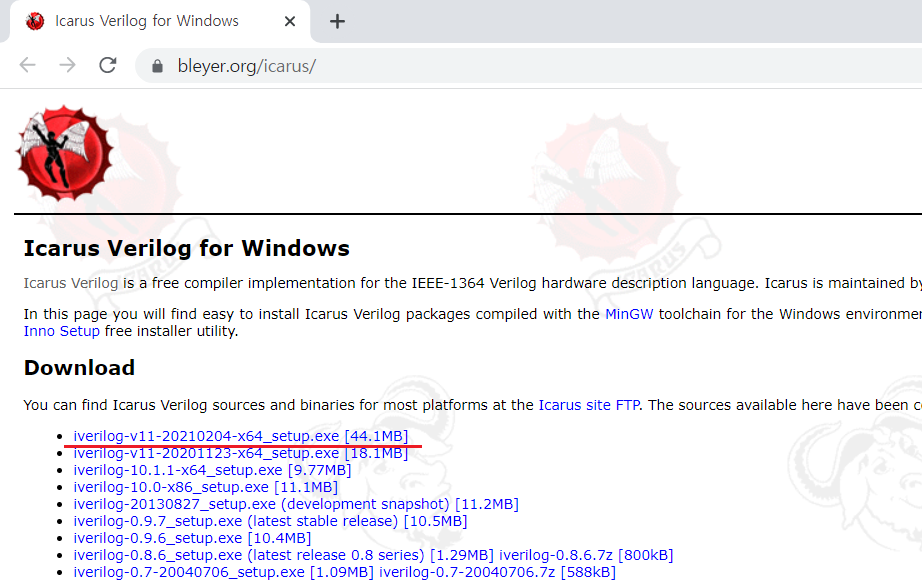

Icarus Verilog 다운로드 페이지에 들어간다.

https://bleyer.org/icarus/

최신 버전을 다운로드한다.

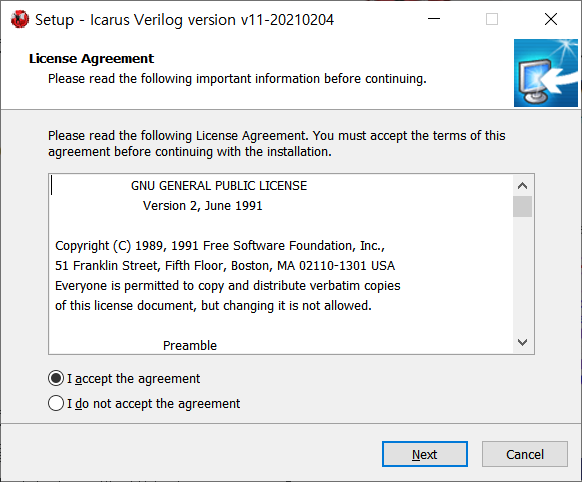

.exe 파일을 내려받아서 실행한다.

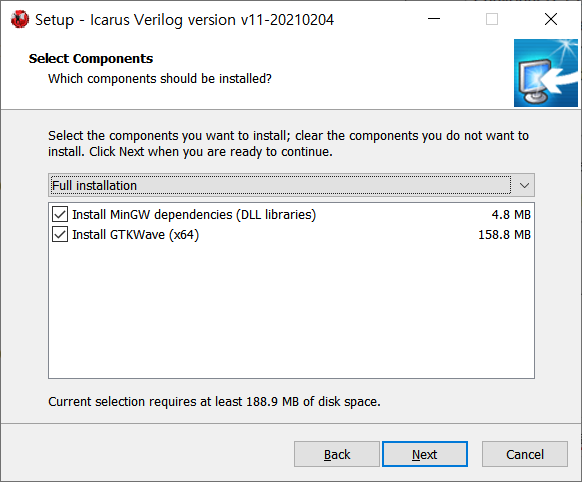

iverilog를 설치하면 자동으로 gtkwave를 같이 설치하도록 되어있어 gtkwave를 따로 설치할 필요가 없다.

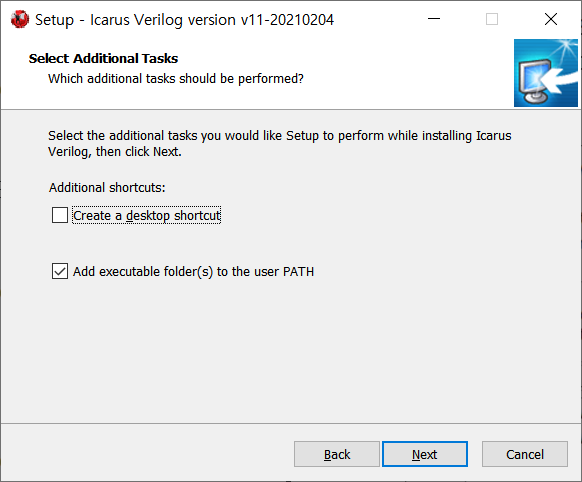

바로 가기는 필요 없고, PATH 환경 변수에 경로가 자동으로 등록된다.

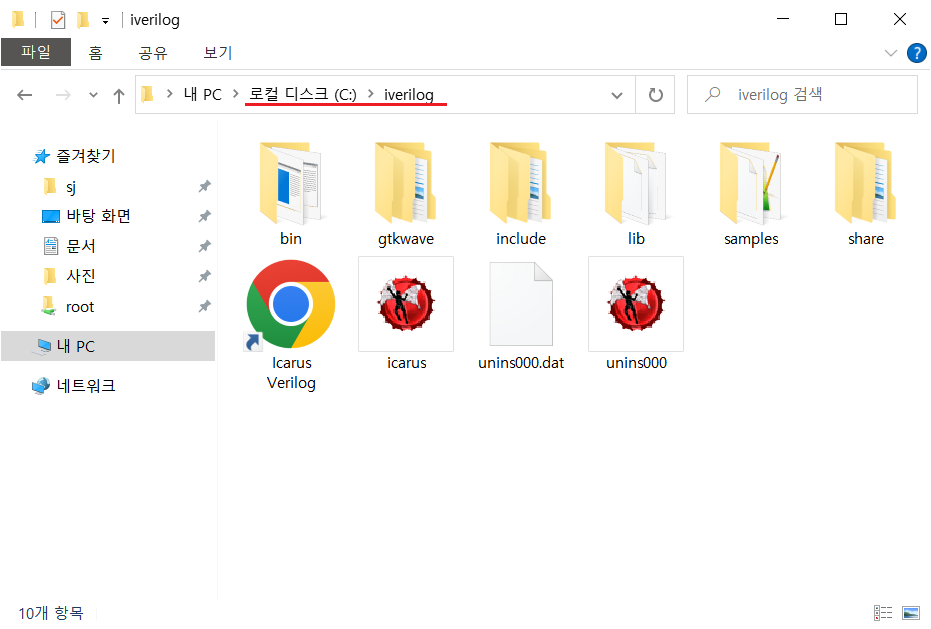

설치를 완료하면 C:\ 경로 밑에 iverilog가 설치되는 것을 볼 수 있다.

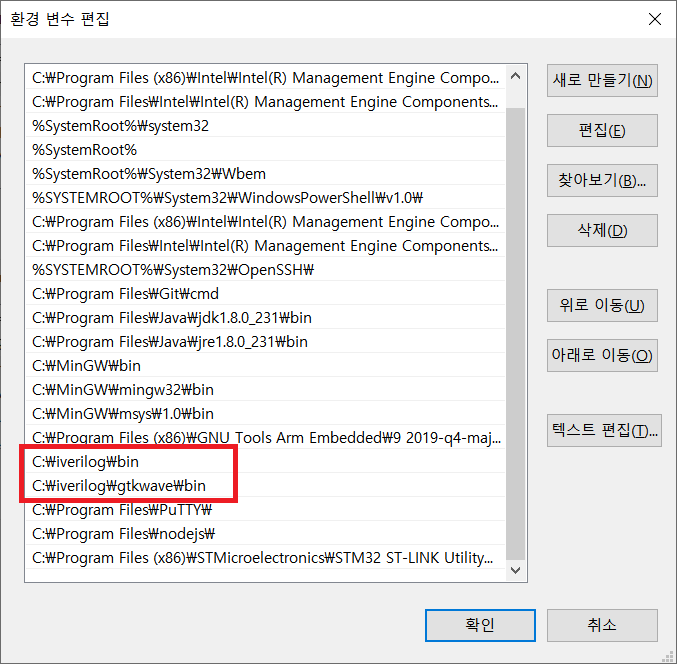

PATH에 iverilog.exe와 gtkwave.exe의 경로가 정상적으로 등록되었는지 확인해보자.

내 PC > 오른쪽 클릭 > 속성 > 고급 시스템 설정 > 고급 > 환경 변수 > 시스템 변수 에 들어가서

"Path"를 더블 클릭하여 맨 아래에 아래 두 경로가 추가되었는지 확인하자.

- C:\iverilog\bin

- C:\iverilog\gtkwave\bin

혹시 추가되어있지 않다면 추가해주자.

2. iverilog + gtkwave 실행 방법

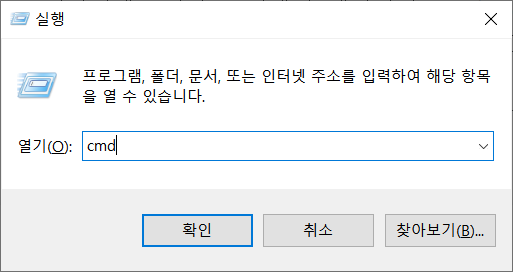

Windows 명령 프롬프트를 실행한다.

Windows 키 + R 누른 후 "cmd" 입력 후 엔터.

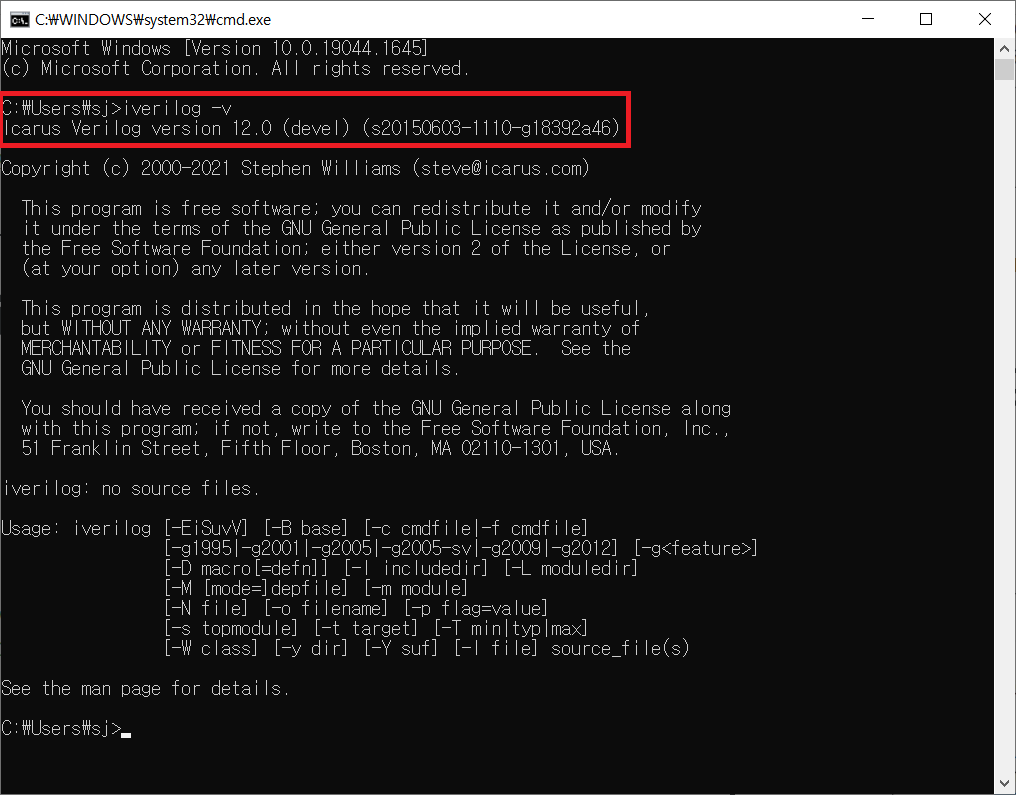

iverilog.exe를 실행해보자

> iverilog -v

버전이 정상적으로 표시되는 것을 볼 수 있다.

※ 만약 "'iverilog'은(는) 내부 또는 외부 명령, 실행할 수 있는 프로그램, 또는 배치 파일이 아닙니다." 라고 뜬다면, 환경 변수 설정이 제대로 안된 것이니 다시 천천히 해보자. 화이팅!

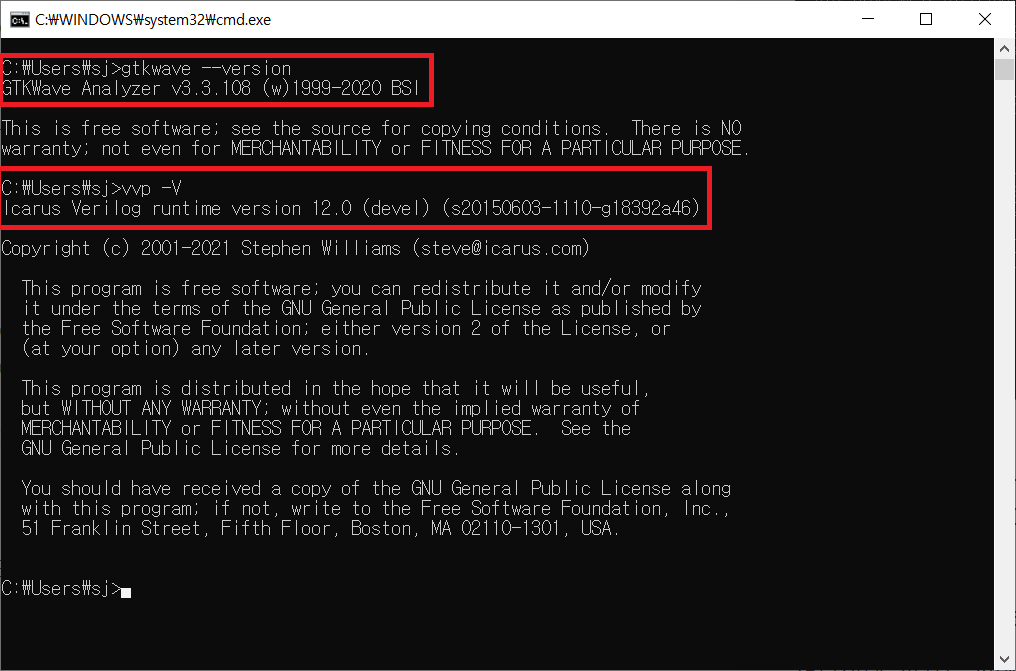

gtkwave.exe도 잘 되는지 실행해보자.

> gtkwave -v

> vvp -V

버전이 정상적으로 표시되는 것을 볼 수 있다.

3. 테스트 실행 (hello world!)

모듈 빌드 및 시뮬레이션 방법을 익히기 위해 아주 간단한 모듈 하나를 만들어보자.

아래와 같이 바탕 화면에 "verilog" 란 폴더를 만들고, 그 아래 모듈과 테스트벤치를 만들어보자.

C:\C:\Users\pikamon\Desktop

└ \verilog

└ test.v

└ testbench.v아주 간단한 AND, OR 회로 하나와 테스트벤치를 만들어보자.

- test.v

`ifndef __TEST_V__

`define __TEST_V__

module test(

// output pins

output wand x,

output wor y,

// input pins

input a, b, c, d, e, f, g, h, i

);

// calculate x

assign x = a;

assign x = b;

assign x = c;

assign x = d;

assign x = e;

assign x = f;

assign x = g;

assign x = h;

assign x = i;

// calculate y

assign y = a;

assign y = b;

assign y = c;

assign y = d;

assign y = e;

assign y = f;

assign y = g;

assign y = h;

assign y = i;

endmodule

`endif /* __TEST_V__ */- testbench.v

`timescale 1ms/1ms

`include "test.v"

module testbench();

reg a, b, c, d, e, f, g, h, i;

wire x, y;

test _test(

.x(x),

.y(y),

.a(a), .b(b), .c(c),

.d(d), .e(e), .f(f),

.g(g), .h(h), .i(i)

);

initial begin

// for simulation

$dumpfile("test.vcd");

$dumpvars(-1, _test);

// initialize

a <= 0; b <= 0; c <= 0;

d <= 0; e <= 0; f <= 0;

g <= 0; h <= 0; i <= 0;

// start

#1 a = 1;

#1 b = 1;

#1 c = 1;

#1 d = 1;

#1 e = 1;

#1 f = 1;

#1 g = 1;

#1 h = 1;

#1 i = 1;

// end

#1

$finish;

end

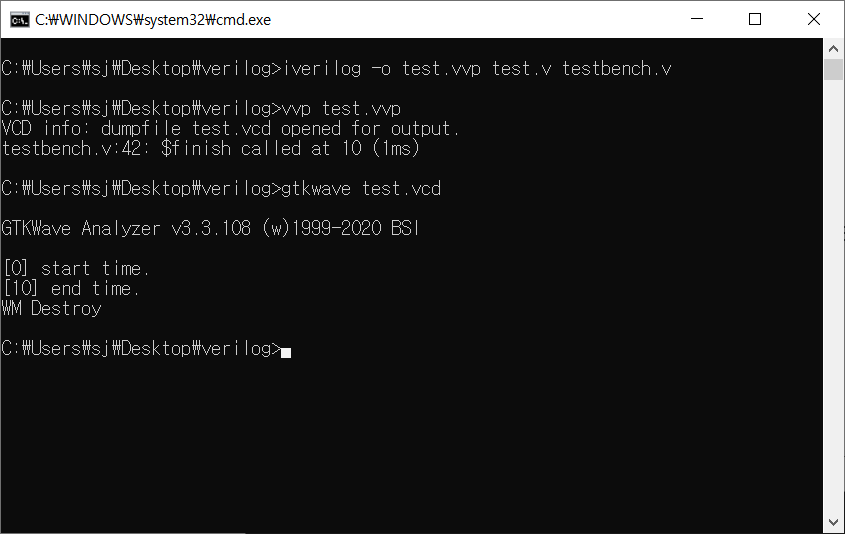

endmodule각각 파일을 저장한 후, verilog 폴더 위에서 쉘을 열어서 아래와 같이 실행한다.

> iverilog -o test.vvp test.v testbench.v

> vvp test.vvp

> gtkwave test.vcd

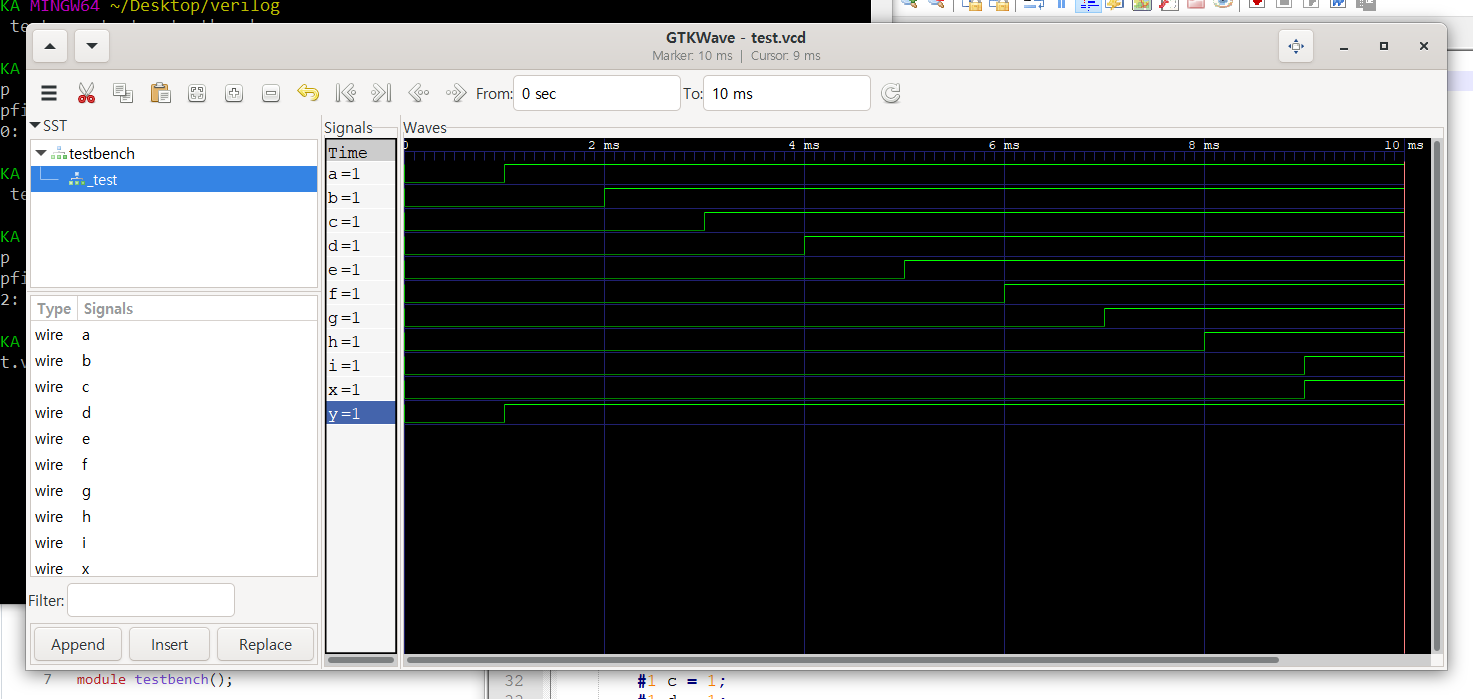

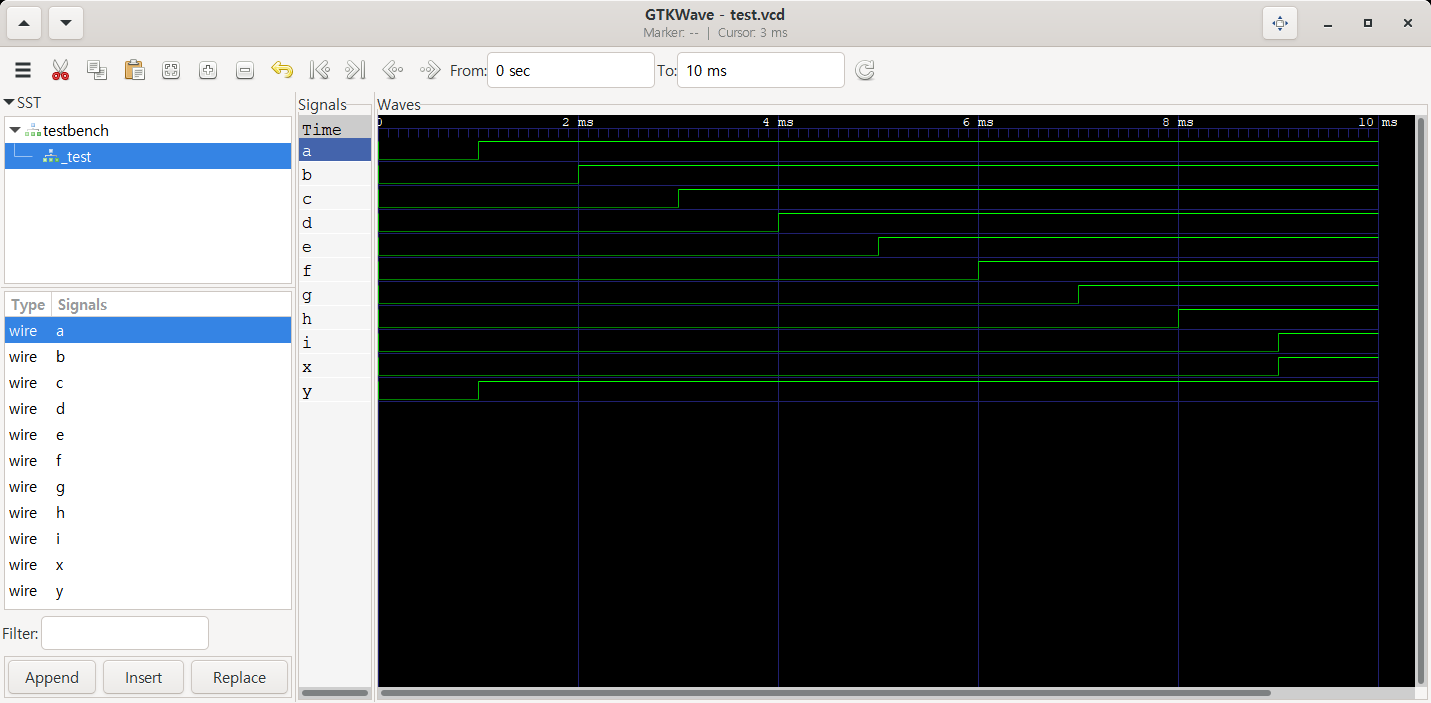

gtkwave 명령어를 입력하면 Gnome 테마의 GUI 창이 하나 뜬다.

왼쪽 상단 testbench 왼쪽에 있는 화살표를 클릭하고, 모든 wire를 드래그한 다음 하단의 "Insert" 버튼을 누른다.

그럼 시각적인 형태의 Waveform을 볼 수 있다.

이미 눈치챘겠지만, x는 모든 값의 논리곱, y는 모든 값의 논리합임을 알 수 있다.

HDL을 처음 접하면 여기까지의 일련의 과정이 매우 헷갈릴 수 있다. (사실 필자 얘기)

여러가지 노하우를 통해 보다 유연한 환경을 만들어가면 좋을 것 같다.

혹시 iverlog를 사용하면 system verilog도 컴파일이 가능할까요?