1. 설명

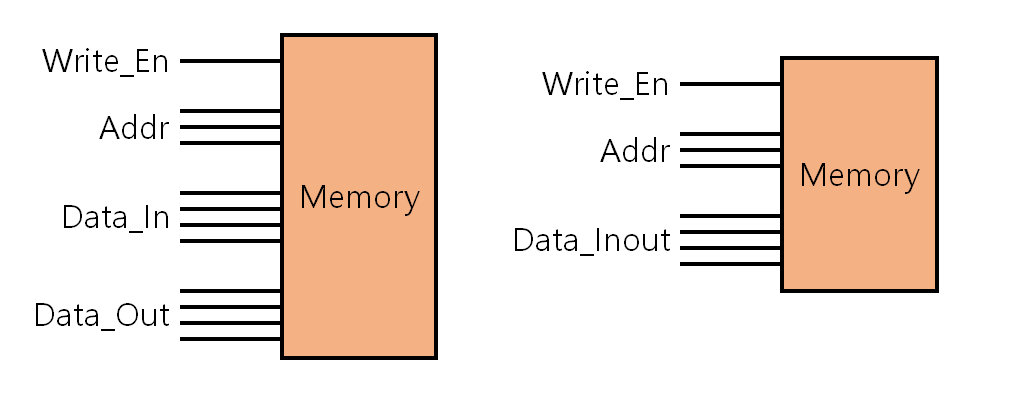

메모리를 그림으로 간단히 그려보았다.

Inout 핀을 사용하는 이유는 대개 핀 개수를 줄이기 위해서이다. 대부분의 통신 프로토콜들은 Input 핀과 Output 핀을 전용으로 나누지만, 일부 프로토콜에서는 Inout 핀을 사용하기도 한다.

Inout 핀으로도 통신 프로토콜의 안정성을 보장할 수 있다면, 이를 통해 핀의 개수를 절약할 수 있으며, 패키지 사이즈도 줄어 생산 단가를 줄일 수 있다.

2. 예제

다음의 메모리 예제를 통해 자세히 알아보자.

데이터 라인을 Inout으로 구현하였으며, 시나리오는 아래와 같다.

- w_en = 1 : data_io = High Impedance.

- w_en = 0 : data_io = (value of memory).

- memory_io.v

`ifndef __MEMORY_IO__

`define __MEMORY_IO__

module memory_io(

input w_en,

input [3:0] addr,

inout [7:0] data_io

);

reg [7:0] memory[0:15];

// 메모리의 값을 아래와 같이 초기화함.

initial begin

memory[0] <= 8'h1; memory[4] <= 8'h10;

memory[1] <= 8'h2; memory[5] <= 8'h20;

memory[2] <= 8'h4; memory[6] <= 8'h40;

memory[3] <= 8'h8; memory[7] <= 8'h80;

end

// write enable 시 data_io 핀이 input으로 사용됨.

always @ (*) begin

if (w_en)

memory[addr] <= data_io;

end

// write disable 시 data_io 핀이 output으로 사용됨.

assign data_io = !w_en ? memory[addr] : 8'bz;

endmodule

`endif /*__MEMORY_IO__*/- tb_memory_io.v

`timescale 1ms/1ms

`include "memory_io.v"

module tb_memory_io();

reg w_en;

reg [3:0] addr;

wire [7:0] data_io;

reg [7:0] data_in;

memory_io _memory_io(

.w_en(w_en),

.addr(addr),

.data_io(data_io)

);

assign data_io = w_en ? data_in : 8'bz;

initial begin

// for simulation

$dumpfile("test.vcd");

$dumpvars(-1, _memory_io);

// initialize

w_en <= 1'b0;

addr <= 4'h0;

// start

// 메모리를 7번지부터 0번지까지 거꾸로 읽음.

#1 addr <= 4'h7;

#1 addr <= 4'h6;

#1 addr <= 4'h5;

#1 addr <= 4'h4;

#1 addr <= 4'h3;

#1 addr <= 4'h2;

#1 addr <= 4'h1;

#1 addr <= 4'h0;

// 0~7번지의 값을 0xFF로 채움.

#1 w_en <= 1'b1;

#1 addr <= 4'h7; data_in <= 8'hFF;

#1 addr <= 4'h6; data_in <= 8'hFF;

#1 addr <= 4'h5; data_in <= 8'hFF;

#1 addr <= 4'h4; data_in <= 8'hFF;

#1 addr <= 4'h3; data_in <= 8'hFF;

#1 addr <= 4'h2; data_in <= 8'hFF;

#1 addr <= 4'h1; data_in <= 8'hFF;

#1 addr <= 4'h0; data_in <= 8'hFF;

// 값이 정상적으로 써졌는지 확인.

#1 w_en <= 1'b0;

#1 addr <= 4'h7;

#1 addr <= 4'h6;

#1 addr <= 4'h5;

#1 addr <= 4'h4;

#1 addr <= 4'h3;

#1 addr <= 4'h2;

#1 addr <= 4'h1;

#1 addr <= 4'h0;

// end

#1 $finish;

end

endmodule- 실행

> iverilog -o test.vvp memory_io.v tb_memory_io.v

> vvp test.vvp

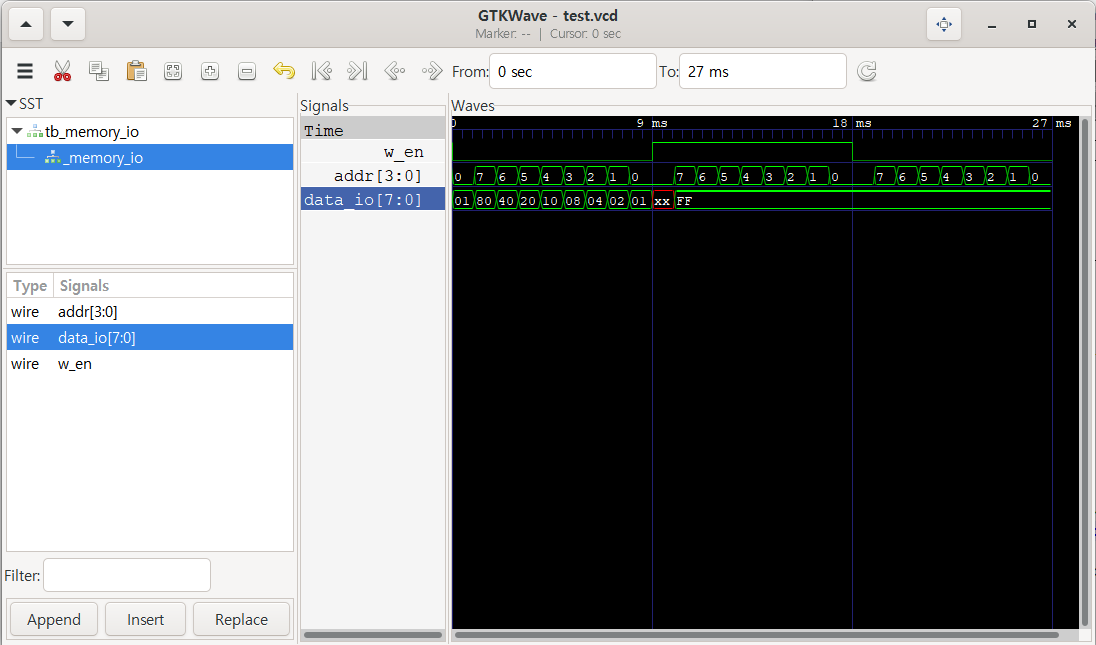

> gtkwave test.vcd- 파형 결과

메모리에 들어있는 초기값이 data_io 핀으로 정상 출력됨을 볼 수 있으며,

data_io 핀으로 설정한 값이 메모리에 정상 입력됨을 볼 수 있다.