어제 처음 ChatGPT를 써봤는데, 얘가 프로그래밍 소스 코드를 생성해준다...

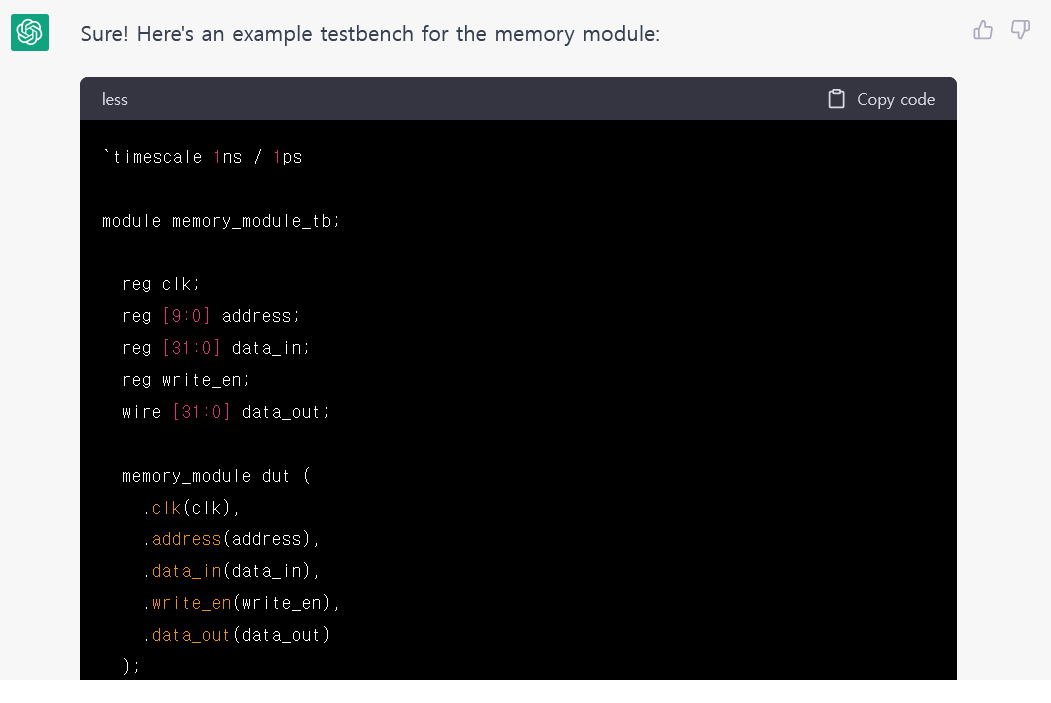

Verilog 할 줄 아냐고 물어봤는데 "Sure!" 라고 하길래, 32-bit 1KB 짜리 메모리 모듈 만들어달라고 하니까 얘가 실제로 만들어줬다.. 심지어 testbench도 만들어달라고 했더니 만들어줬다... (경악)

1. 32-bit 1KB 메모리 모듈

ChatGPT가 만들어준 메모리 모듈은 아래와 같았다.

module memory_module(

input clk,

input [9:0] address,

input [31:0] data_in,

input write_en,

output reg [31:0] data_out

);

reg [31:0] mem [1023:0];

always @(posedge clk) begin

if (write_en) begin

mem[address] <= data_in;

end

end

assign data_out = mem[address];

endmodule테스트벤치는 아래와 같았다.

`timescale 1ns / 1ps

module memory_module_tb;

reg clk;

reg [9:0] address;

reg [31:0] data_in;

reg write_en;

wire [31:0] data_out;

memory_module dut (

.clk(clk),

.address(address),

.data_in(data_in),

.write_en(write_en),

.data_out(data_out)

);

initial begin

clk = 0;

forever #5 clk = ~clk;

end

initial begin

write_en = 0;

address = 0;

data_in = 0;

#100;

write_en = 1;

data_in = 8'hCAFE;

address = 10'h200;

#100;

write_en = 0;

address = 10'h200;

#100;

$display("data_out: %h", data_out);

$finish;

end

endmodule대충 0x200번지에 0xCAFE 라는 값을 쓰고 100ns 후에 다시 읽어보는 코드이다.

2. 빌드 결과

실제로 로컬에서 컴파일해보니 에러가 있다고 나왔다.

PS C:\Users\sj\Desktop\memory> iverilog memory_module_tb.v memory_module.v

memory_module_tb.v:30: warning: extra digits given for sized hex constant.

memory_module_tb.v:30: warning: Numeric constant truncated to 8 bits.

memory_module.v:22: error: reg data_out; cannot be driven by primitives or continuous assignment.

1 error(s) during elaboration.내용은 대충 아래와 같다.

- 모듈 코드에서 assign 문으로 reg 타입에 값을 넣으려고 함.

- 테스트벤치 코드에서 16비트 상수 앞에 8'h를 붙임.

그래서 수동으로 에러를 해결해주는 작업이 필요했다.

3. 실행 결과

수정하여 실행한 결과는 아래와 같다.

PS C:\Users\sj\Desktop\memory> iverilog memory_module_tb.v memory_module.v

PS C:\Users\sj\Desktop\memory> vvp a.out

data_out: 0000cafe

memory_module_tb.v:37: $finish called at 300000 (1ps)0xCAFE가 출력된 후 300ns만에 종료된 것을 볼 수 있다.

사소한 버그를 제외하면 실행 결과는 꽤 괜찮았다.

4. 코드 재생성

내가 너가 짠 코드 틀린 것 같다고 말해주니까, 미안하다면서 수정한 코드를 생성해줬다.

module memory_module(

input clk,

input [9:0] address,

input [31:0] data_in,

input write_en,

output [31:0] data_out

);

reg [31:0] mem [1023:0];

always @(posedge clk) begin

if (write_en) begin

mem[address] <= data_in;

end

end

always @* begin

data_out = mem[address];

end

endmodule기특해서 좋긴 한데, 또 틀린 코드를 만들어줬다. assign이랑 output reg 중에 하나만 수정했어야 하는데 둘 다 고쳐서 또 똑같은 문제가 나왔다.

그래서 둘 중 하나만 고쳐야 한다고 말해주니까, 미안하다면서 수정한 코드를 생성해줬다.

module memory_module(

input clk,

input [9:0] address,

input [31:0] data_in,

input write_en,

output reg [31:0] data_out

);

reg [31:0] mem [1023:0];

always @(posedge clk) begin

if (write_en) begin

mem[address] <= data_in;

end

end

assign data_out = mem[address];

endmodule보면 알겠지만, 또또 틀린 코드를 내게 생성해줬다. 내가 분명 either 라고 했는데 아오...

또또 말해줘봤자 또또또 무한 루프일 것 같아서 포기했다.

5. 결론

코드를 아주 잘 짜는 것처럼 보이지만, 자세히 보면 군데군데 버그가 있는 것 같다. 인간의 실수까지도 학습한 건지...

목업 코드를 잘 짜는 건 사실이라, AI랑 개발자랑 코드를 같이 짜면 좋은 시너지가 나오지 않을까 싶었다.