4.1 Introduction

CPU Performance는 CPI와 Cycle time이 결정한다.

- CPI - ISA와 Compiler가 영향

- Cycle time - CPU HW의 성능

MIPS Processor중 간단한 버전과 실질적인 pipeline을 사용하는 버전을 배울것이다.

Instruction은 9가지를 다룬다.

The memory-reference instructions - lw, sw

The arithmetic-logical instructions - add sub AND OR slt

Control - transfer beq j

ISA가 Implementation의 여러 가지 요소를 어떻게 결정하는지, 또 여러 가지 implementation 전략이 클럭 속도와 CPI에 어떻게 영향을 미치는지 알아본다.

모든 명령어의 첫 두 단계

- PC를 프로그램이 저장되어 있는 메모리에 보내서 메모리로 부터 명령어를 가져온다.

- 읽을 레지스터를 선택하는 명령어 필드를 사용하여 하나 또는 2개의 레지스터를 읽는다. 워드 적재 명령어는 레지스터 하나만 읽으면 되지만 대부분의 다른 명령어는 레지스터 2개를 읽는다.

PC(Program Counter) : 다음에 수행할 명령어의 주소를 가리킨다.

instruction fetch 회로가 하는것?

$s, $v, $t 등의 앞 알파벳과 뒤의 숫자로 이루어짐

- 점프 명령어를 제외한 모든 명령어가 레지스터를 읽은 후에는 ALU를 사용한다.

ALU는 명령어에 따라 수행하는 기능이 다르다.

- The memory-reference instructions : address calculation

- The arithmetic-logical instructions : opeation execution

- branches : comparison

ALU사용 후 행동

- The memory-reference instructions : 메모리에 접근

- Load/save instruction : 데이터 읽기/데이터 기록

- The arithmetic-logical/load instructions : ALU나 메모리에서 온 데이터를 레지스터에 쓴다.

- branches : 비교 결과에 따라서 다음 명령어의 주소를 바꾸거나 PC값을 4 증가시켜 다음 명령어의 주소를 갖게 할 수 있다.

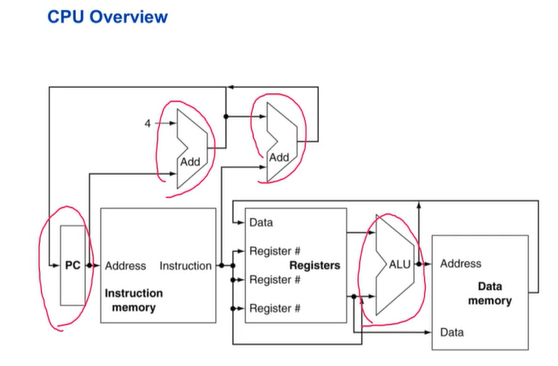

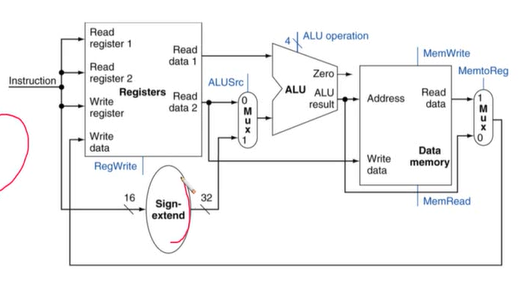

- 그림 1. CPU Overview

교재설명 : 모든 명령어의 실행은 PC에 있는 명령어 주소를 명령어 메모리로 보내는 것으로 시작된다. 명령어를 가져온 후에는 명령어의필드를 보고 명령어가 사용하는 레지스터 피연산자를 알아낸다. 레지스터 피연산자를 읽고, 메모리 주소를 계산하기 위하여(적재나 저장 명령어의 경우), 산술 연산 결과를 구하기 위하여(정수 산술/논리 명령어의 경우), 또는 비교하기 위하여(분기 명령어의 경우) 피연산자에 대한 연산을 수행한다. 산술/논리 명령어이면 ALU 결과를 레지스터에 쓴다. 적재 명령어이면 ALU결과를 주소로 사용하여 메모리에서 레지스터에 적재할 값을 읽고, 저장 명령어이면 레지스터 값을 메모리에 저장한다. ALU결과(산술/논리 명령어의 경우)나 메모리에서 읽은 값(적재 명령어)을 레지스터 파일에 써넣는다. 분기 명령어의 경우는 ALU출력을 사용하여 다음 명령어 주소를결정하게 되는데, 이 주소는 오른쪽 덧셈기에서(PC와 분기 변위가 더해진 값) 나오거나 왼쪽 덧셈기에서(PC+4)가 나온다.그림에서 기능 유닛들을 연결하는 굵은 선은 버스를표시하는데, 버스는 여러개의 신호선들로 이루어진다. 화살표는 정보가 흐르는 방향을 알 수 있도록 하기 위해서 사용하였다. 신호선들이 교차할 수 있기 때문에 교차하는 신호선들이 연결되는 경우에는 점으로 표시하였다.

ADD 두개와 ALU한개를 가지며

instruction memory와 data memory 체크하자.

고칠점

1. 잘 보면 wire가 합쳐지는 부분이 있는데 MUX를 추가해야한다.

2. 어떤 유닛들은 명령어 종류에 따라 다르게 제어되어야 하는데 이 부분이 빠져있다. ex) 레지스터에 READ WRITE 구분하는 INPUT 필요

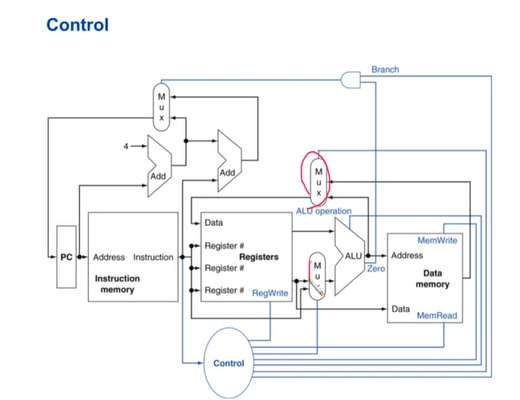

- 그림 2. MUX 추가

교재설명 : 맨 위의 MUX는 어떤 값(PC+4 또는 분기 목적지 주소)이 새 PC값이 될지를 결정한다. 멀티플렉서 자체는 ALU의 Zero 출력과 현재 명령어가 분기 명ㄹㅇ어라는 것을 나타내는 제어선을 AND하는 게이트에 의해 제어된다. 가운데 멀티플렉서는 ALU출력(산술/논리 명령어의 경우)과 데이터 메모리 출력(적재 명령어의 경우)중에서 어느 것을 레지스터 파일에 쓸 것인지를 결정하는 것으로, 그 출력이 레지스터 파일로 연결된다. 아래쪽의 멀티플렉서는 ALU의 두 번째 입력을 레지스터에서(산술/논리 또는 분기 명령어의 경우) 받을 것인지 아니면 명령어의 변위 필드(적재 또는 저장 명령어)에서 받을 것인지를 결정하는 데 사용된다. 나머지 제어선들의 동작은 그림을 보면 쉽게 알 수 있다. ALU가 수행할 연산을 결정하고, 데이터 메모리가 읽기를 할지 쓰기를 할지, 레지스터에 쓰기를 할 것인지 말 것인지를 결정한다. 제어선들은 좀 더 알아보기 쉽게 파란색으로 표시하였다.

control이 생겼다.

각각의 하드웨어 모듈이 어떻게 동작하는지 제어하는 컨트롤해주는 회로

명령어를 읽어서 해당되는 control을 만들어낸다.

명령도 하고 input도 받는다.

4.2 Logic Design

deasserted(low) = 0 asserted(high) = 1

조합회로 순차회로의 차이 알기

- 조합회로 : 정보저장 X, input이 output에 그대로 영향

- 순차회로 : 정보저장 o, input + 현재 상태 = output

ALU는 Y = F(A,B) 즉 어떤 연산을 나타낸다.

순차회로는 CIRCUIT에 정보를 저장하는데 쓰임

즉 input 뿐만 아니라 현재의상태가 출력에 영향

메모리 구현에 사용

clocking methodology

clock이 없이 combinational logic 만으로 회로가 설계될 경우

이전의 값과 현재의 값이 섞일 수 있기 때문에 clock에 동기화 하여 동작하는

sequential logic의 register와 combinational logic을 같이 사용하여 설계한다.

- edge triggered를 많이 사용함.

4.3 datapath

데이터 전달 과정

register, ALU, MUX, memory등이 연결된것을 datapath

모든 요소들을 지칭하는 것 같다.

1. instruction fetch

- 그림 3. fetch

PC에 있는 주소를 Instruction memory에 전달하고 명령어를 실행

주소가 add에서 4가 더해져 다음 명령어를 실행하는 구조

PC는 32-bit register이다.

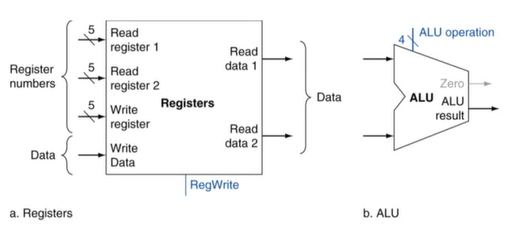

2. R-format instruction

- 그림 4. r-format

register 두개에서 데이터를 읽고 연산논리수행을 함 결과를 다시 register에 준다.

read 두개는 입력

write는 출력과 값

값이 나가면 alu에 input후 다시 돌아온다.

3. load/store instruction

데이터메모리 엑세스해야됨 메모리가있으면 하나는 어드레스 하나는 data가 입력됨

이때 sign extension해야함 load store는 16빗을 32빗으로 바꿔줘야함

offset을 16bit해줌

4 Branch instruction

operand(피연산자)를 read하고 비교하는놈

값을 빼서 0이면 같음 아니면 다름

zero output check

target address 계산

extend 하고 shift left 2 하고 PC + 4

왜 이 과정이 있어야 목표하는 address가 계산됨.

ALU는 zero check로 비교 수행.

datapath 요소들은 한번에 한 function만 한다.

따라서 instruction과 memory를 나눈다.

명령어에따라 data가 달라질때 mux사용

- 그림 5. R-format + load/store

첫 mux는 extention또는 register값

ALU값은 데이터메모리를 바이패싱하거나 addressing 입력이됨

첫번째 register의 값이 바로 data memory로 갈수도 있다.

이 때 마지막 mux는 load명령어와 같이? 선택하는역할

파이프라인가면 회로가 또 바뀐다.

'

'

- 그림 6. +branch 회로

single cycle MIPS 회로

위에 추가된 회로가 branch instruction

Reference

[1] D. Patterson and J. Hennessy, ⌜Computer Organization and Design, 5th Edition⌟ , chapter 4

[2] 최규상 교수님, 컴퓨터구조, 7-1강