4.4 A Simple Implementation Scheme

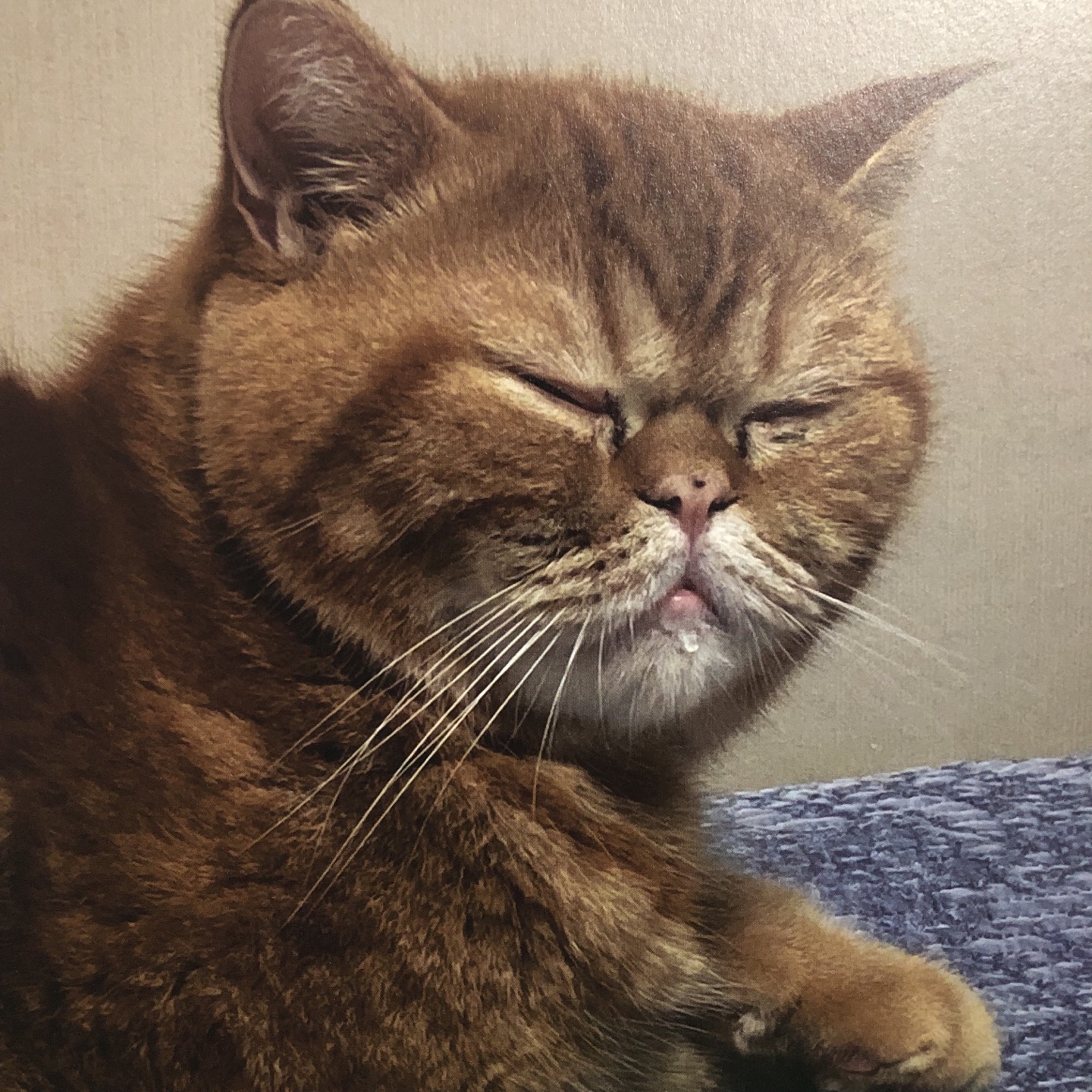

ALU Control

- Load/Store : F = add

- Branch : F = sub

- R-type : F depends on funct field

- 그림 1. ALU control

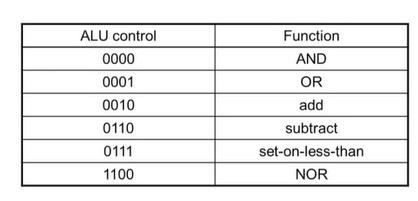

ALUOp라는 걸 opcode로부터 만들어냄 2bit임

- 그림 2. ALUOp

table -> k-map -> ALU control 유도 가능

The Main Control Unit

명령어에 따라 달라지는 32-bit의 영역?

- 그림 3. control unit이 추가된 datapath 회로도

ALUOp의 2bit과 명령어 6bit이 ALU control로 가는것을 확인

각각의 instruction 회로는 다시 체크하기

Implementing Jumps

- Update PC with concatenation of

- Top 4 bits of old PC- 26-bit jump address

- Need an extra control signal decoded from opcode

모르겠다.

Performance Issues

- 가장 긴 delay가 clock period를 결정

- 각각의 명령어마다 다른 clock을 사용할 수 없어 가장 긴 delay기준

- Making the common case fast에 위배

- pipelining 도입

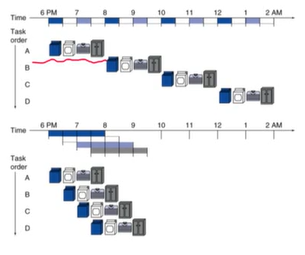

4.5 Pipelining

- 그림 4. 파이프라인 설명

모든 과정을 끝내고 다음이 수행되는것이 아니라 차곡차곡 실행되는것

MIPS Pipeline 중요!

Five stages, one step per stage

- IF : Instruction fetch from memory

- ID : Instruction decode & register read

- EX : Execute operation or calculate address

- MEM : Access memory operand

- WB : Write result back to register

모든 stage가 balanced할 경우 속도향상 정도가 크다.

- latancy가 아닌 throughput에 의해 성능이 향상된다.

- pipelining improves performance by increasing instruction throughput, as opposed to decreasing the execution time of an individual instruction.

32 bit, 적은 명령어 formats등에 의해 MIPS는 Pipeline에 적합

Designing Instruction Sets for Pipelining

- All MIPS instructions are the same length.

- 이 제한된 형태는 명령어를 fetch하고 다음 단계로 전달할하는 것을 더 쉽게 만들어준다.

- All MIPS instructions are the same length.

- MIPS has only a few instruction formats, with the source register fields being located in the same place in each instuction.

- 이 대칭된 형태 덕분에 두 번째 단계에서 register의 파일을 읽을 수 있게되어 pipeling의 단계를 줄일 수 있게 된다.

- MIPS has only a few instruction formats, with the source register fields being located in the same place in each instuction.

- Memory operands only appear in loads or stores in MIPS.

- 모르겠다.

- Memory operands only appear in loads or stores in MIPS.

- operands must be aligned in memory.

- 이해안됨.

- operands must be aligned in memory.

Hazard

- 한 명령어를 수행한 후 다음 클락 사이클 때 다음 명령어를 실행해야 하는데 실행하지 못하는 상황.

- Structure hazard : confilct for use of a resource 때문에 발생, resource를 늘리면 해결

- Data hazard : 실행 될 명령어에 사용될 data가 전 명령어에 의해 제공되는데, 이 data가 clock cycle에 맞게 나오지 않은 경우 발생. forwarding으로 해결할 수 있다.

- forwarding(bypassing) : 값이 계산되고 register에 쓰이기 전에 바로 다음 명령어를 위해 사용될 수 있도록 추가적인 연결을 하는 것.

forwarding은 반드시 다음 명령어중 전 단계로 이어저야 한다.

-- load-use data hazard의 경우에는 forwarding으로도 해결하지 못한다.

- load-use data hazard : lw와 같이 memory read가 실행되어야 data를 사용 가능한 경우 발생?

data hazard는 Read after Write일 때 발생한다. 명령어의 순서를 바꿔 연관되는 명령어들의 거리를 조절하여 해결할 수 있다.

- Control hazard : 다음 명령어가 전 명령어의 결과에 의해 제어되는 경우, Branch명령어와 연관됨. branch prediction으로 해결한다.

- static prediction : taken or not taken

- dynamic prediction : 결과들의 history를 이용하여 예측

pipeline stall/bubble : hazard가 발생할 때 마다 파이프라인을 멈추는것. 1cycle을 멈추면 1 cycle stall이라고 한다.

Reference

[1] D. Patterson and J. Hennessy, ⌜Computer Organization and Design, 5th Edition⌟ , chapter 4

[2] 최규상 교수님, 컴퓨터구조, 7-2강