layout 제작

지난 포스트(https://velog.io/@quesiman/Full-Custom-IC2)에서는 symbol과 schematic을 만들어보았다. 이것을 하는 이유는 개인 라이브러리 구축을 통해 나중에 지금 구현했고 검증한 소자를 이용하여 IC칩을 만들 때 사용하기 위함이다. 이번 포스트에서는 layout, 실제 디자인과 크기를 지정해줌으로써 칩 위의 물성을 구현하는 것에 초점을 두었다.

NOT과 2NAND, 2NOR 게이트의 layout 제작

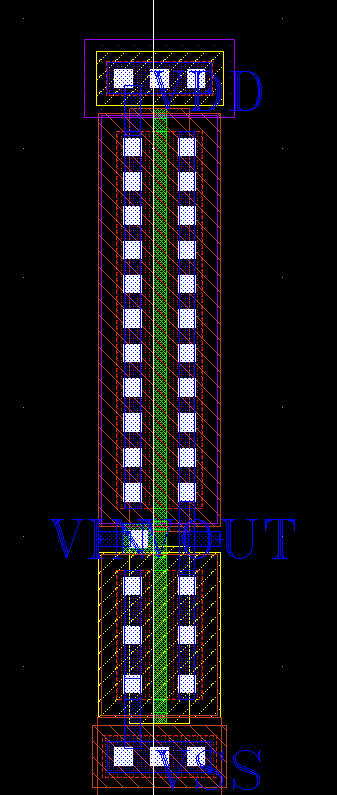

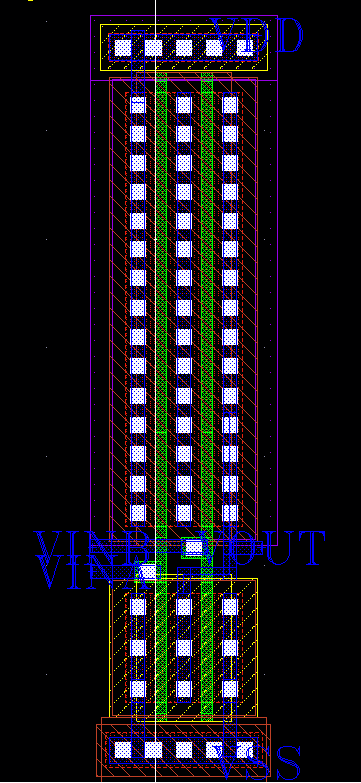

NOT 게이트의 layout. 날씬해보인다.

NOT 게이트의 layout. 날씬해보인다.

2NAND 게이트의 layout. NOT게이트보다는 든든하다.

2NAND 게이트의 layout. NOT게이트보다는 든든하다.

2NOR 게이트의 layout. 점차 커지는 것을 관찰할 수 있다.

2NOR 게이트의 layout. 점차 커지는 것을 관찰할 수 있다.

virtuoso를 사용하여 layout을 제작할 때 가장 주의해야 할 것은 바로 회로의 문제가 아닌, 소자를 제작할 때 가장 작은 크기로 디자인해야한다는 설계자의 역량에 관련한 문제이다.

왜냐하면, 툴에서 전기적/물성적인 설계 실수는 모두 체크가 가능하다. 그러나 설계자가 설계 시 모든 디지털/물성적인 룰을 지키고 120nm로 이격해야 할 것을 더 넉넉하게 거리를 주어 150nm로 이격했다고 가정해보자. 이 경우, 단순히 30nm의 작은 오차로 보이지만 이 소자를 라이브러리로 하여 IC칩을 제작한다면 수많은 게이트들이 사용되는 IC칩에서 누적되어 엄청난 손해를 보게 될 것이기 때문이다. 따라서 IC칩 하나에 막대한 양의 게이트가 들어가므로, 항상 이러한 최적화 문제를 주의하여 최소의 게이트 높이를 찾아 layout 디자인을 진행하여야 한다.