[Computer Architecture] Processor Implementation with MIPS(9 Instructions)

Computer Architecture

MIPS instruction 9개 lw, sw, add, sub, and, or ,slt, beq, j 에 대한 하드웨어 구현을 간단한 논리회로 지식과 함께 알아보자.

CPU 성능의 척도는 대략 instruction count, CPI, Cycle time 등으로 알아보았다.

instruction count는 ISA, compiler로 결정되며 소프트웨어 레벨이라 볼 수 있다.

하지만 CPI와 Cycle time은 ISA를 위한 하드웨어 구현에 의해 결정되며 이번 포스트부터 MIPS instruction을 위한 하드웨어 구현을 알아본다.

두 가지 구현으로 바라본다.

- Simplified version: 간단한 구현 (1 instruction per 1 cycle)

- More realistic pipelined version: 현실과 비슷한 파이프라인이 추가된 버전

How instruction executes

instruction이 처리되기 위한 간단한 과정을 알아보자.

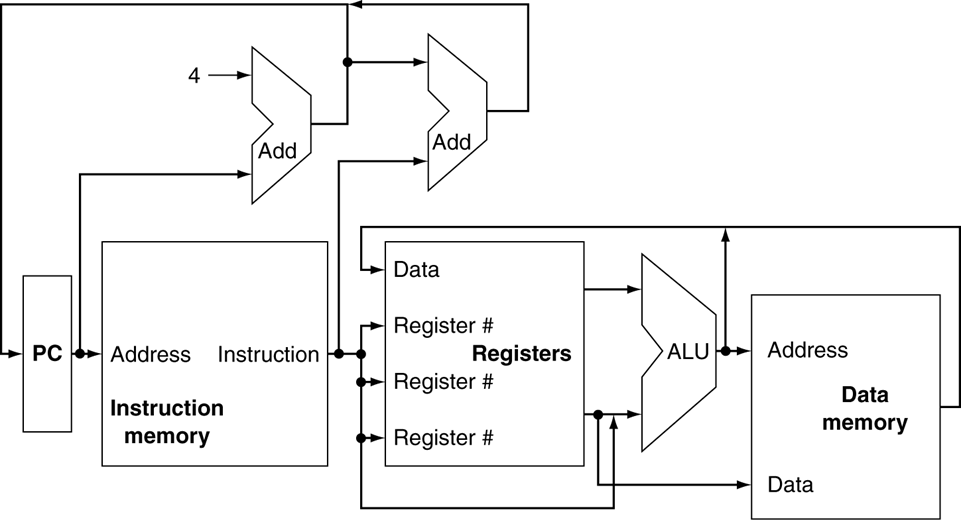

- Instruction fetch: PC에 있는 주소값을 통해 instruction을 메모리에서 읽어온다.

- Instruction decoding and register fetch: instruction을 해석하고 instruction의 주소를 통해 미리 레지스터의 정보를 읽어온다.(이는 레지스터의 성질로 인해 무조건 사용되지 않는다.)

- Instruction 처리: instruction을 수행해준다.

ALU

산술연산

메모리 주소 연산(immediate + value register holds)

branch(PC에 점프할 주소를 저장)

Memory

lw/sw

PC: target address or PC + 4

(레지스터로 이어지는 wire는 32개로 이루어져있다고 가정한다. 1 bit per 1 wire)

Logic Design Basics

논리회로의 간단한 지식을 알아보자.

- Combinational logic: input -> output으로 바로 반영된다.

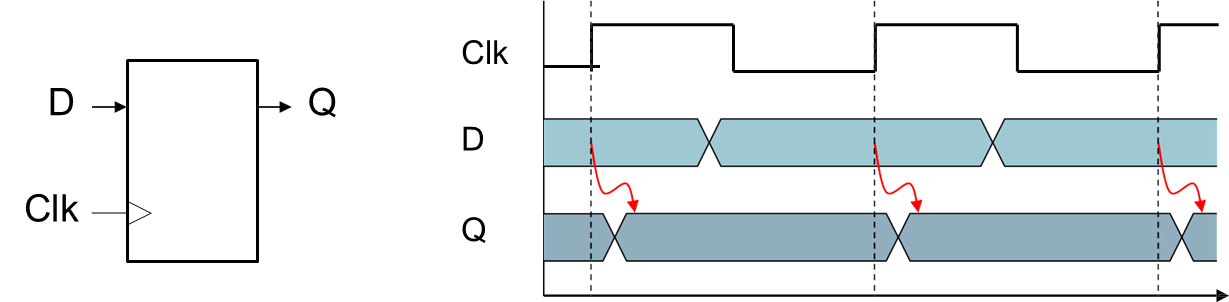

e.g. AND, Adder, MUX, ALU 연산- State(sequential) elements: input + 이전의 output이 현재 output에 영향을 끼친다.

e.g. 레지스터에 data 저장

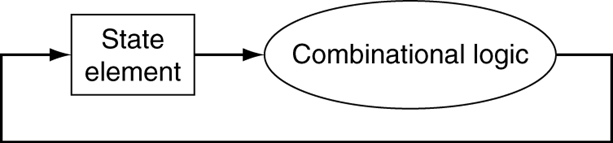

위의 그림은 State element인 레지스터의 동작방식이다.

Clk이 0에서 1로 변경될 때,(Edge-Triggere) 이때 D의값이 반영되어 Q가 변경된다.

여기서 D를 write하기 위한 값, Q가 결과값이라 생각하자.

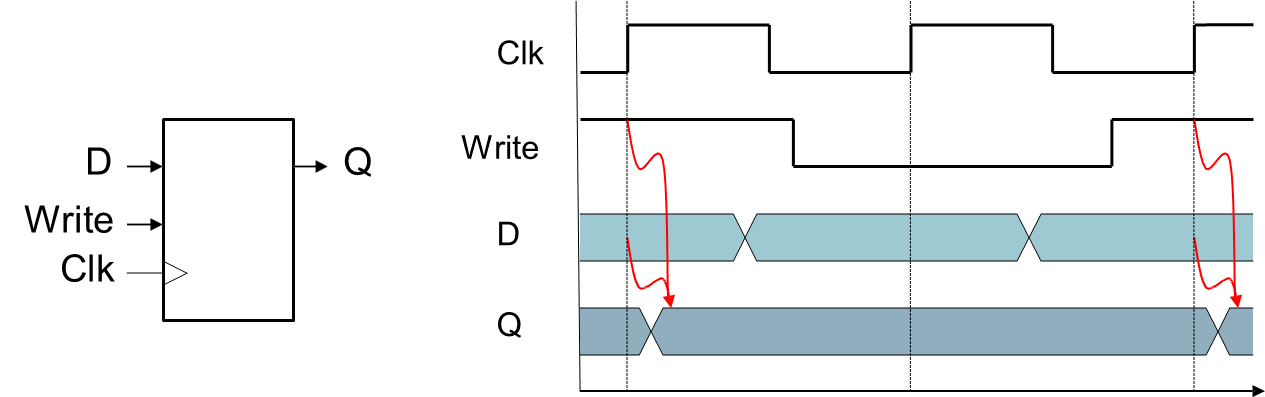

위와 같이 control signal인 write를 통해 무조건 Clk이 edge triggered 될 때가 아닌, write 명령이 들어왔을 때, 값을 쓴다.

Clocking Methodology

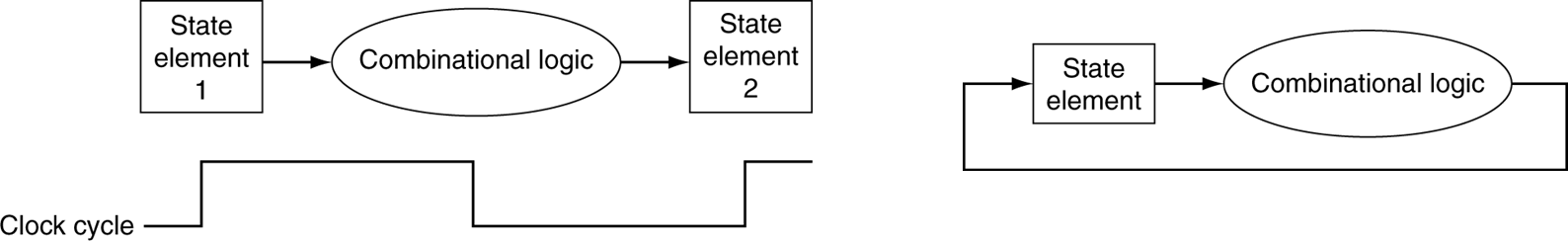

Combination logic은 delay가 존재한다. input에서 output으로 나오는데 당연히 있을 것이다. 이 logic을 길게 엮으면 delay는 당연히 길어질 것이다.

state element는 clock 한 cycle 마다 연산을 할 수 있는 준비가 되어야 한다고 봤을 때, clock의 한 싸이클은 얼마나 되어야 할까?

state element 사이에 Combination 연산이 발생할 때, 각각 delay가 어느정도인지 모를 것이다. 그럼 시스템에서 가장 긴 delay(path가 긴)에 맞춰서 clock cycle을 맞춰야 한다. 그래야 모든 연산들이 한 cycle에 수행될 수 있을 것이다.

이 사이에 ALU도 가고, 메모리도 가고 등 이러한 작업 중 가장 긴 path를 한 싸이클로 잡는다.

실제로 이러한 path 중 가장 긴 것을 한 싸이클로 본다.

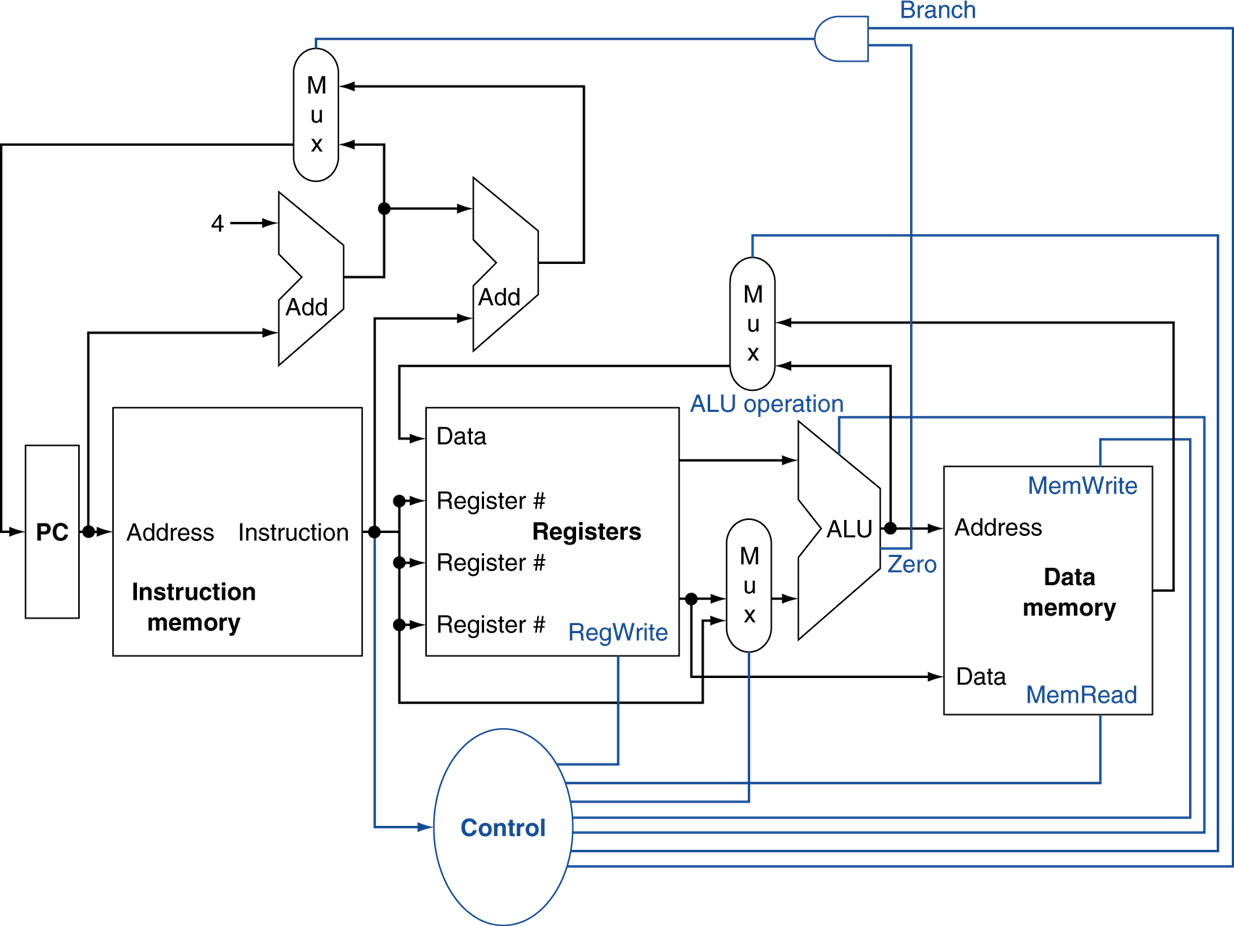

여기서 파란 글씨는 다 control signal 이다. 어떤 연산인지 알려준다.

이건 전체적인 모습이다. 세분화하여 알아본다.

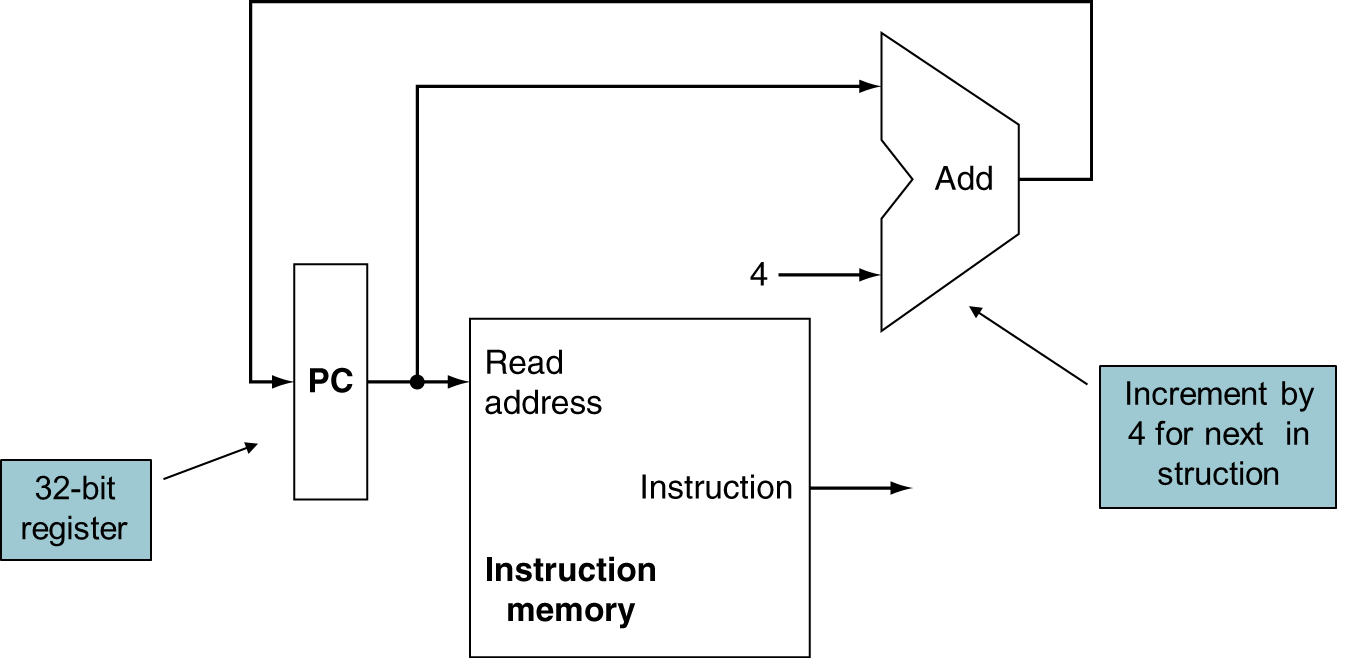

Instruction Fetch

PC의 주소를 읽어 메모리를 참조해 Instruction을 반환한다.

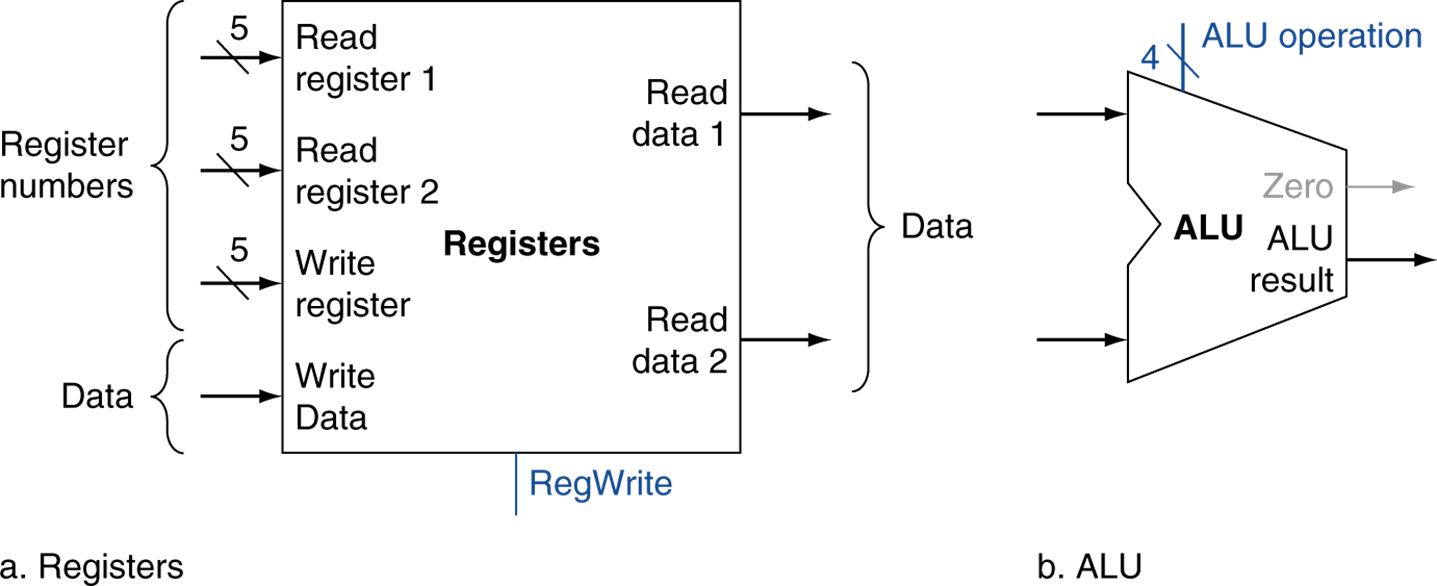

R-Format Instructions

5bit의 번호, 32개의 레지스터

- ALU operation: lw, add, sub, or, and, slt(왜 4bit인지는 나중에)

- RegWrite: wrtie인지에 대한 flag

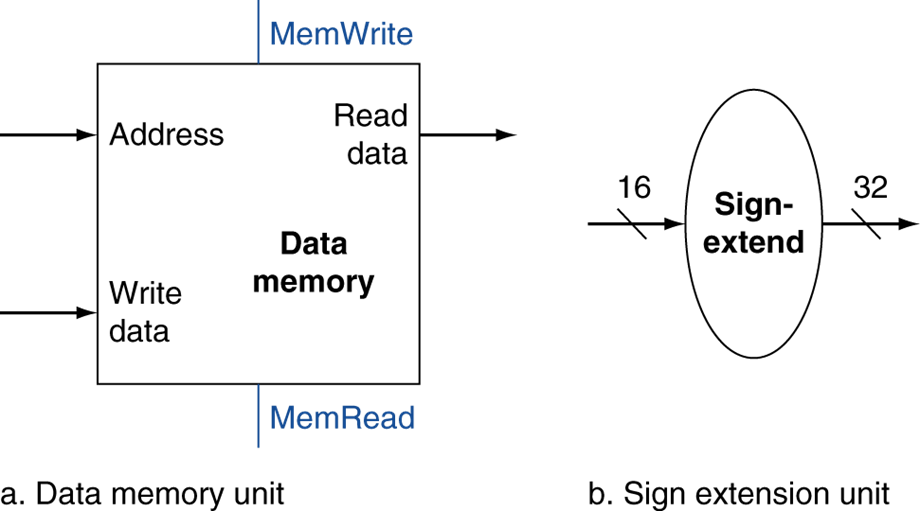

Load/Store Instructions

상수 + 레지스터 값을 계산할 때, 16bit을 32bit으로 확장한다.

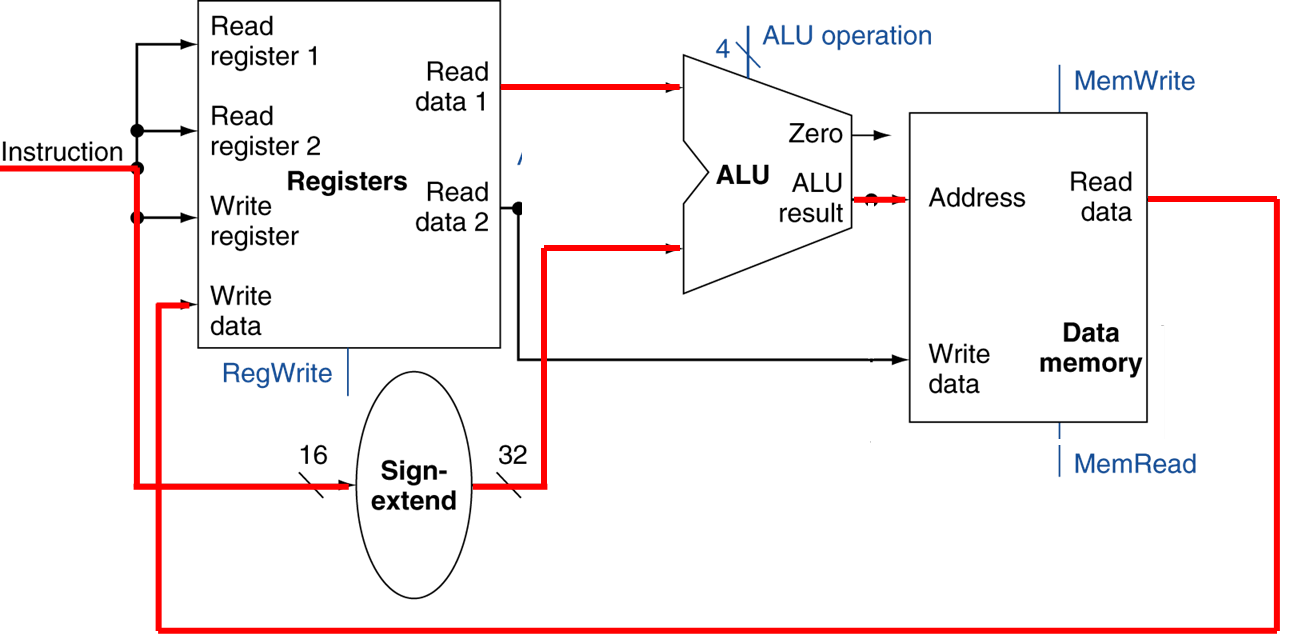

Load instruction

가장 긴 PATH는 Resister file -> Register file로 돌아오는 path(Read to Write data)이다.

이것을 clock period로 설정해야한다.

ALU에서 상수 + 레지스터 값으로 읽어올 메모리를 계산하고 참조하여 Write data 한다.

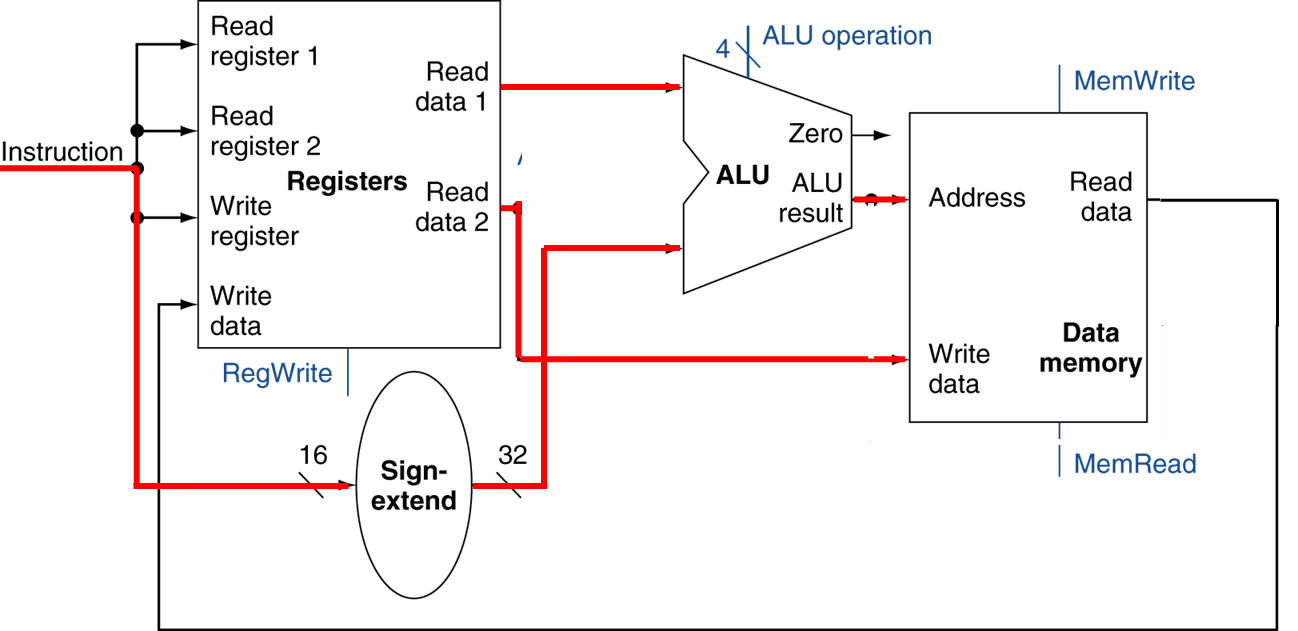

Store instruction

ALU에서 상수 + 레지스터 값으로 저장할 메모리를 계산하고 Read data2의 값을 저장한다.