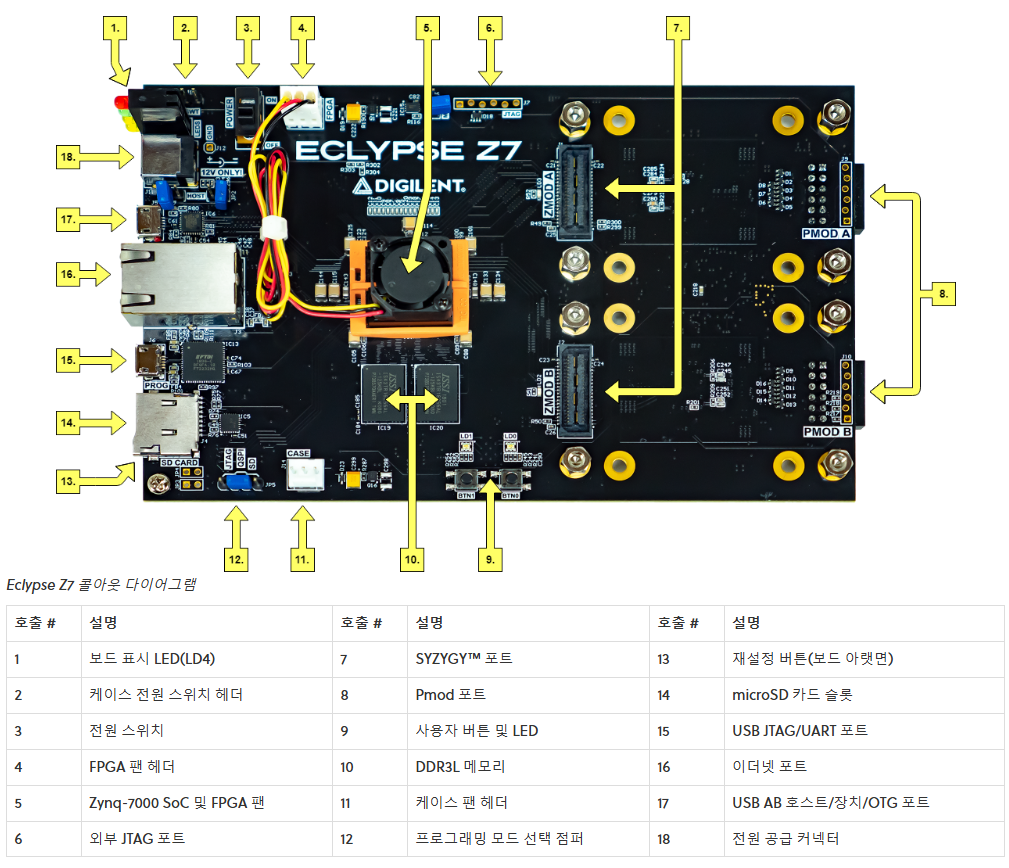

보드 기능 관련

Zmod Scope(이전 명칭 Zmod ADC ), Zmod AWG(이전 명칭 Zmod DAC )

오버플로우 / 부호화

비트 슬라이싱

ZMOD

DMA-FPGA에서 HDL-Embedded C 데이터 전송

DMA를 통해 ARM 코어의 CPU가 다른 작업을 수행하기 전에 전송이 완료될 때까지 기다릴 필요 없이 자체와 DDR 간에 데이터 전송을 간단히 시작할 수 있음, DMA를 통해 CPU는 외부 장치와 DDR 간에 전송을 시작

- PL의 HDL과 FPGA의 프로세서에서 실행되는 임베디드 C 간에 데이터를 전송하는 방법

< PL과 PS 간의 데이터 전송을 수행하는 방법 >

- 직접 메모리 액세스(DMA) 전송

: DMA를 통해 ARM 코어의 CPU가 다른 작업을 수행하기 전에 전송이 완료될 때까지 기다릴 필요 없이 자체와 DDR 간에 데이터 전송을 간단히 시작할 수 있음, DMA를 통해 CPU는 외부 장치와 DDR 간에 전송을 시작할 수있음

[Xilinx DMA IP 블록을 사용하여 AXIS 버스를 통해 메모리 맵 인터페이스를 스트리밍 인터페이스로 변환하여 가능한 가장 기본적인 방식으로 DMA의 기능을 시연]

-

AXI Stream Hand Shake

tdata: 데이터 버스

tvalid: 마스터 인터페이스가 tdata 버스에 배치한 데이터가 유효할 때 어설션됨

tready: 슬레이브가 tdata 버스에서 데이터를 수신할 준비가 된 상태에 있을 때 주장됨

tlast: tdata 버스의 스트림에서 마지막 패킷이 지속되는 동안 마스터가 주장하여 슬레이브에게 해당 패킷 다음에 데이터가 나오지 않을 것이라고 알립니다.

tkeep: 마스터가 설정한 tdata 버스의 패킷에 대한 2차 검증으로 패킷이 스트림의 일부인지 여부를 나타냅니다. -

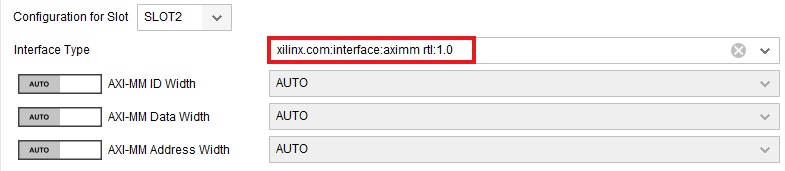

AXI DMA IP

Enable Scatter Gather Engine 선택 해제 + Allow Unalingned Transfers 선택 = 인터페이스 작성시 조금 더 여유로운 공간을 제공함

- Zynq PS IP를 추가하고 블록 자동화를 실행하여 개발 보드에 대한 보드 사전 설정을 적용

- AXI DMA IP 블록 추가

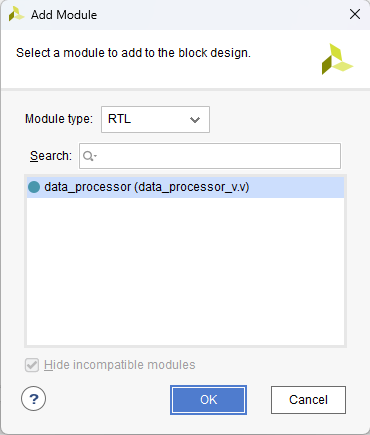

- 모듈(.v파일) 추가 방법

: Add Sources - Add or Create Design Sources - Add Files - 추가할 .v 파일 선택

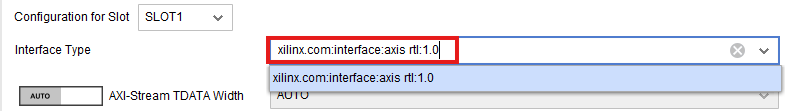

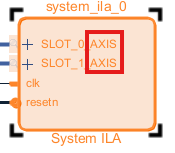

- ILA 포트 AXI - AXIS로 변경하기

-

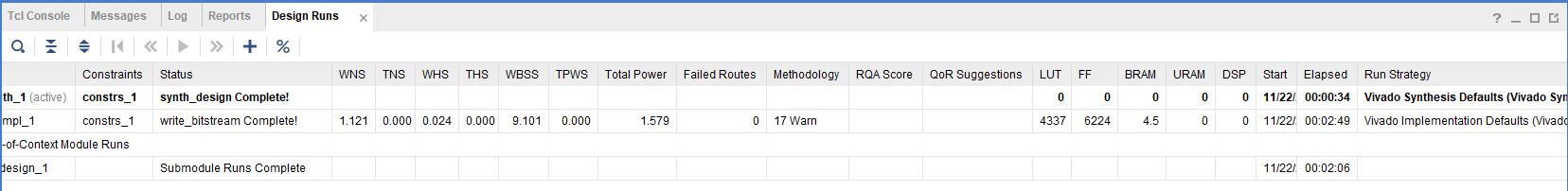

비트스트림 결과

-

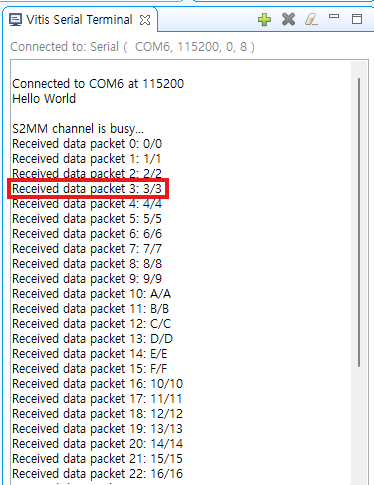

Vitis 결과

: Received data packet : <수신 데이터>/<송신 데이터>

잘 송신되고 수신된 것을 알 수 있다.

DAC (출력)- ADC (입력) 시작

DAC로 데이터를 전송하여 램프파를 출력하고 ADC가 이를 읽고 그 결과가 직렬 터미널을 통해 출력되는 모습을 직렬 터미널에서 살펴보기. 프로젝트1

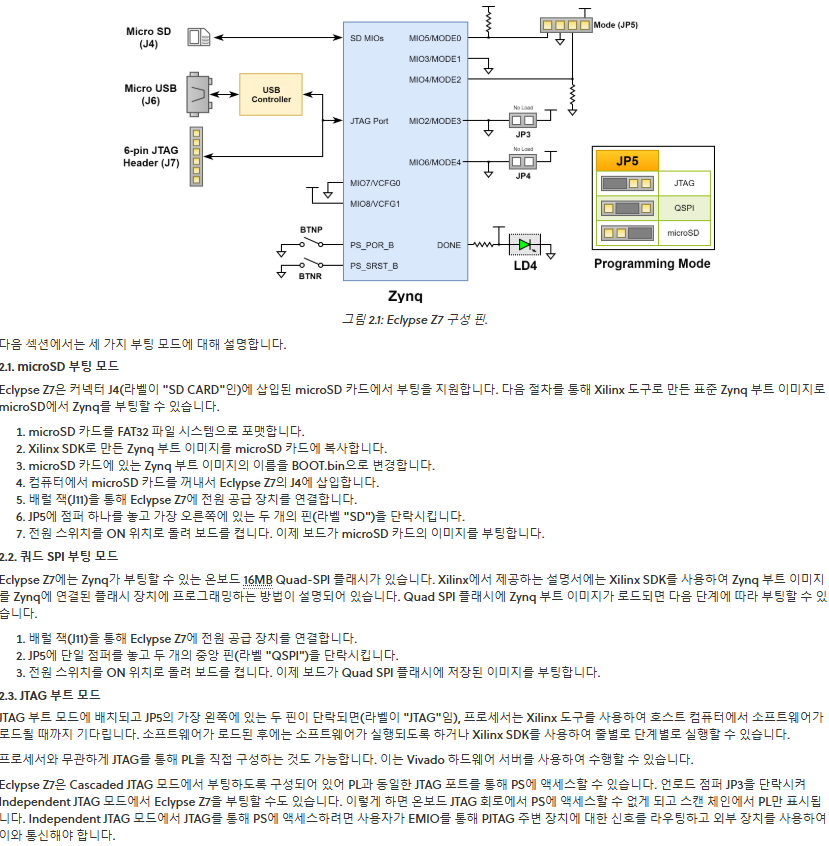

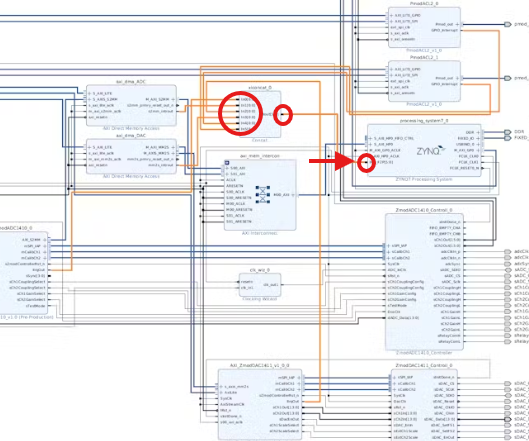

1. Zynq7 Processing System

- Eclypse 보드는 Zynq-7000시리즈의 FPGA이므로 해당 프로세서 사용

추가 후 Run Block Automation탭을 사용해 Eclypse 보드에 맞는 핀아웃 설정

2. Board 탭

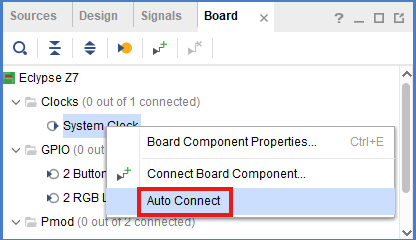

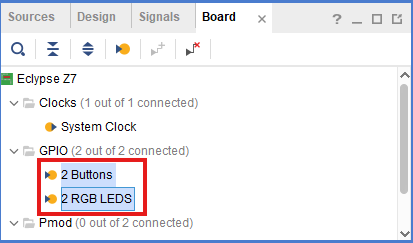

- System Clock 설정

- GPIO를 통해 모든 소프트웨어 설계에 사용할 수 있는 RGB LED 2개와 푸시 버튼 2개 연결(Sytem Clock과 동일하게 Auto Connect 후 Run Block Automation)

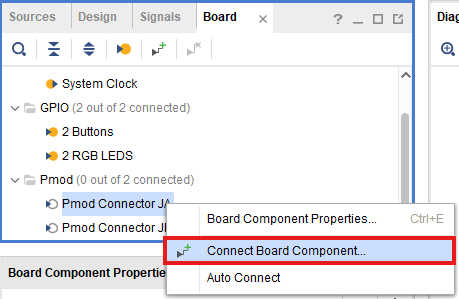

- 문제 해결 및 일반 상태 출력을 위한 OLED 디스플레이(PMOD OLED-SSD1306 선택)

: PMOD Connector JA를 마우스 오른쪽 버튼으로 클릭하고 'Connect Board Component' 옵션을 선택

(내용추가) Pmod IP는 Vivado 2019.1을 통해서만 지원하기에 불가했음

3. ZMOD IP를 추가하기 전 Zynq PS 구성 조정

-

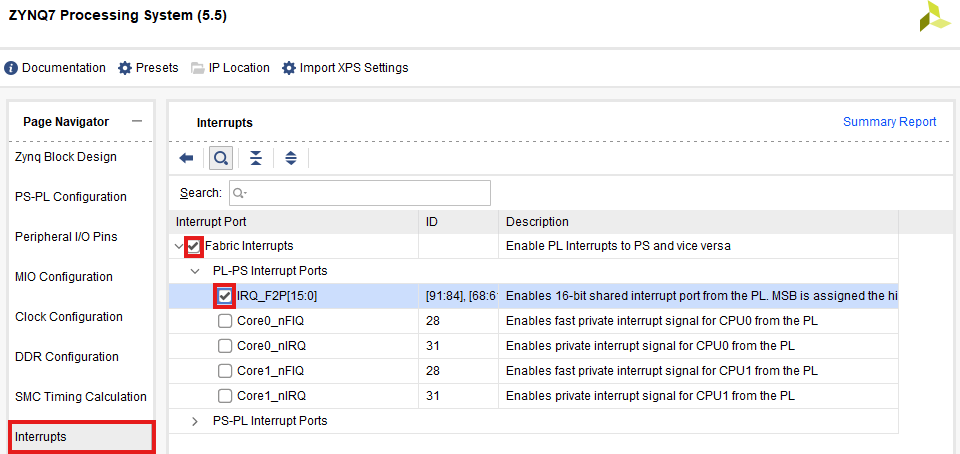

Zynq IP에서 인터럽트 입력 활성화

-

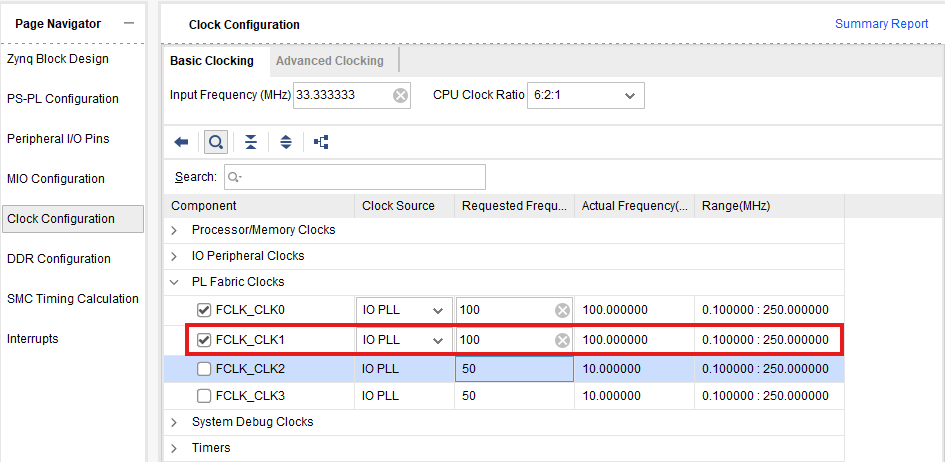

단일 클록 소스에서 지원하기에는 주변 기기가 너무 많기 때문에 Zynq PS의 두 번째 클록 출력도 추가

: PL Fabric clocks 메뉴를 선택하고 FCLK_CLK1 상자를 체크한 뒤 값을 100MHz로 설정

-

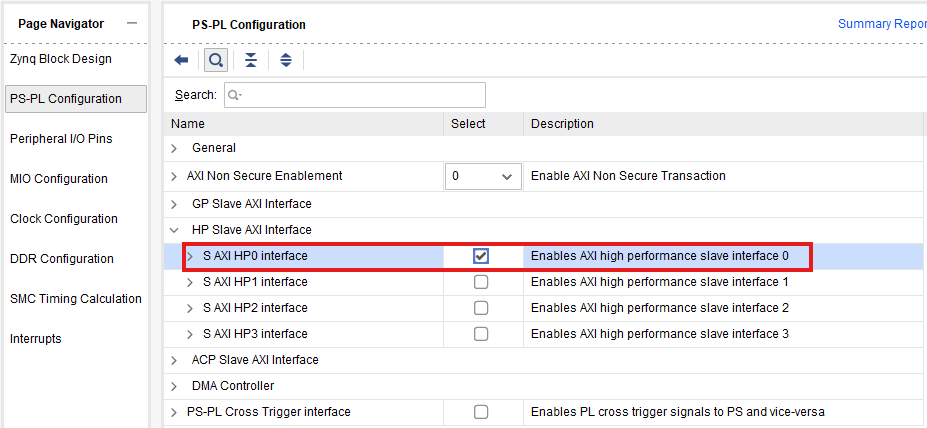

ZMOD는 DMA가 DDR에서 데이터를 읽고 쓸 수 있도록 고성능(고속) AXI 포트 활성화

: PS-PL 구성으로 이동, HP Slave AXI Interface 메뉴 아래에 있는 S AXI HP0 인터페이스 옆의 상자 체크!

-

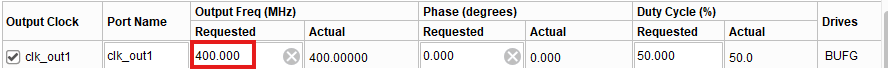

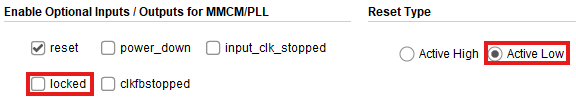

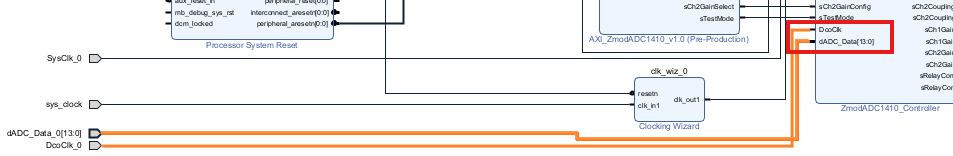

Clocking Wizard IP 블록에 대한 일부 클로킹 구성 조정

: clk_out1을 400MHz로 설정, '잠금' 옵션의 선택을 해제하고 재설정 유형을 활성 로우로 체크

4. ADC ZMOD

<수정>

Vivado에서 AXI controller IP가 더 이상 사용 할 수 없다. 원형 버퍼(FIFO, First In First Out방식으로 동작)의 제한으로 인해 특정 상황에서 기능적으로 문제가 발생했기 때문

사용하고자 한다면 Zmod IP Version 1 Support for Vivado 2019.1 에서 다운로드 할 수 있음

-

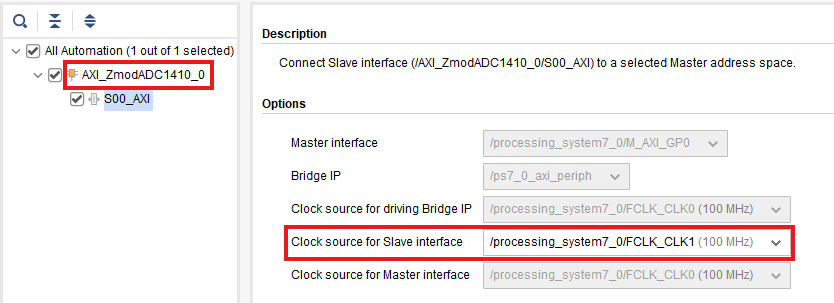

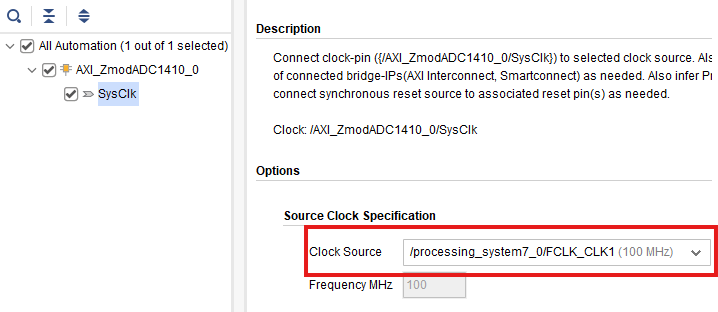

AXI_ZmodADC1410_v1.0 IP, 슬레이브 인터페이스의 클록 소스를 FCLK_CLK1로 변경

: ZMOD 인터페이스 부분을 지원하는 데 전담되는 클록 소스이다.

-

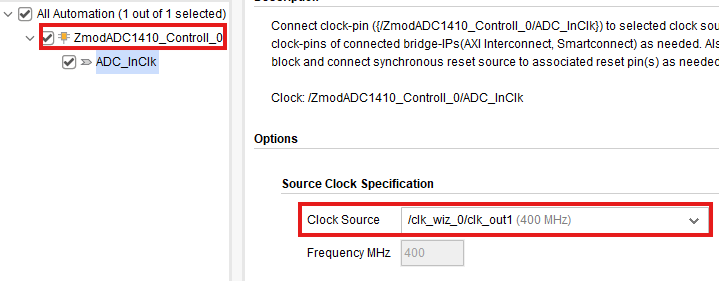

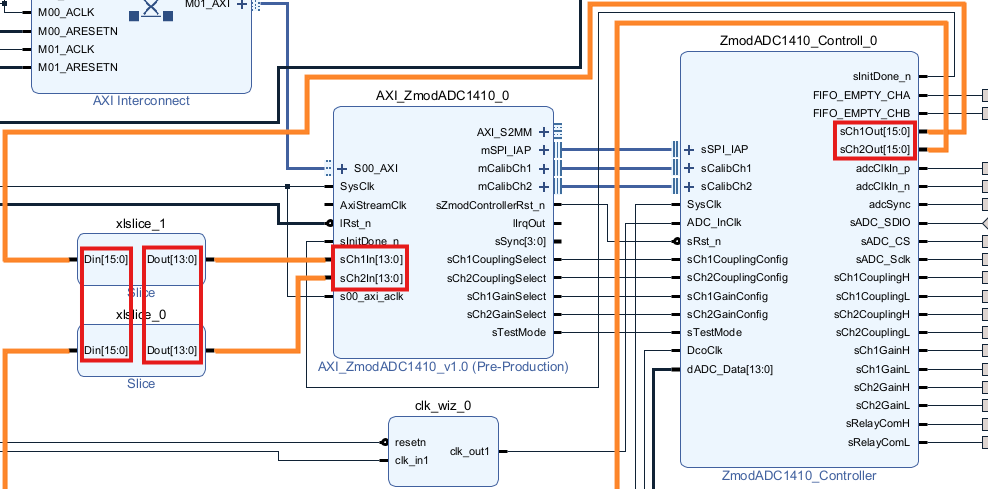

ZmodADC1410_Controller IP, ADC 참조 클록(400MHz)

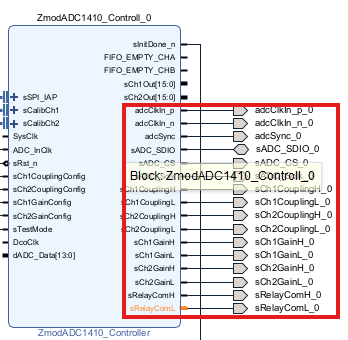

ZmodADC1410_Controller의 출력 포트 대부분은 SYZYGY 커넥터로 라우팅된 FPGA의 핀에 직접 연결된다.

: 적절한 출력, 입력 신호를 ADC 외부로 만든다.

-

ADC ZMOD IP의 SysClk 클록 포트, FCLK_CLK1로 설정

- 두 개의 slice IP 블록을 추가하여 데이터 폭 출력을 변환

: 두 ADC ZMOD IP 사이의 데이터 포트 폭이 일치하지 않습니다. 이 포트는 컨트롤러 IP가 ADC 출력에서 인터페이스 IP로 보낼 디지털 데이터를 출력하는 방식

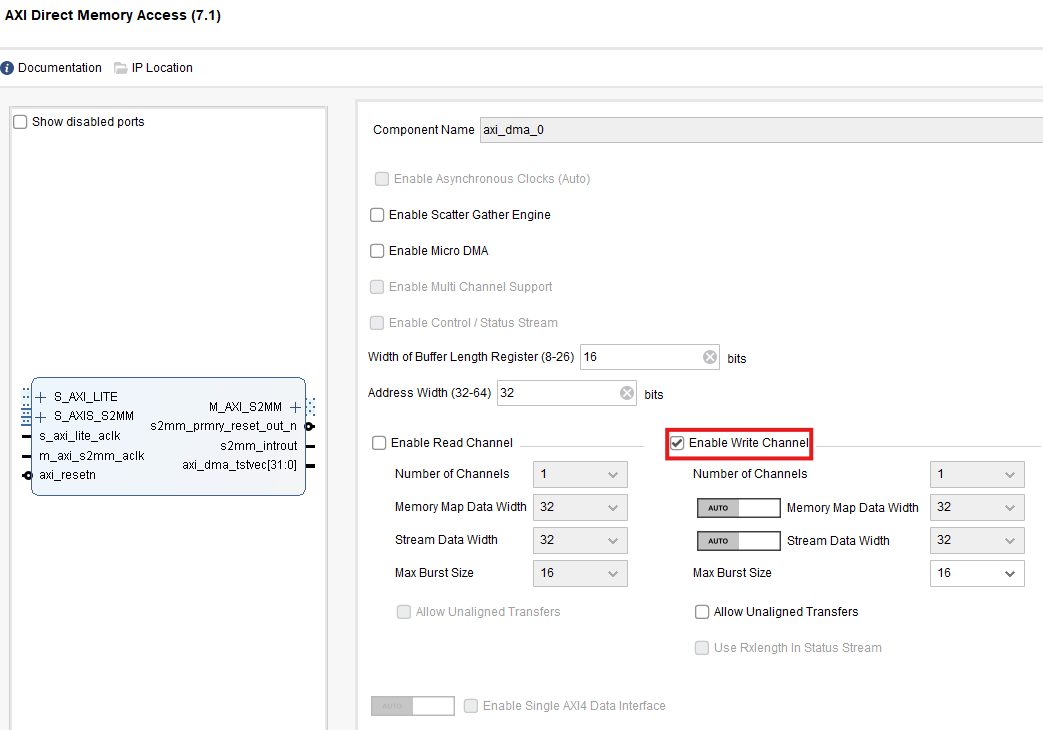

5. AXI Direct Memory Access IP

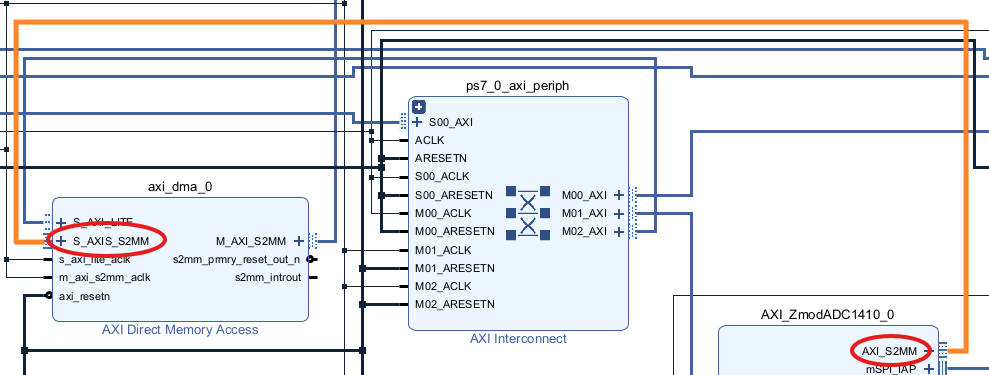

- ADC에서 DDR로 들어오는 디지털 데이터를 씁니다. (쓰기 전용 DMA)

- AXI_ZmodADC1410_v1.0 IP에서 AXIS_S2MM (메모리 매핑)포트를 쓰기 전용 DMA IP 블록의 S_AXIS_S2MM (메모리 매핑)포트로 연결

여기까지가 ADC ZMOD이다.

6. DAC ZMOD

- AXI_ZmodDAC1411_v1_0_v1_0 IP, (RBA)AXI Lite Clock source를 FCLK_CLK1으로 연결, ADC ZMOD IP의 IRst_n 포트에 수동으로 연결

RBA는 Run Block Automation이다.

-- 이후에서 막힘

7. Concat IP

- 각 인터럽트의 출력을 Concat IP의 입력에 연결해 Zynq PS의 인터럽트 입력에 연결한다.(Zynq PS에 연결)

HDL Wrapper : 인스턴스화 하기 위해서

<문제 발생>

-

2019년 이후로 Vivado에서 AXI controller IP를 더 이상 사용 할 수 없다. 원형 버퍼(FIFO, First In First Out방식으로 동작)의 제한으로 인해 특정 상황에서 기능적으로 문제가 발생했기 때문이다.

이전 버전의 IP를 찾아서 시도해봤지만 AWG Controller IP에서 호환성에 문제가 생겨 실패함(약 80%완성)

-

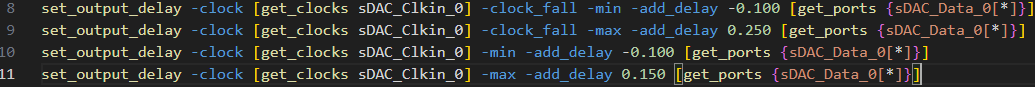

타이밍 오류

-

.xdc 제약 조건 파일에 딜레이 입력, 보류 시간을 주기위함

-

신호가 통과할 수 있도록 여분의 게이팅을 추가하여 홀드 타임을 늘리는 것

<결과>

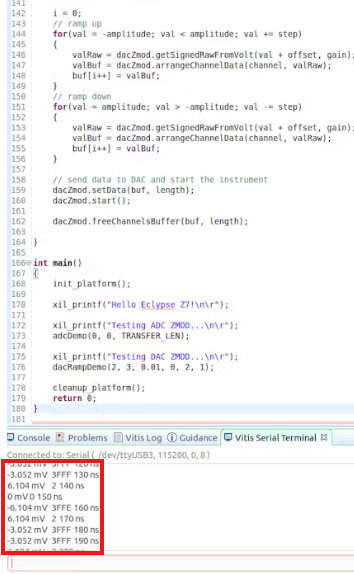

코드 리뷰 1)

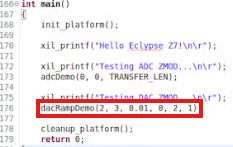

dacRampDemo() : 입력된 파라미터에 따라 램프파를 정의하고, 이를 DAC 버퍼에 작성한 후 출력

ex) dacRampDemo(2, 3, 0.01, 0, 2, 1);

offset = 2: 기준 전압은 2V.

amplitude = 3: 파형의 진폭은 ±3V.

step = 0.01: 각 샘플 간 0.01V씩 변화.

channel = 0: DAC의 채널 0에서 출력.

frequencyDivider = 2: 출력 주파수는 기본값의 절반.

gain = 1: 증폭값은 기본값.

ex ) 3.052 mV 3FFF 130 ns

3.052 mV:

ADC가 샘플링한 신호의 전압 값. 이 값은 DAC에서 생성된 램프파의 한 지점을 나타냄.

3FFF:

ADC의 샘플링 결과로, 16진수로 표현된 디지털 값.

3FFF는 ADC의 최대값(해상도에 따라 달라짐)

130 ns:

이 데이터가 130 나노초 지점에서 샘플링되었음을 의미. 이는 샘플링 주기를 알 수 있는 지표.

Resolution, 해상도 : ADC가 아날로그 신호를 디지털 값으로 변환할 때 사용할 수 있는 비트 수<프로젝트 의의>

전압과 16진수의 패턴을 보면 선형적 증가와 감소가 있음, 애플리케이션이 DAC로 데이터를 전송하여 램프파를 출력하고 ADC가 이를 읽고 그 결과가 직렬 터미널을 통해 출력되는 모습을 직렬 터미널에서 살펴볼 수 있었음

- BOOT.BIN, 부트 이미지, Eclypse의 플래시에 프로그래밍 과정 포함됨

FIR 필터 테스트

AWG Zmod의 출력을 디지타이저 Zmod의 입력으로 다시 루프백하여 가변 주파수 사인파를 공급하여 실제 신호로 FIR의 저지대역과 통과대역을 테스트/검증

- Digitizer의 ADC에서 나오는 데이터 샘플과 AWG Zmod로 전송되는 DAC 코드로 변환되는 데이터 샘플에 대한 데이터 처리 작업

(DAC)AWG Zmod : AWG(아날로그 파형 생성기) 기본 기능을 활용한 사인파를 생성하는 방법 - 단위 원의 360도 각각에 대한 사인 함수의 크기 값을 계산하는 C 코드를 작성 (이때 타이밍과 C 코드에서 각 크기 값을 얼마나 빨리 계산할 수 있는지가 관건임)