xdc 이해하기

ex) Eclypse Z7.xdc 제공

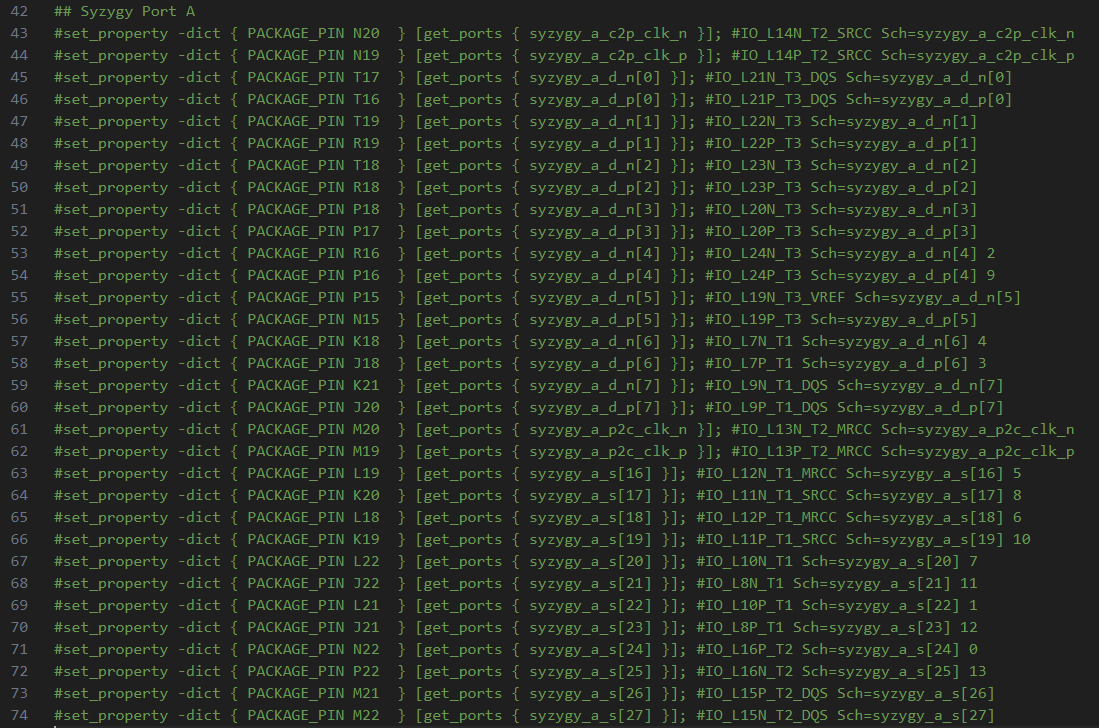

#set_property -dict { PACKAGE_PIN N20 } [get_ports { syzygy_a_c2p_clk_n }]; #IO_L14N_T2_SRCC Sch=syzygy_a_c2p_clk_n#IO_ 부분은 주석(Comment)이다. 이 주석은 해당 핀의 물리적 역할, FPGA의 핀 이름, 또는 회로도(Schematic)에서의 용도를 나타낸다.

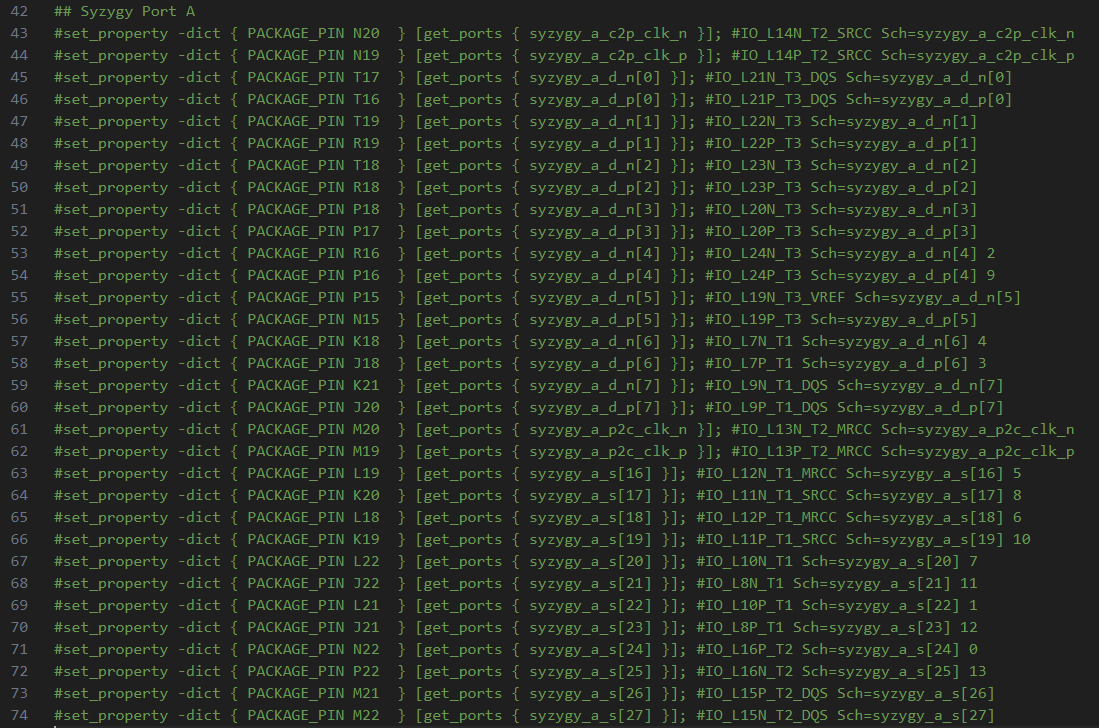

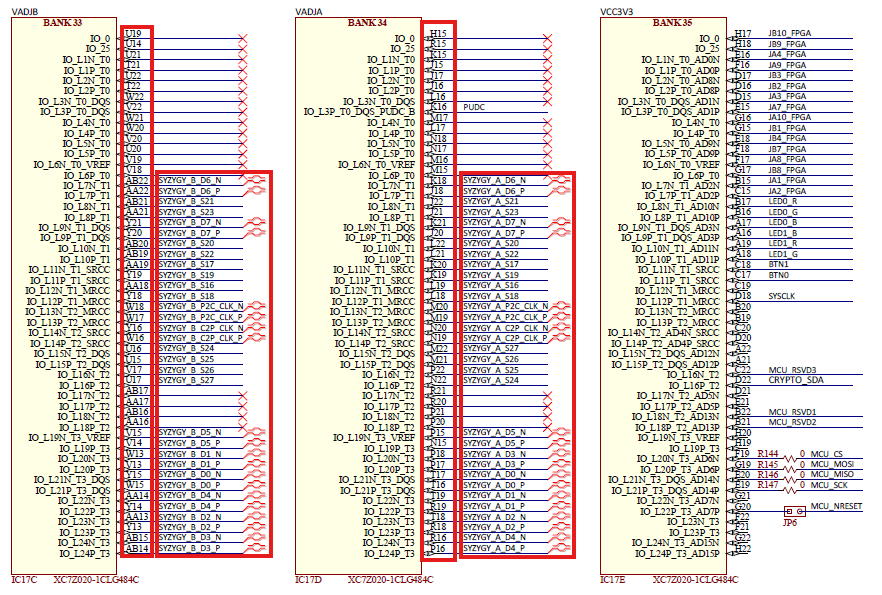

Eclypse Z7 xdc

이 부분을 이해하기 위해서는 몇 가지 자료가 필요하다.

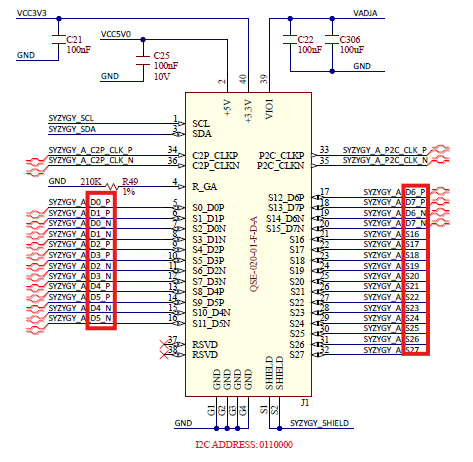

1. Zmod Scope Schematic 페이지 7

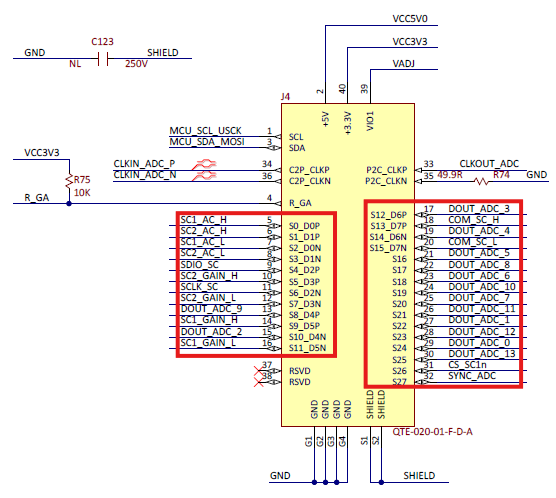

2. Zmod AWG Schematic 페이지 3

3. Eclypse Z7 Schematic 페이지 3, 8

해당 자료를 다운로드

SYZYGY Port A와 Port B에 연결하는 AWG(DAC) , SCOPE(ADC) 사이 PIN-PORT연결 위치는 정해져있다.(임의로 하면 안된다.) 아래에서 각 Port A와 B에 어떤식으로 배치해야하는지 설명하겠다.

SYZYGY Port A

위 사진은 Digilent에서 제공하는 Eclypse Z7-Master xdc파일이다.

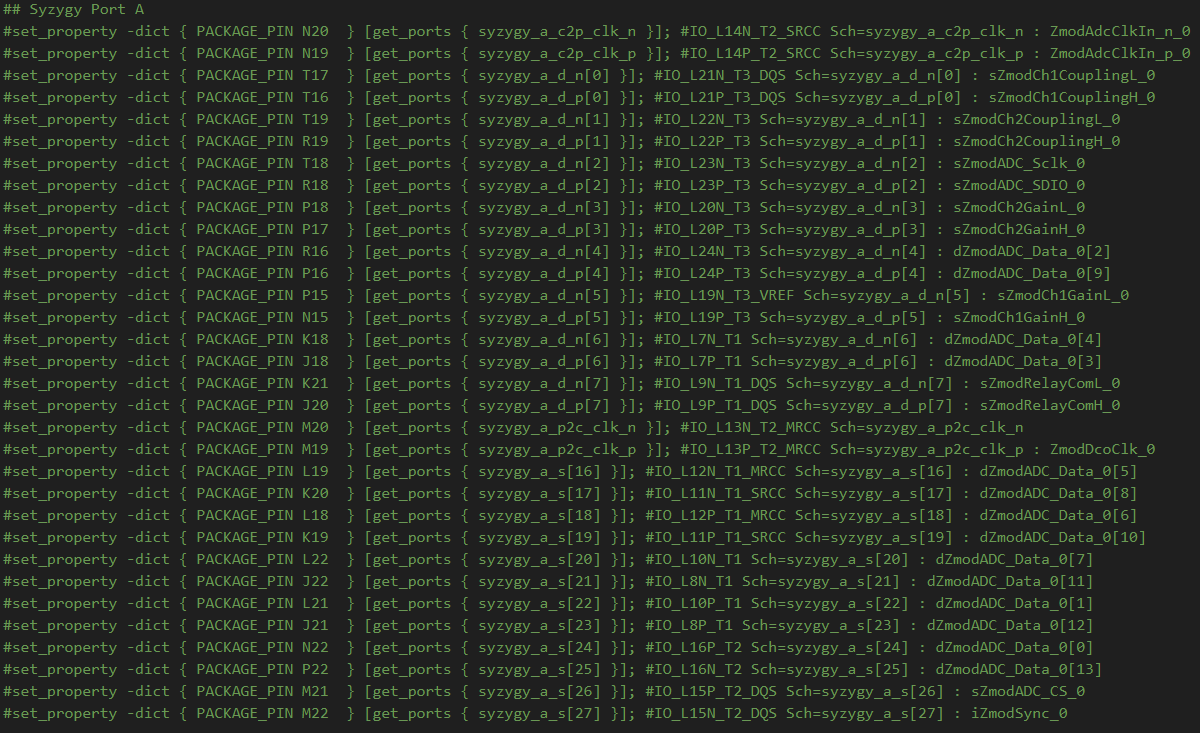

#set_property -dict { PACKAGE_PIN N20 } [get_ports { syzygy_a_c2p_clk_n }]; #IO_L14N_T2_SRCC Sch=syzygy_a_c2p_clk_n : ZmodAdcClkIn_n_0해당 코드할 부분은 get_ports 뒷부분의 { } 내부이다.

그럼 어떻게 수정해야 하는가? 이를 알기위해서는 앞서 말한 3가지 파일을 다운로드 해야한다.

좌측 부분을 보면 DO_P가 있다. 여기서 P,N은 차동입력을 의미한다.(클락과 관련)

xdc 코드 46번째 줄을 살펴보면 syzygy_a_d_p[0]이 보일 것이다. 여기서 d_n[0]이 바로 DO_P를 의미한다. 그럼 여기서 어떤 포트를 연결해야 할까? 이어서 SCOPE의 Circuit을 보자.

좌측 붉은 부분 내부를 보면 S0_D0P가 있다. 여기서 DOP가 바로 위 SYZYGY Port A의 DO_P와 같은 의미이다. 즉 SC1_AC_H를 연결해 주면된다. 그럼 SC1_AC_H는 무엇인가? 여기서 부터는 해당 ZMOD의 IP를 살펴봐야 한다. (참고로 Digilent에서 제공하는 ECclypse Low pass Filter DEMO의 xdc를 참고하면 쉽게 알 수 있다.)

SC1_AC_H = sZmodCh1CouplingH_0 즉 여기서 C1 = CH1을 의미하고 AC = Coupling을 의미함을 눈치 챌 수 있을것이다.

이런식으로 축약해서 IP의 포트를 나타내고 있으니 IP 레퍼런스 자료 또는 Vivado 설계를 하다보면 어렵지 않게 알 수 있을것이다.

아래에 : 뒤에 알맞는 IP 포트를 표시 했다. 이를 참고해서 하면된다.

T16 , T17과 같은 PIN이름은 xdc파일 뿐만 아니라 아래 사진에서도 알 수 있다.

SYZYGY Port B

#set_property -dict { PACKAGE_PIN Y19 } [get_ports { syzygy_b_s[19] }];#IO_L11P_T1_SRCC Sch=syzygy_b_s[19]

- SRCC, Single Region Clock Capable

#set_property -dict { PACKAGE_PIN Y13 } [get_ports { syzygy_b_d_p[2] }]; #IO_L23P_T3 Sch=syzygy_b_d_p[2] : 사용된 포트 sZmodDAC_Reset_0- syzygy_b_d_p[2] = D2P(S4)를 의미한다.

#set_property -dict { PACKAGE_PIN W17 } [get_ports { syzygy_b_p2c_clk_p }]; #IO_L13P_T2_MRCC Sch=syzygy_b_p2c_clk_p : ZmodDAC_ClkIO_0

- syzygy_b_p2c_clk_p = P2C_CLKP , CLKIO_AWG = ZmodDAC_ClkIO_0

xdc 오류

[Common 17-55], [Vivado 12-584], [Vivado 12-180]

[Common 17-55] 'set_property' expects at least one object. ["C:/DLIA_cDrive/Eclypse/Renewal_IP/project_1/project_1.srcs/constrs_1/imports/Constraints/constr_1.xdc":1]

내용 : 제약 조건에 지정된 개체 이름이 올바르지 않음

해결방법 : 합성된 디자인으로 이동하여 넷리스트에서 개체의 실제 이름을 찾기

AMD Sol

[XDC 제약은 대소문자를 구분함]

: 패키지핀 AF28 설정속성 [get_ports CLK_66M_N]

여기서 포트 이름은 실제로 RTL 코드에서 "CLK_66M_n"입니다.

[범위가 지정된 XDC(IP XDC, OOC XDC 등)의 제약은 특정 범위 내의 개체 이름과 계층을 사용해야 한다. 이러한 경고는 개체 이름의 계층이 범위와 일치하지 않을 때 발생할 수 있다]

: 최상위 레벨의 IP 인스턴스 "a_inst"에 있는 a_reg라는 레지스터의 경우 IP XDC의 다음 제약 조건으로 인해 위의 중요 경고가 발생합니다.

set_property INIT 1 [셀 가져오기 a_inst/a_reg]

올바른 제약조건은 다음과 같습니다.

set_property INIT 1 [셀 가져오기 a_reg]