Hello World!

Vivado

개발 환경은 Xilinx Vitis 2023.1에서 진행-

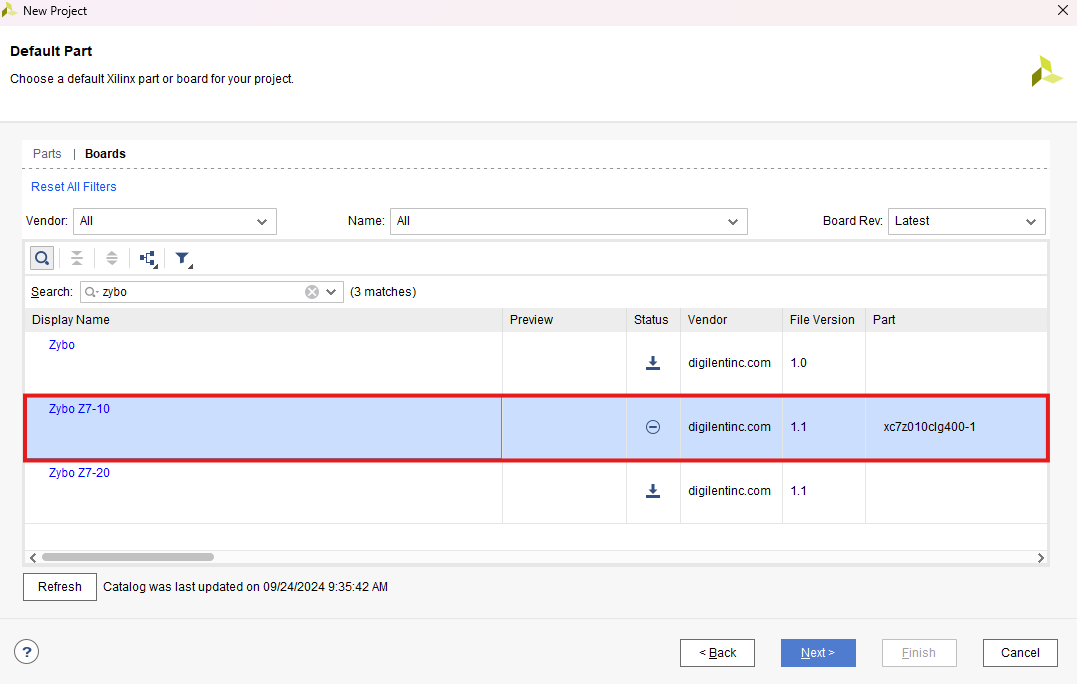

Vivado를 실행 - project name / location을 설정한다. 이때 location에 한글이 들어가지 않도록 주의! - RTL Project - 나머지 다 스킵 - Board 선택 (나는 zybo Z7-10) - Finish

-

Create Block Design - Diagram - '+' 클릭해서 사용할 IP선택(Add IP) - ZYNQ7 Processing System

-

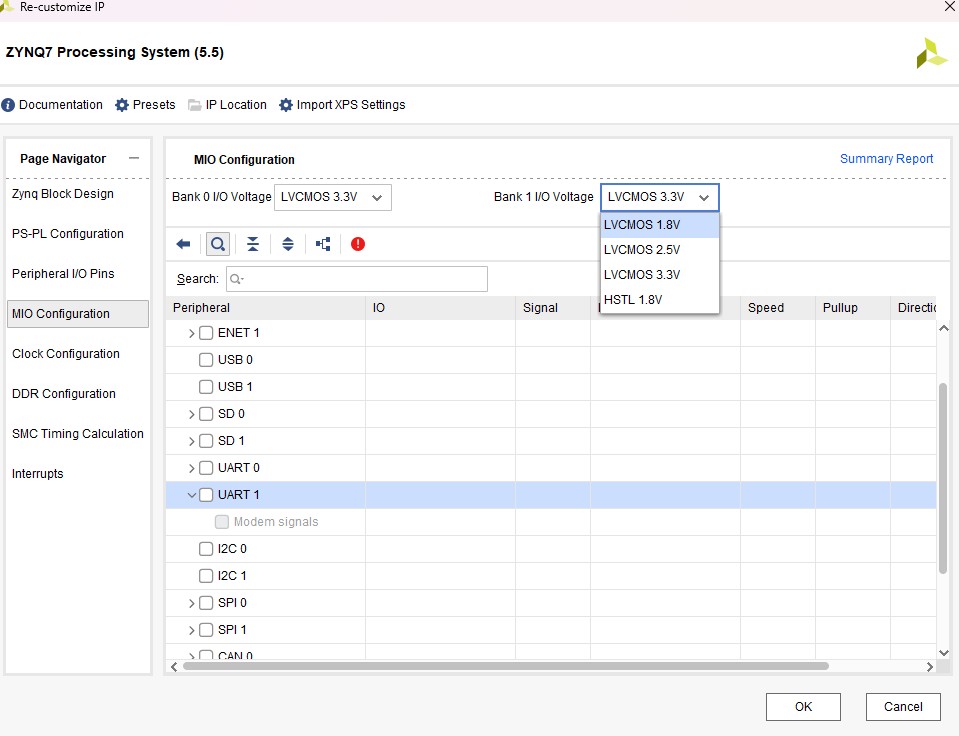

더블클릭해서 Re-Customize

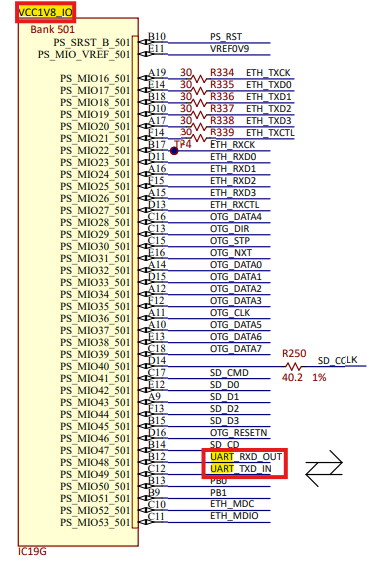

이 같이 사용하는 port에 맞는 전압을 찾아서 설정 해야한다. zybo z7은 아래 링크 참고 (자신이 갖고 있는 Board의 Schematic 참고)Zybo Z7 Reference

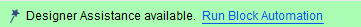

4. Run Block Automation으로 자동 interface 생성

버그로 customize전으로 돌아갈 수 있음 그럼 다시 수정-

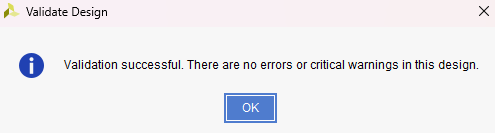

F6 : Validation Check 으로 Successful Message Check

-

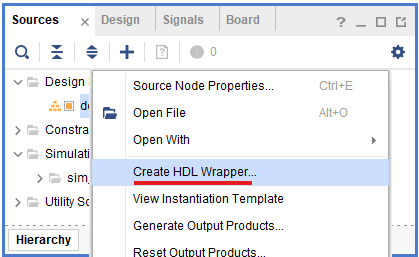

bd file > Verilog HDL file use Create HDL Wrapper

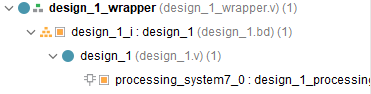

Wrapping 진행 후 아래와 같이 HDL File이 생성된다.

-

Generate Bitstream

- Run Synthesis 와 Run Implementaion이 자동으로 실행된다.

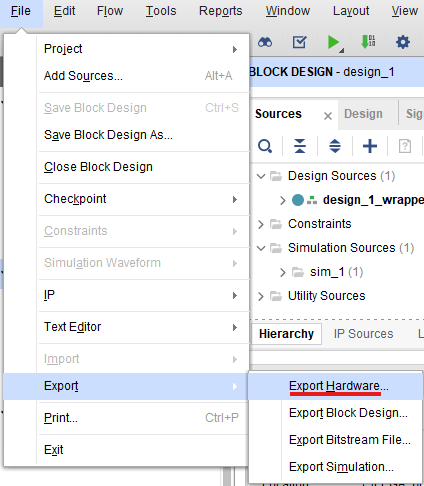

- Hardware File 추출하기 use Export Hardware (.xsa 생성)

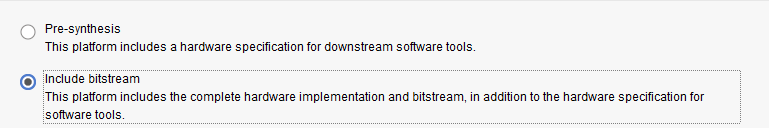

Include bitstream 선택시 Vitis에서도 FPGA에 bitstraem을 올리기 가능

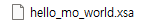

완료되면 .xsa 파일이 생성된다.

// 여기까지하면 Vivado에서 할 일 종료

Vitis

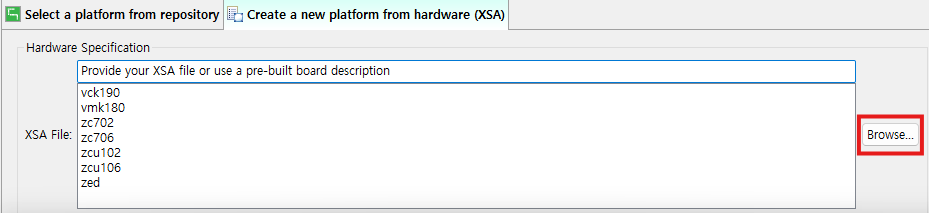

- Vitis 실행 후 경로설정 - Create application Project - Platform - Create a new platform from hardware(XSA) - Browse - Vivado에서 생성한 xsa 파일 선택

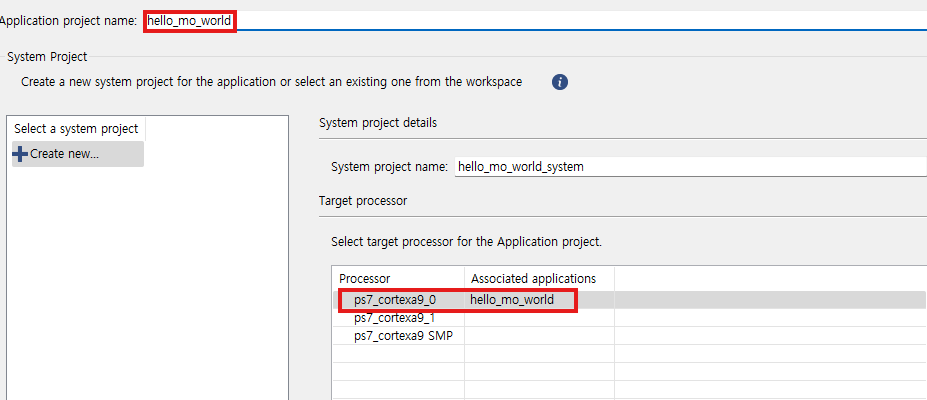

-> projectname - processor 선택(core) - operating system(standalone) - Hello World 선택

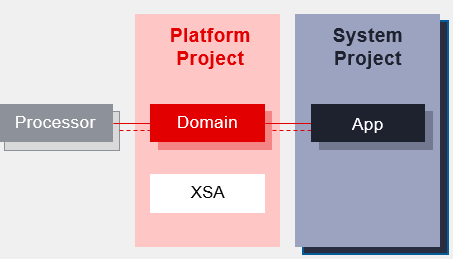

아래 사진은 Vitis 동작에 대한 간단 요약도이다.

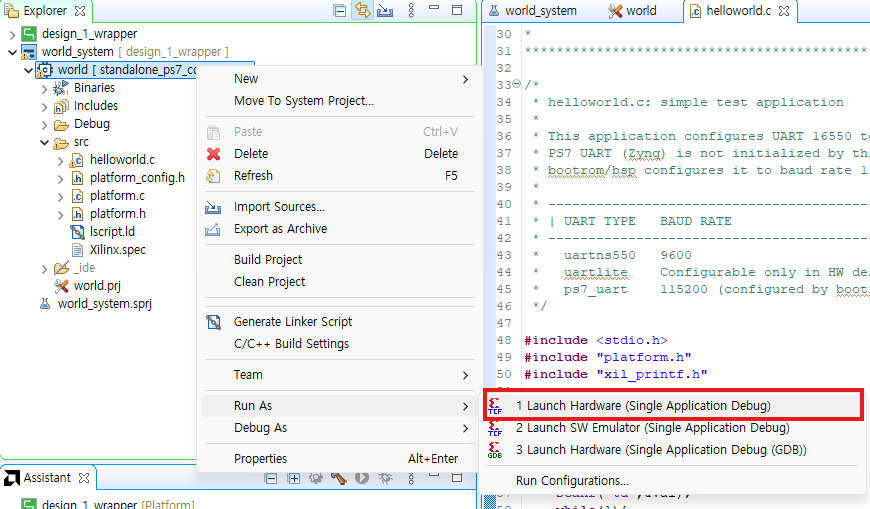

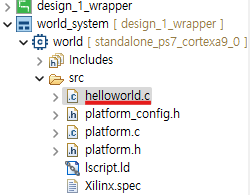

- helloworld.c에서 원하는 코드 수정

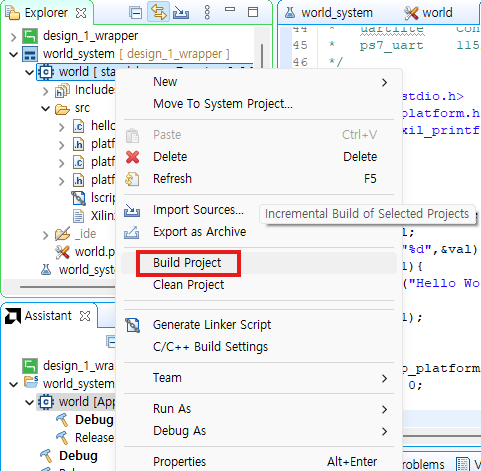

-> Build Project 클릭

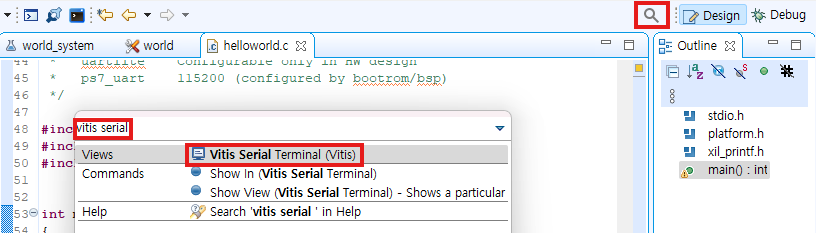

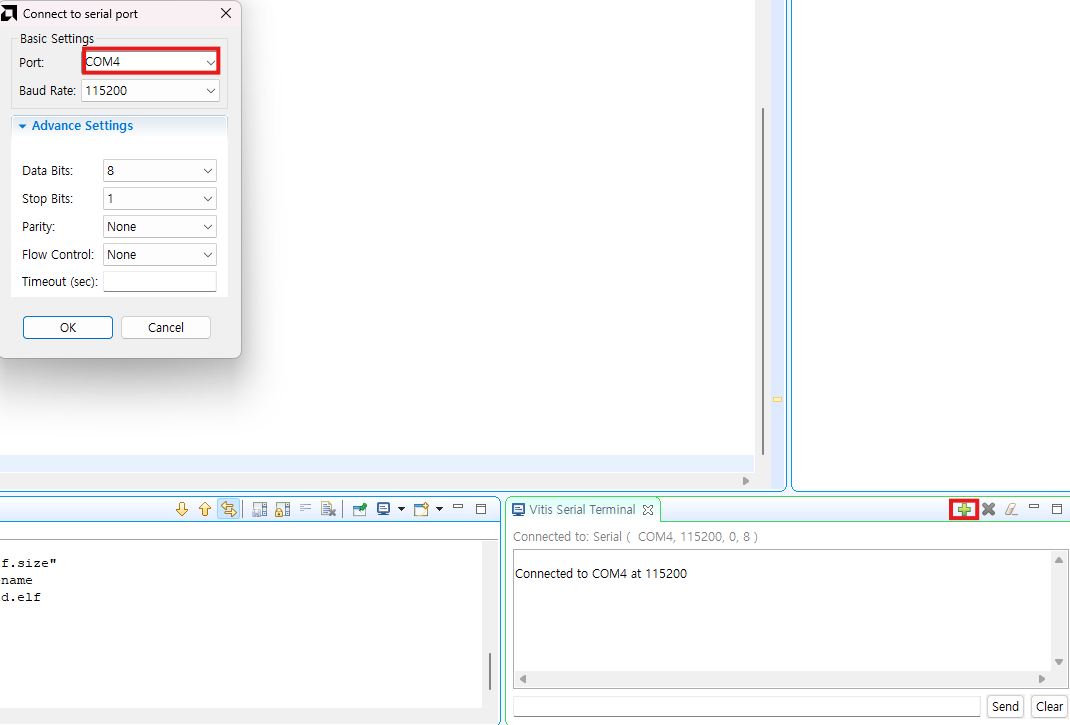

->Terminal

->FPGA 연결

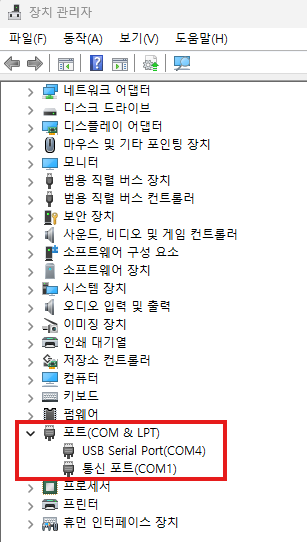

이때 Port number는 장치관리자에서 찾을 수 있다. 아래 사진 참고

->FPGA에서 실행