LED Blink on PL

Xilinx FPGA Port / Pin

-

Port, 포트

: 논리적으로 설계된 모듈의 입출력 신호, 다른 모듈과 통신하기 위한 논리적인 연결점<종류>

1) 입력 포트 (Input Port): 외부에서 데이터를 받아들이는 포트

2) 출력 포트 (Output Port): 내부 데이터를 외부로 보내는 포트

3) 양방향 포트 (Bidirectional Port): 입력과 출력을 모두 할 수 있는 포트

- Pin, 핀

: FPGA나 칩의 물리적인 입출력 연결점, FPGA 칩 자체에서 외부 장치와 물리적으로 신호를 주고받는 전기적 연결부, FPGA 칩의 물리적인 핀에 매핑되어 실제 신호가 흐름

Example for Port & Pin

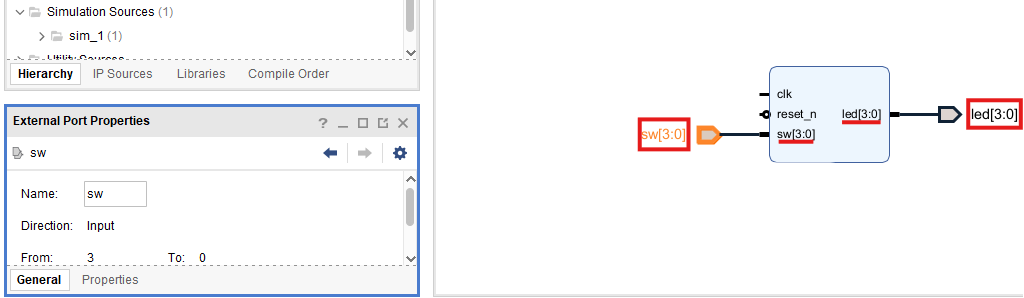

set_property PACKAGE_PIN E3 [get_ports clk] # 포트 clk를 E3 핀에 매핑

set_property PACKAGE_PIN L13 [get_ports in_data[0]] # 포트 in_data[0]을 L13 핀에 매핑이런식으로 PORT / PIN 이름을 정확히 맞춰 줘야한다. // 필요시 Name을 수정해야함

어떻게 연결해야 하는가?

Constraints File인 XDC File(Xilinx Design Constraints File)을 사용

XDC 파일은 Verilog와 같은 하드웨어 설계 언어로 정의한 논리적 포트를 실제 FPGA의 물리적 핀에 매핑Flow: verilog에서 포트를 정의 - xdc file 생성 - "PACKAGE_PIN"을 사용해 Mapping 진행

set_property PACKAGE_PIN W5 [get_ports clk] # clk 신호를 FPGA의 W5 핀에 연결

set_property PACKAGE_PIN V6 [get_ports rst_n] # rst_n 신호를 FPGA의 V6 핀에 연결

set_property PACKAGE_PIN Y11 [get_ports data_in[0]] # data_in[0]을 Y11 핀에 연결

set_property PACKAGE_PIN W13 [get_ports data_out[0]] # data_out[0]을 W13 핀에 연결

//Zybo board에서는 Master XDC Files를 제공하고 있다.Custom한 IP Repositories에 추가하기

[과정]

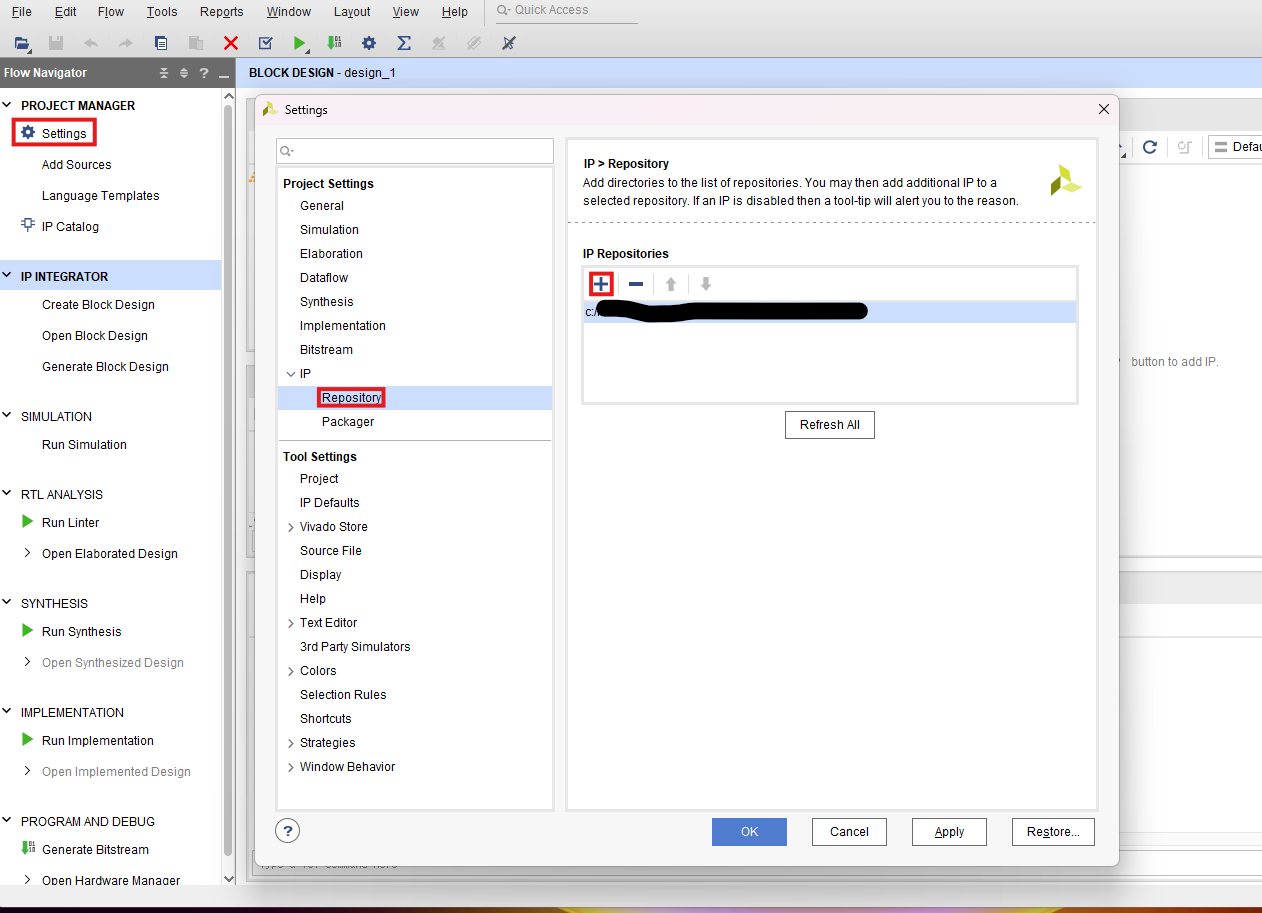

좌측 Flow Navigator에서 Setting - IP - Repository - '+' - Custom한 IP 선택