1. Clock 생성하기

Testbench에서 진행

[이론]

clock의 frequency와 period

cpu는 물리적으로 동일한데 clock의 fequency만으로 동작 속도를 올리 수 있다

over clock = operation frequency

디지털로직 동작에는 clock이 필수적임 - 디지털로직은 clock에 동기화 되어 동작 합니다.

-실습 목표 100MHz의 Freq 를 갖는 clock을 생성

Clone은 깃허브 Repository에 있는 파일을 내 로컬 컴퓨터로 복사해오는 작업이다.

1ps 의미 : precision, 해상도를 의미한다.

timescale 1ns / 1ps인 경우

5 = 5ns의 delay가 생김 / 5.5 = 5.5ns의 delay가 생긴다 but 5.5555 = 5.5555ns의 delay 생기지 않음

2. Sequential Logic, 순차 논리회로 / D Flip-Flop과 Reset

[이론]

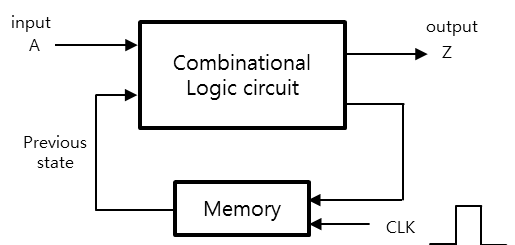

Sequential Logci : 현재의 입력값과 더불어 이전 값의 상태에 따라 출력 값을 결정해주는 논리 회로(현재의 입력값과 더불어 이전 값의 상태에 따라 출력 값을 결정해주는 논리 회로)

clock : 디지털 로직이 동작하기 위해 필요한 Pulse 신호

DUT(Design Under Test) : 검증하고 싶은 대상이 되는 Module

Testbench : DUT 검증을 위한 코드

Reset : 저장공간의 초기화를 위해 사용하는 신호

D - F/F : 디지털로직에 있어 가장 기본이 되는 '저장을 위한 로직' / Sequential Logic을 위한 기본요소

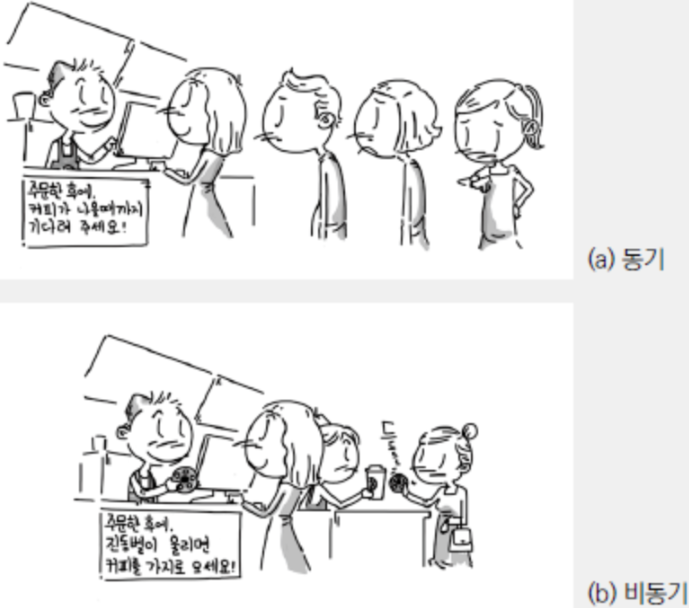

hierarchy : 구조 계층Async Reset(비동기) : Clock이 없는 상태에서도 reset을 걸 수 있다. (물리적 초기화)

Sync Reset(동기) : (System 동작중)Clock이 인가중 일 때 S/W로 reset 신호를 H/W에 전달 할 수 있다.

3. Combinational Logic, 조합 논리회로 / 4칙 연산( + - * / )

[이론]

Combination logic : 현재의 입력 값들을 논리 회로 내부의 '연산자'들을 통해 출력 값을 내보냄