1. FSM(Finite State Machine)

유한 상태 기계

특정 상태(state)에서 출발, 입력 값(input)에 따라 정해진 방식으로 다른 상태로 이동, 그 상태에서의 동작을 정의하는 모델이다. (하나의 FSM Logic은 하나의 State만을 가짐)

Finite State Machines are sequential circuit used in many digital systems to control the behavior of systems and dataflow paths (Control Logic 설계시 용이함)

FSM의 구성 요소는 4가지로 나눌수 있다.

-

상태(State) : 시스템이 특정 순간에 처해 있는 상황을 나타냅니다. 예를 들어, "대기 상태" 또는 "동작 상태" 같은 것들이 있을 수 있습니다.

-

입력(Input) : 상태를 변경시키는 외부 조건이나 신호입니다. 예를 들어, 버튼을 누르거나 센서에서 신호를 받는 것처럼, 시스템에 변화를 일으킬 수 있는 요소입니다.

-

전이(Transition) : 특정한 State에서 특정 입력을 받으면 다른 상태로 이동,변화하는 규칙을 의미합니다. 전이는 주로 상태 다이어그램으로 표현됩니다.

-

출력(Output) : 상태와 입력에 따라 시스템이 내놓는 결과입니다. 이것은 FSM이 각 상태에서 취하는 동작을 의미합니다.

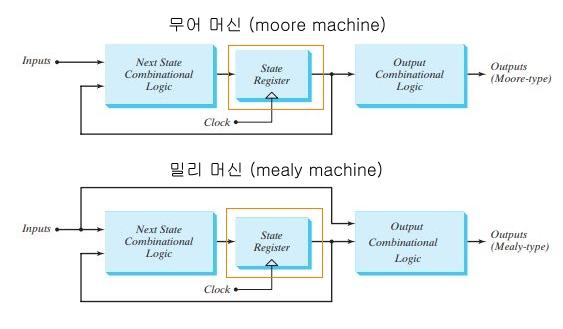

FSM의 유형, How the Output depends on the Input and State

Moore Machine

출력이 오직 현재 상태에만 의존합니다. 입력이 어떻게 변하든 상관없이 출력은 상태에 따라 결정된다.

단방향으로 Data가 흘러가는 시스템에서 사용할 수 있다.

Mealy Machine

출력이 현재 상태, 입력에 의존합니다. 즉, 입력이 바뀌면 출력도 바뀐다.

Ready / Valid : Input까지 봐야하는 양방향 Handshake Interface

2. Internal Memory Interface

Memory

Register

Flip Flop

1bit 저장 = 2 input NAND Gate 8개 , NOT Gate 2개

F/F 1개 Gate Size = 10 Gate //정확하지는 않지만 약80%의 신뢰도를 보임즉, 플립플롭으로 1bit 저장시 많은 resource

1cycle에 f/f개수만큼, 원하는 만큼 read/write 가능

SRAM과 DRAM은 1Cycle의 Access 할 수 있는 Data 양이 제한적이다.

Data Width만큼 Access 할 수 있다.Internal Memory

SRAM

1bit 저장 = Transister 6개 // Flip Flop의 약 10% 크기임을 알 수 있다. (10 * 4 = 40 transister)

2 input NAND Gate = Transister 4개

External Memory

DRAM

1bit 저장 = Transister 1개 + Cap 1개 // Cap무시하면 약 SRAM의 4배 더 저장 가능

Random Address를 통해 Data를 Random하게 접근하는, Random Access하면 Performance가 떨어지게 된다.

// SRAM , F/F은 떨어지지 않음Shape / Size

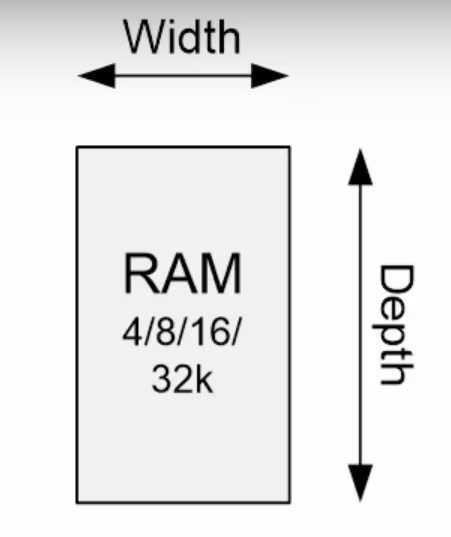

Data의 Width , Depth

저장 할 수 있는 bit, Size : Width와 Depth의 곱 // 면적 = Memory의 Size

Depth : address를 통해 접근할 수 있는 data의 개수 // Depth = Memory 전체 Size / Width

Interface

SRAM - Memory I/F , DRAM - DDRI/F (H.W는 AXI/F를 사용하게 된다.)

//이때 I/F는 Inter Face를 의미한다.ROM

- Read Only Memory, 한번 저장된 data를 읽을 수 만 있다.

RAM

- Random Access Memory, 읽고 쓰고 할 수 있다.

BRAM

- Block RAM, FPGA에 있는 Component로 ASIC의 SRAM과 비슷한 기능을 하는 Primitive Cell이다.AMD-Block Memory

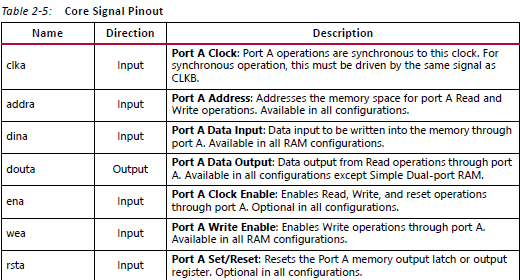

Interface(I/F) , Timing Diagram

- clk'a' : 동기화 동작을 위한 필수적인 신호

이때 'a'는 port A에서 A를 의미하기에 무시- Addr : Address는 원하는 Data 영역에 접근하기위해 사용

- din : Write 할 때 사용되는 신호 // 메모리에 Write 하고 싶은 값을 써

- dout : Read 했을 때 그 값이 출력되는 Data Port

- en : Clock Enable 신호, '1'로 set되었을때 Memory가 동작, 사용하지 않을때는 '0'으로 off / Power Saving과 연관이 있음

- we / Write Enable, '1'이면 write, '0'이면 Read

1) Address 0번지의 Data를 Read = en 신호 '1' , we 신호 '0' (read)

Address를 0으로 셋팅하면 dout에 Read Data가 올라온다.

2) Address 2번지에 Data를 Write = en 신호 '1' , we 신호 '1' (write)

Address를 2로 셋팅, din에 write하고 싶은 Data 생성