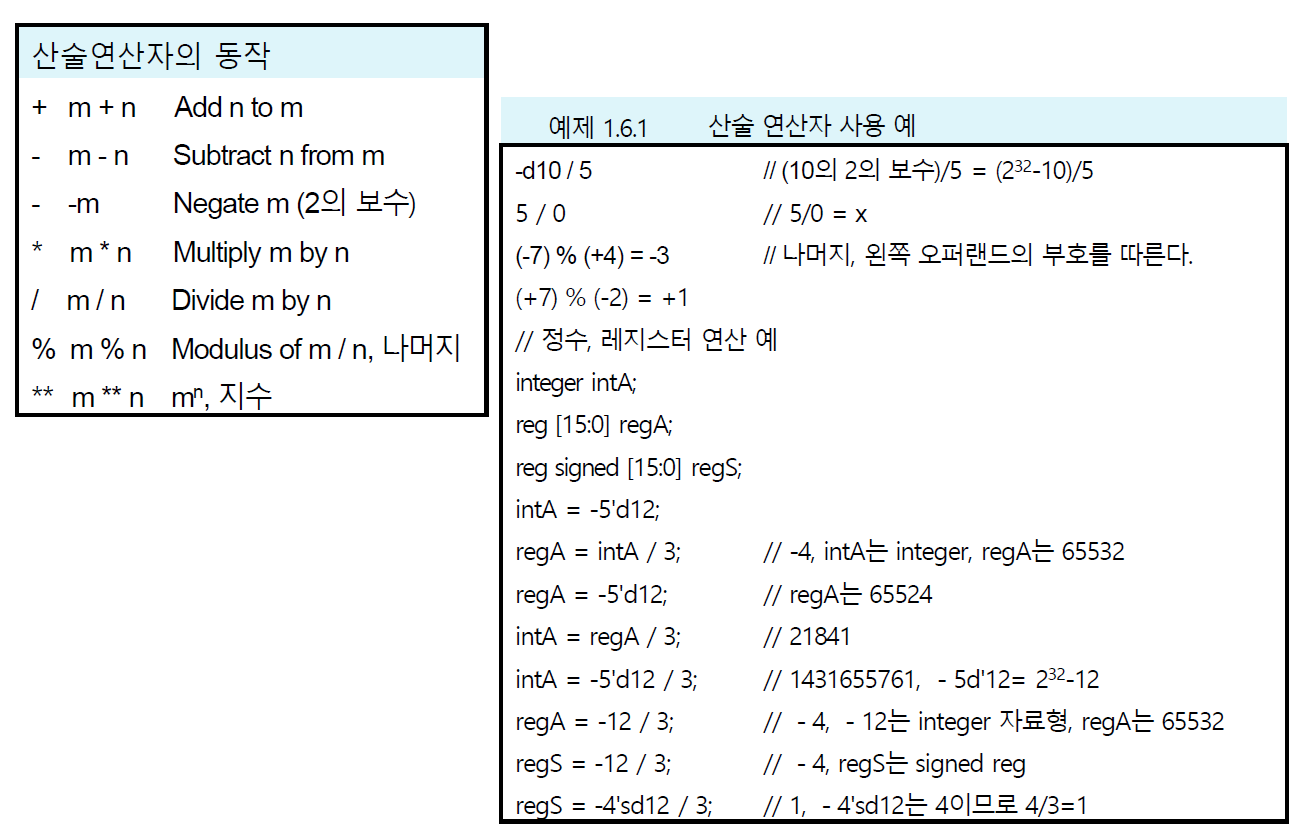

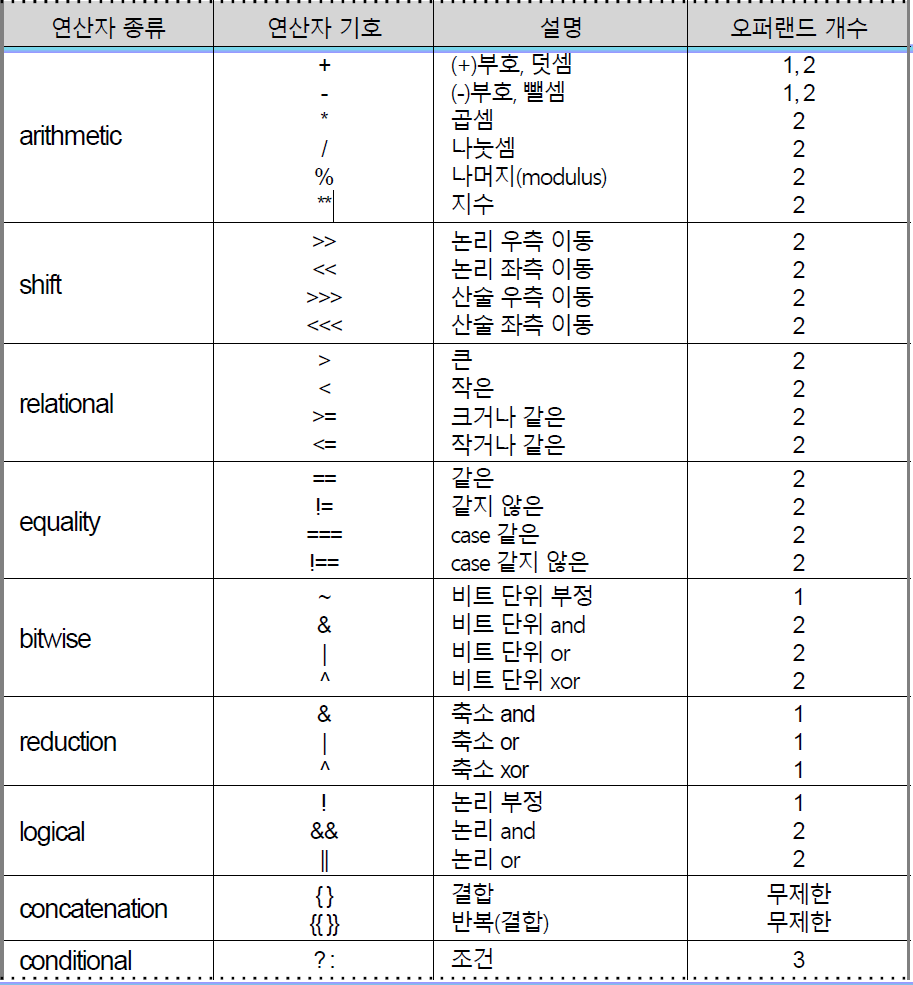

산술 연산자

피연산자의 비트에 x 나 z 가 포함된 경우, 전체 결과 값은 x

나누기와 나머지 연산자에서 두 번째 피연산자가 0인 경우, 결과값은 x

나머지 연산자의 결과 값은 첫번째 피연산자의 부호를 따름

거듭제곱 연산자에서 다음의 경우에는 결과 값이 정의되지 않음

-> 첫번째 피연산자가 0이고 두 번째 피연산자가 양수가 아닌 경우

-> 첫번째 피연산자가 음수이고 두 번째 피연산자가 정수 값이 아닌 경우ex)

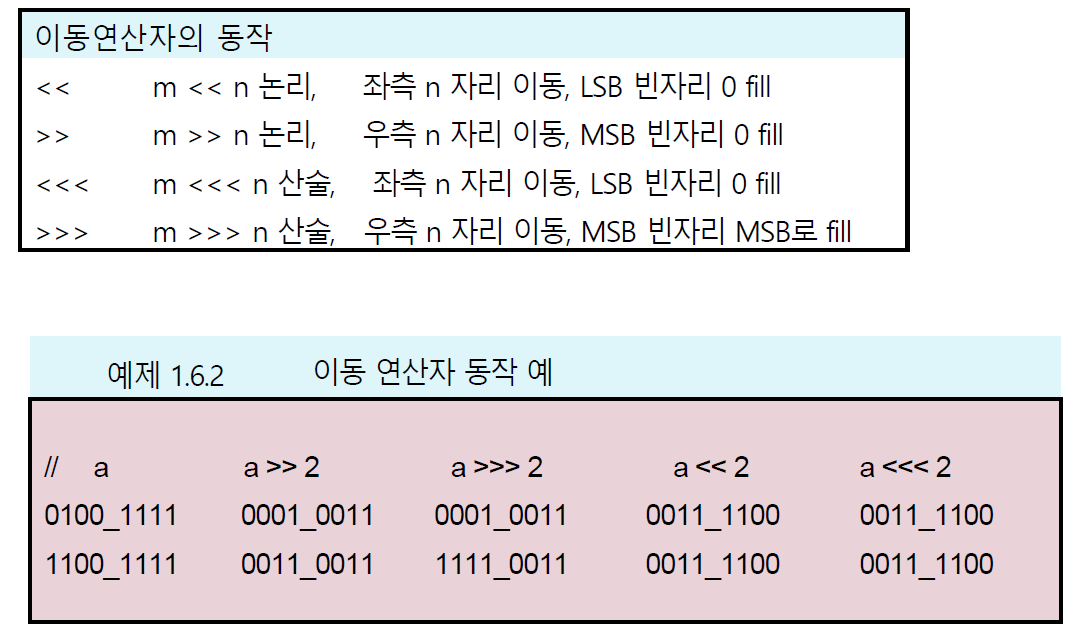

이동연산자

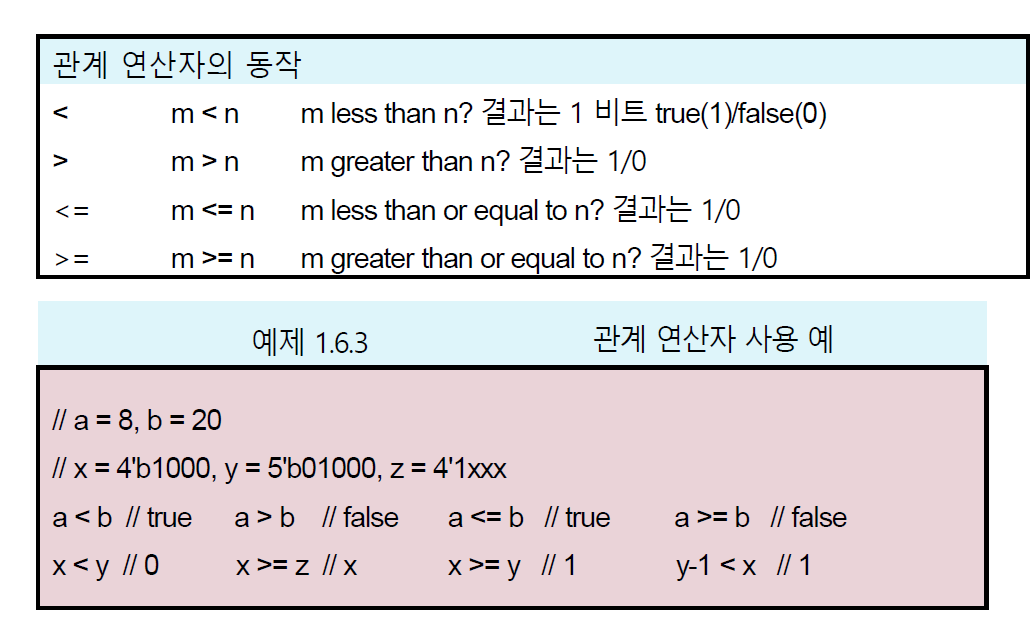

관계 연산자

오퍼랜드의 비트가 x 혹은 z의 값을 포함하면 결과 값은 1 비트의 x

-> X의 값이 모르는 값이기 때문

-> X<=Z인 경우, 참인 것처럼 보이지만 X가 연산자에 포함되므로 결과값은 X가 나옴두 오퍼랜드의 비트 수가 다른 경우에는 비트 수가 작은 오퍼랜드의 MSB 쪽에 0이 채워져 비트 수가 큰 오퍼랜드에 맞추어 판단

오퍼랜드 중 하나가 실수형이면 다른 오퍼랜드도 실수형으로 변환된 후 비교

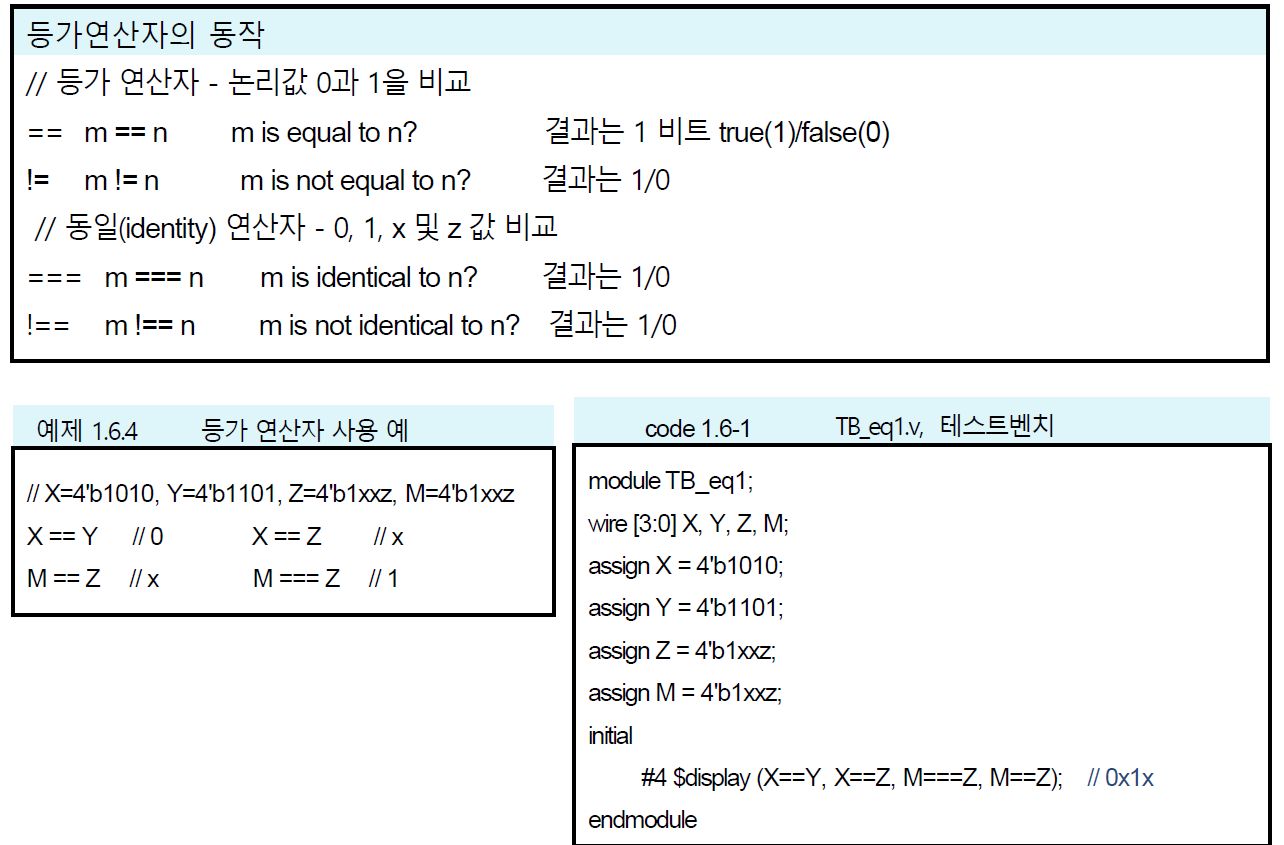

등가 연산자

등가: 내용이 같으면 등가

동일: 형태가 같아야 동일ex)

예제 1.6.4의 연산을 보면 등가와 동일의 차이점이 잘 보인다.

X와 Y의 형태는 같기 때문에 동일이지만 포함된 x의 값을 알 수 없기 때문에 내용이 다를 수 있기 때문에 등가라고는 할 수 없다

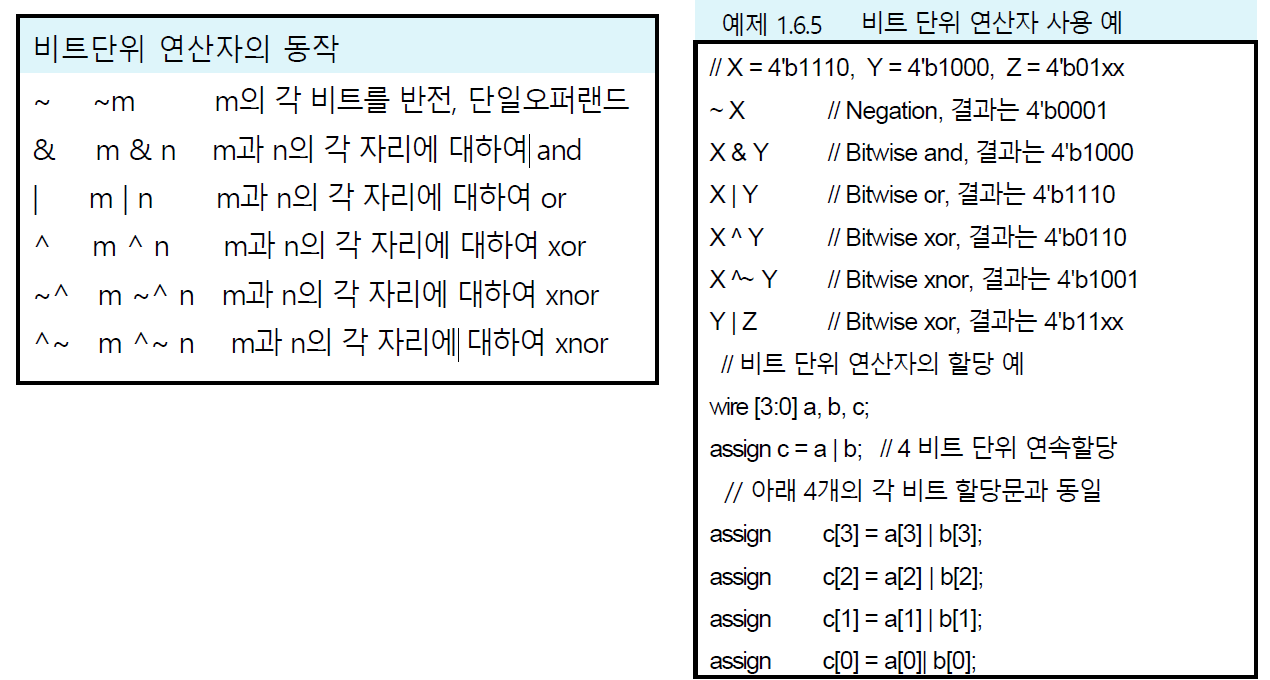

bitwise 연산자

- and, or, not, xor와 같은 논리적 연산을 비트단위별로 수행

- 오퍼랜드의 비트 수와 동일한 비트 수의 결과, 병렬합성

- 연산자를 구현하는 하드웨어는 기본적인 논리 게이트

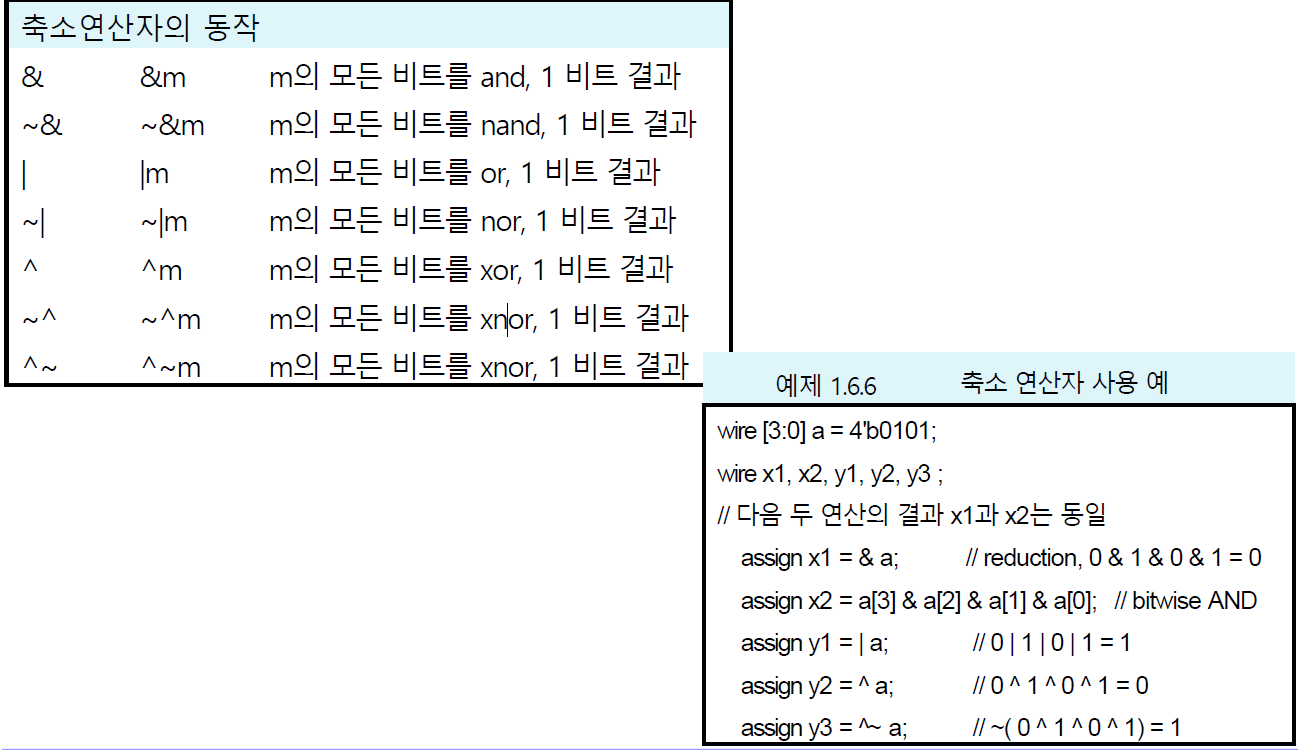

축소 연산자

- 단일 오퍼랜드에 동작, 벡터 입력에 대하여 1비트의 결과

- 입력수가 여러 개인 단일 게이트 합성

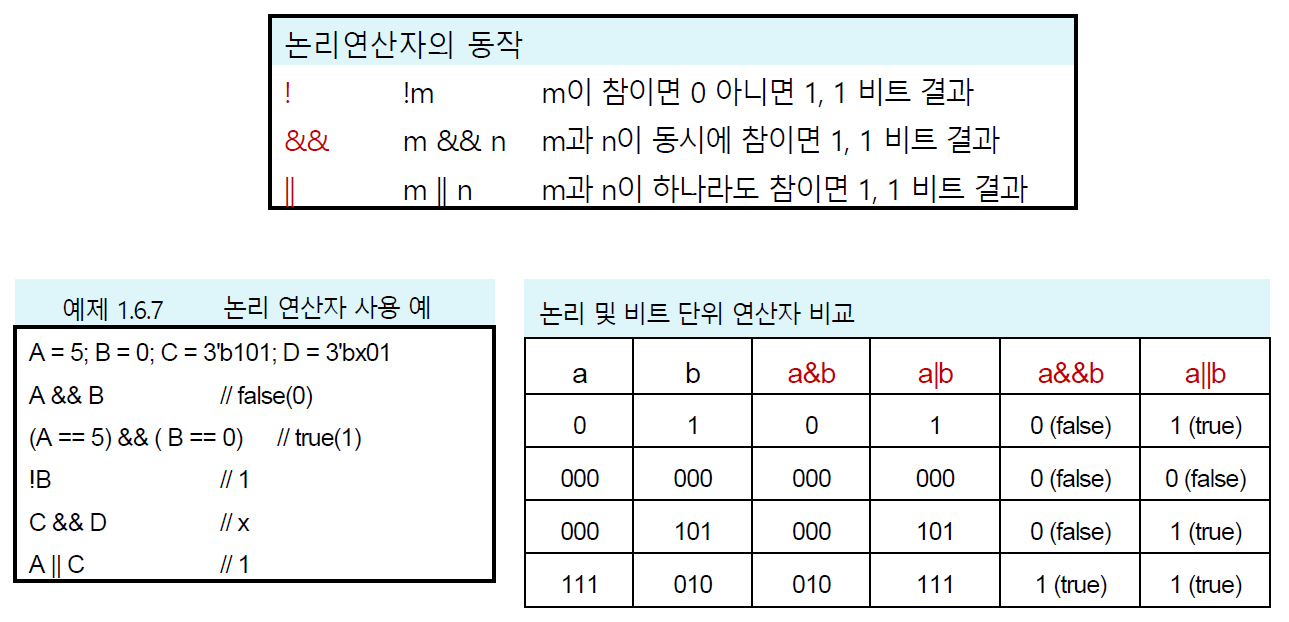

논리 연산자

- true(1) 혹은 false(0)의 1비트 평가 결과

- if, case 문 등의 조건식 판단에 주로 사용

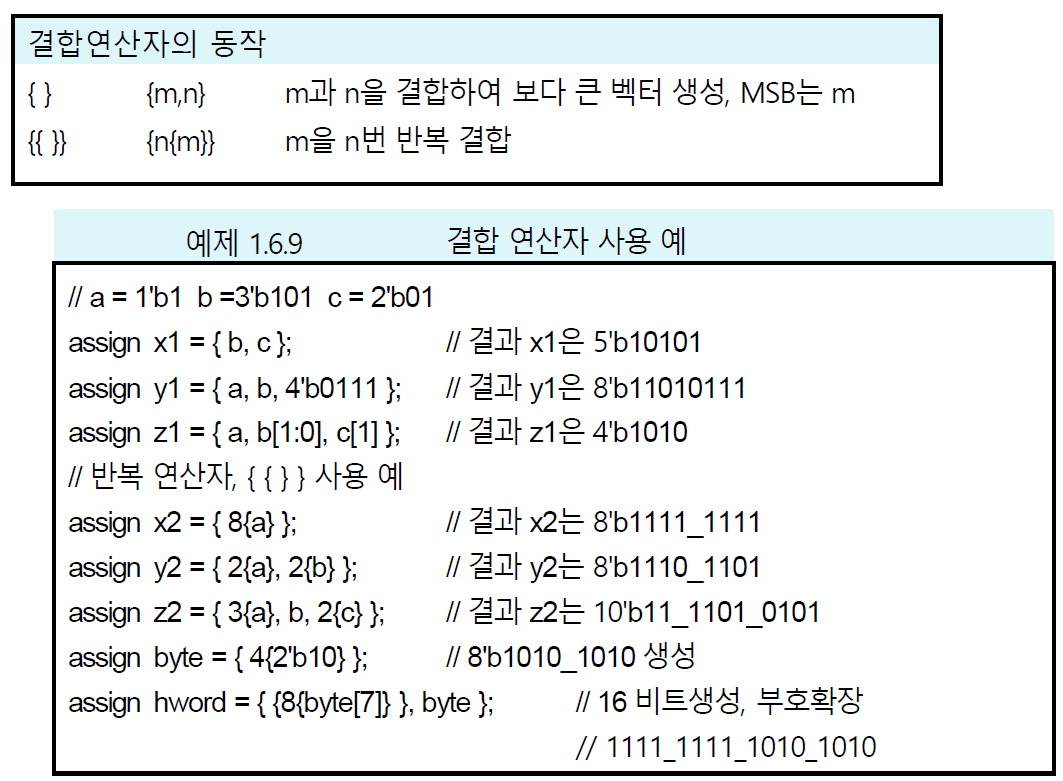

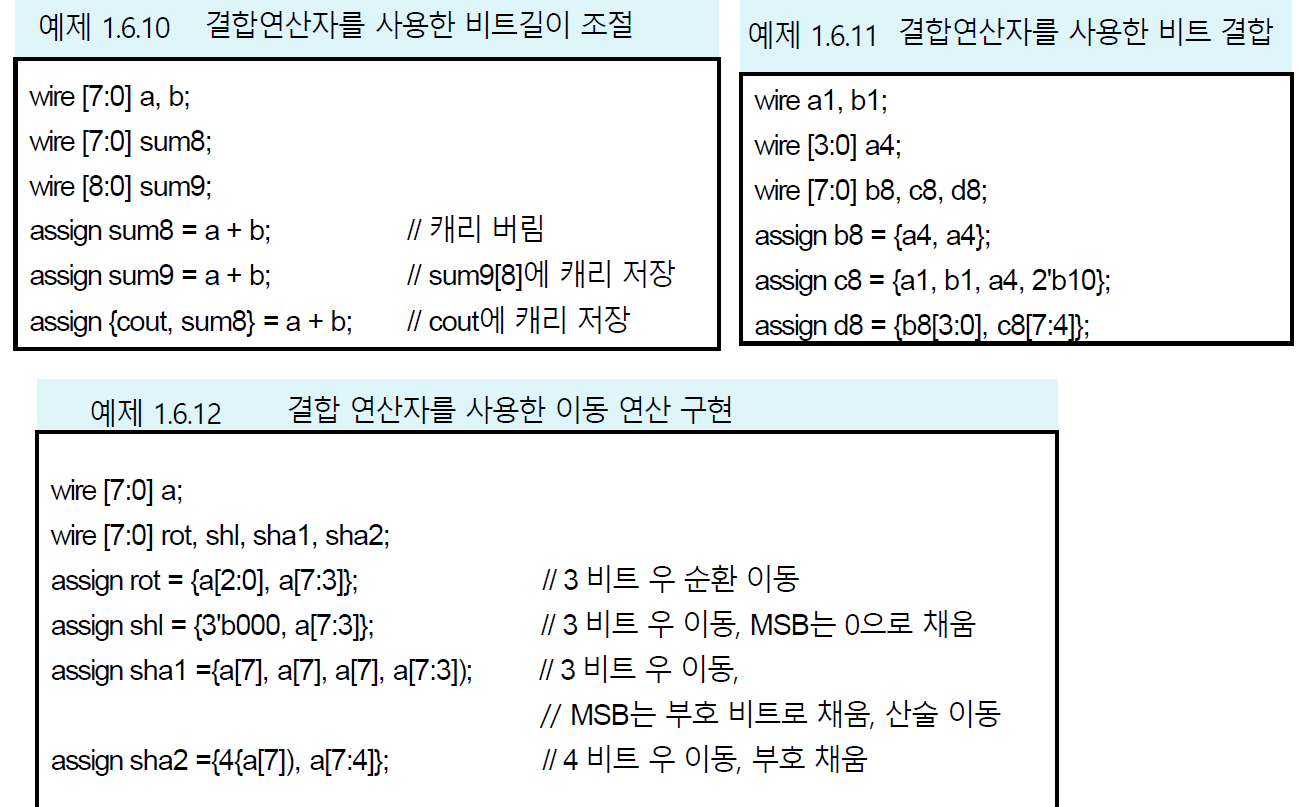

결합 연산자

- 스칼라 혹은 벡터의 구성요소를 결합하여 보다 큰 벡터 생성

-> ex)

- assign sha2 ={4{a[7]), a[7:4]};의 경우, a[7]을 4번 반복한 후, a[7:4]와 결합하라는 의미이다.

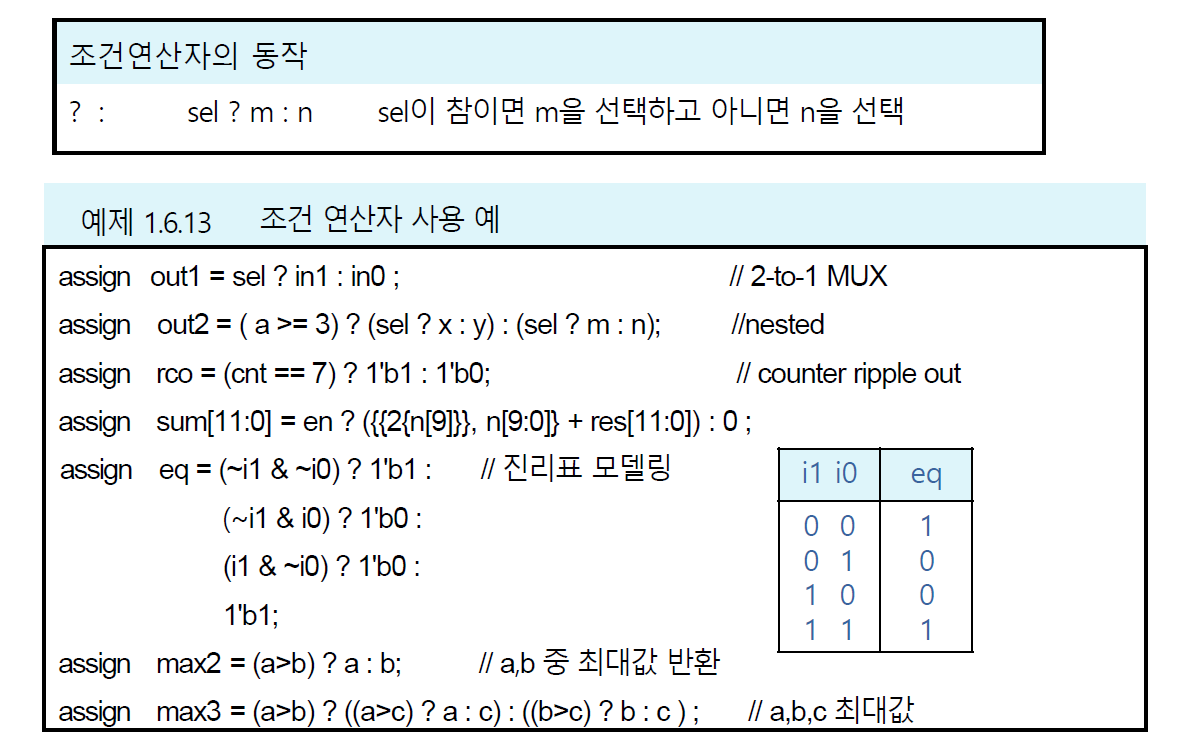

조건 연산자

- 3개의 오퍼랜드, RHS의 값을 평가하여 좌측변수에 전달

?는 :를 사이에 두고 조건이 맞으면 :앞의 값을 틀리면 뒤의 값을 변수에 할당함

-> ex)(a==1)?1:0 -> a가 1이면 1이면 a에 1을 대입하고 1이 아니면 0을 대입함

-> Mux처럼 동작

코드 최적화

eq = (~i1 & ~i0) ? 1'b1; (~i1 & i0) ? 1'b1; (i1 & ~i0) ? 1'b1; 1'b1;eq = i1^~i0;위의 두 코드는 같은 기능이다.

코딩이 어렵다면 알고있는 것으로 우선 구현한 후, 추후에 필요성을 느끼면 최적화를 하자

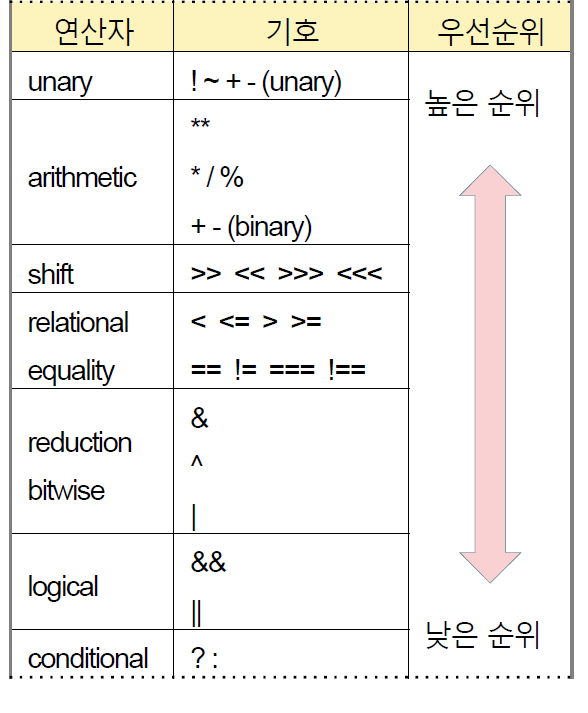

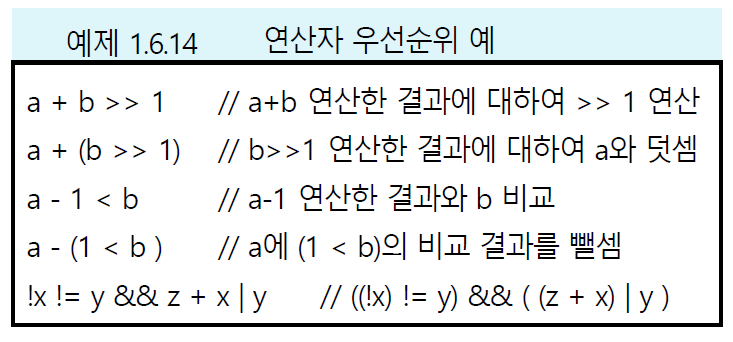

연산자 우선순위

-> ex)

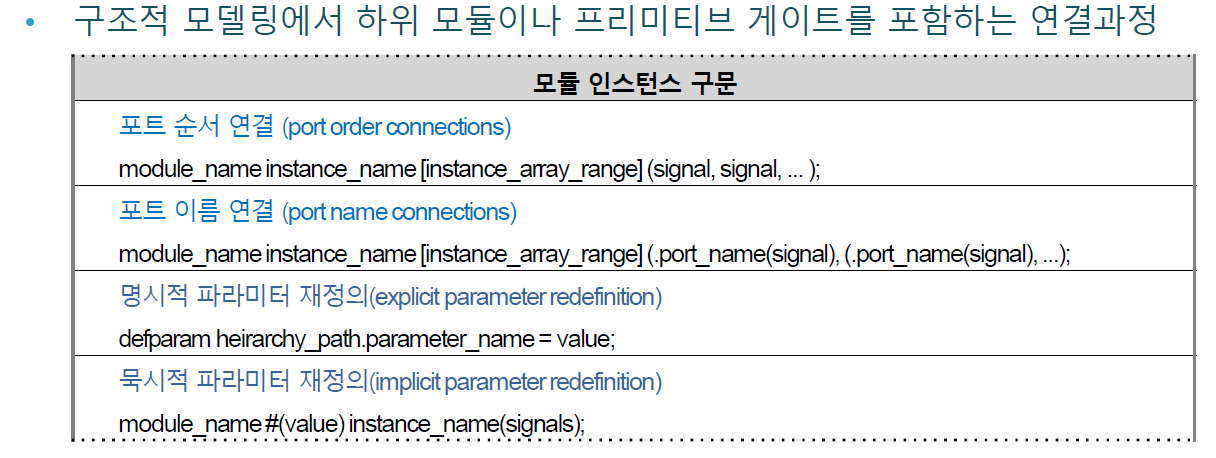

인스턴스

모듈 인스턴스

-> 이미 만들어진 것을 활용하여 구체화하는 것

-> 부품을 조립하는 것과 유사

포트 순서에 의한 연결

- 모듈정의시 사용한 포트 목록의 순서와 동일하게 신호 연결

- 연결하지 않아도 되는 포트는 두 개의 콤마 , , 사용

- 포트 정의시 사용한 순서와 신호의 크기가 일치하도록 유의

포트 이름에 의한 연결

- 포트 이름과 신호 이름을 같이 표현, 순서에 무관

- 연결이 필요하지 않는 포트는 신호 이름을 빈칸 ( )으로 남겨둔다.

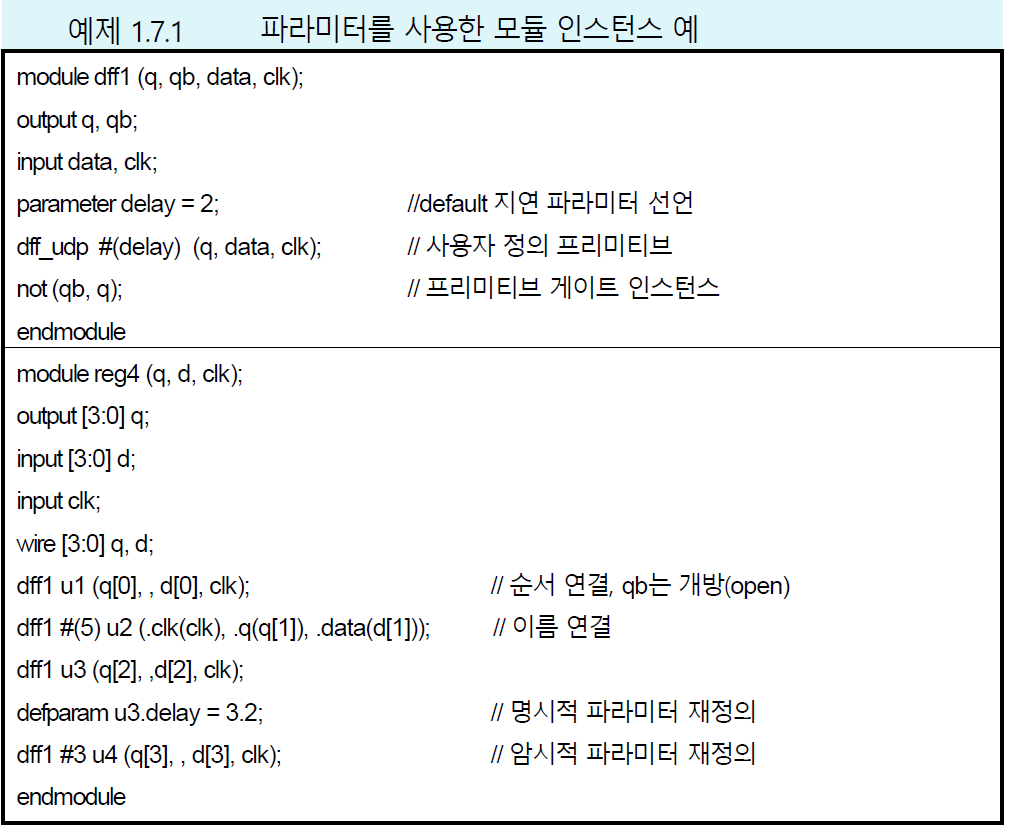

파라미터(parameter)를 포함한 인스턴스

- 명시적 파라미터 재정의

- 파라미터의 계층적 이름(hierarchical name)을 가진 defparam 문을 사용

- 묵시적 파라미터 재정의

- 모듈 사례화 시 #(value)의 형태로 사용.

- 모듈 내에서 여러 개의 파라미터가 선언되었을 때는 파라미터의 선언 순서대

로 값 지정

-> ex)

-> 이름에 의한 연결은 순서를 신경 쓸 필요 없다는 것이 가장 큰 장점이다.

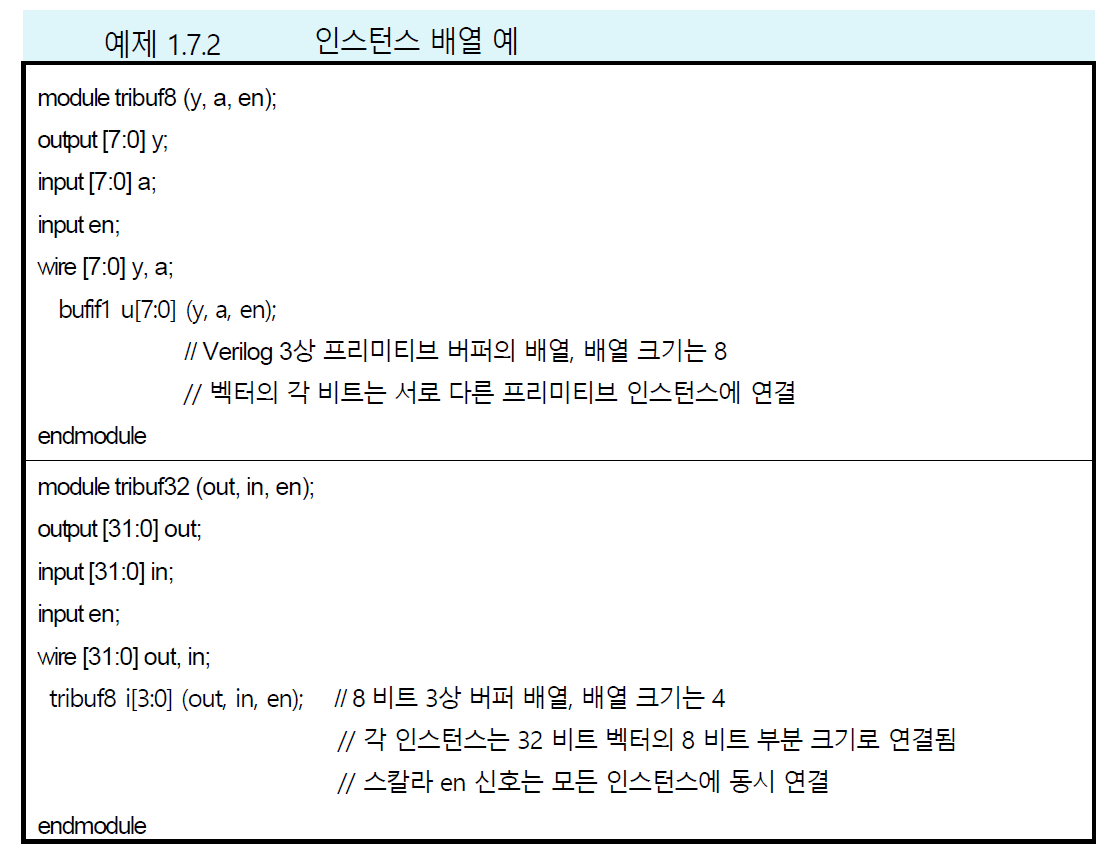

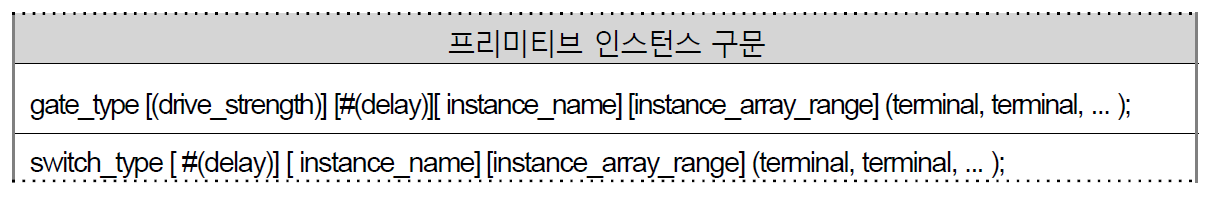

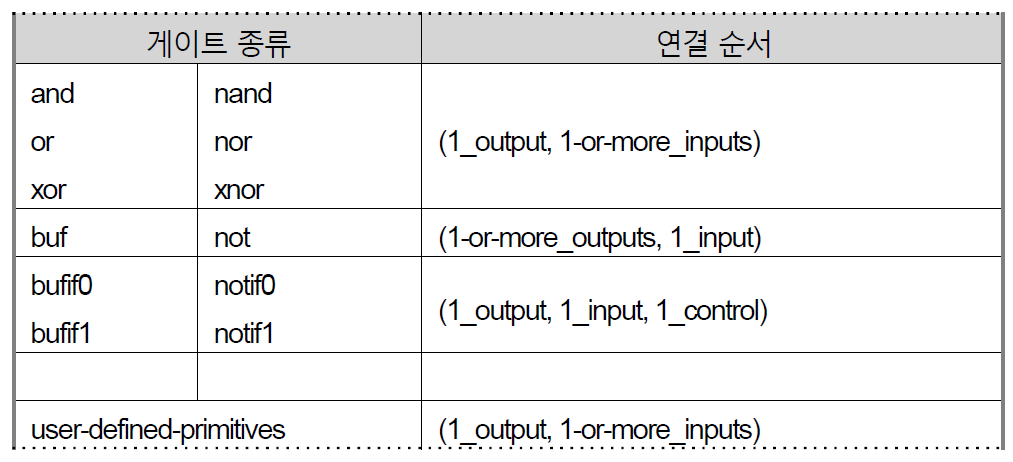

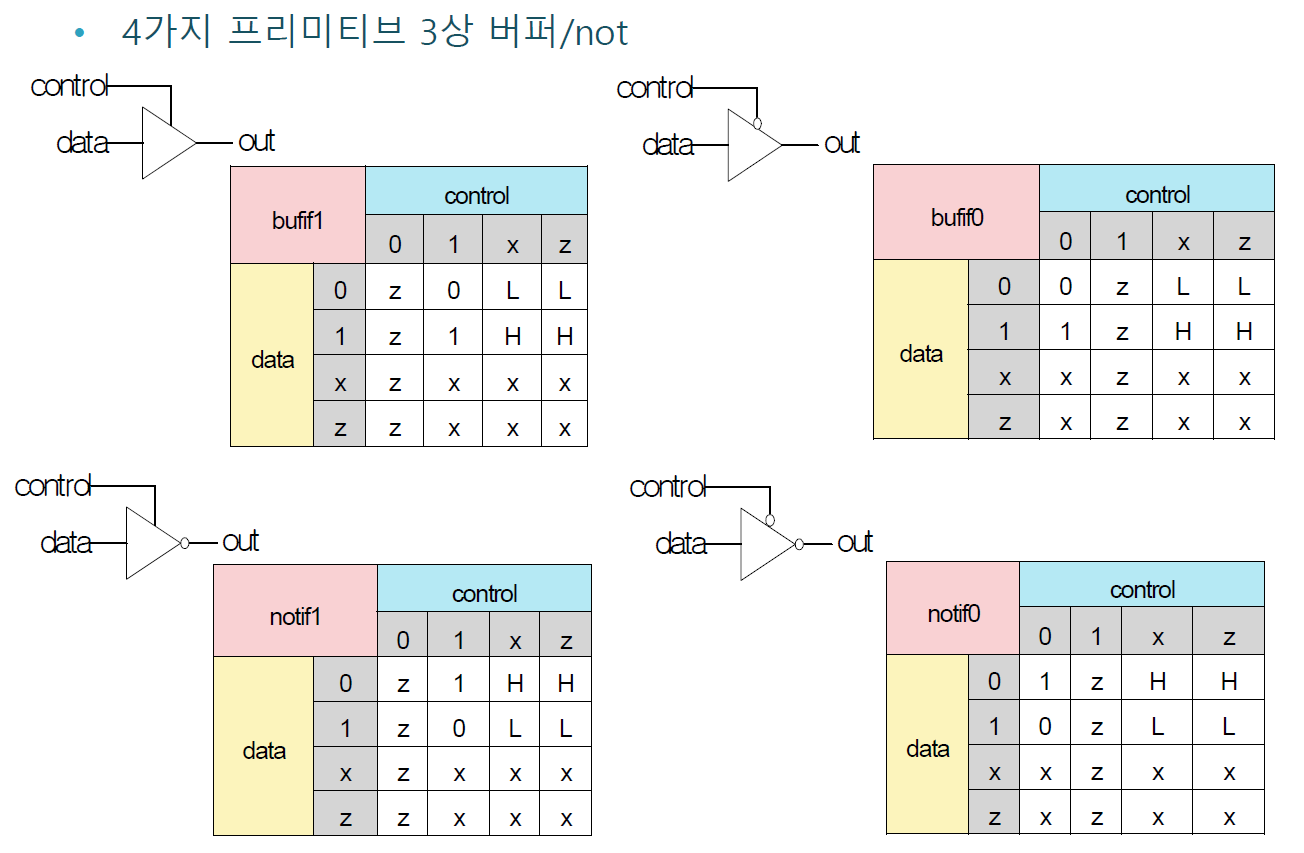

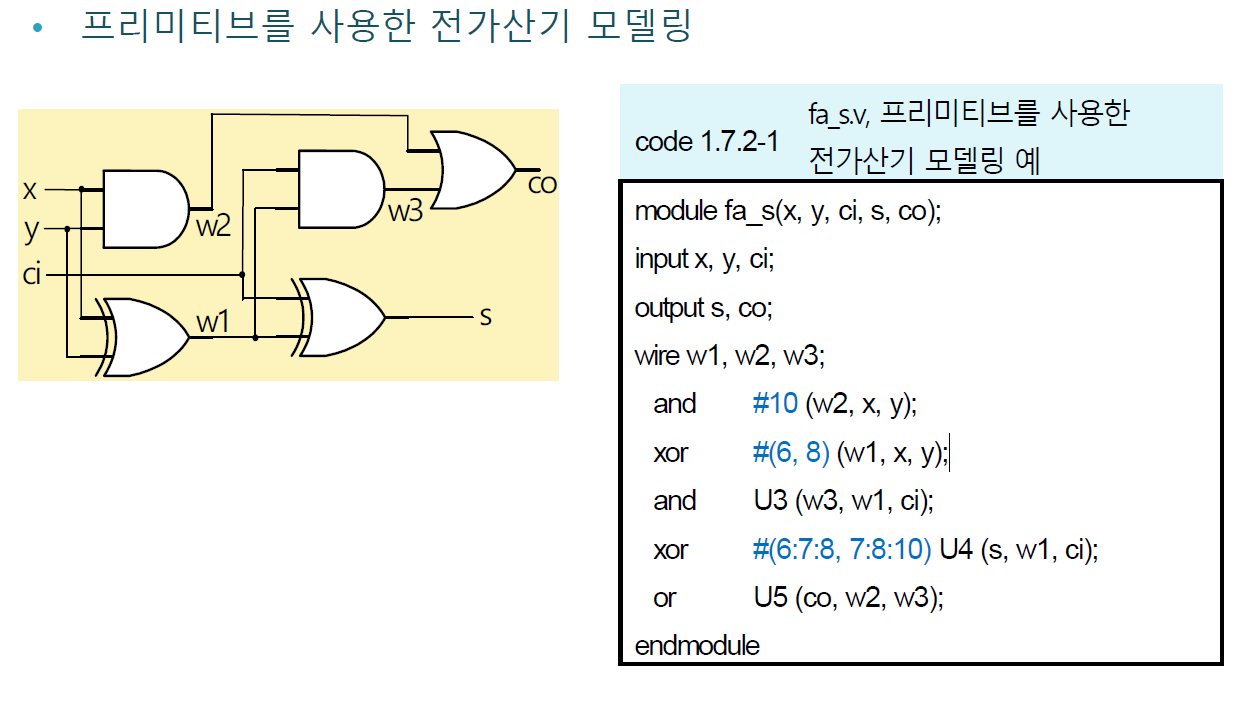

프리미티브 게이트

- Verilog에서 제공하는 프리미티브 게이트 사용

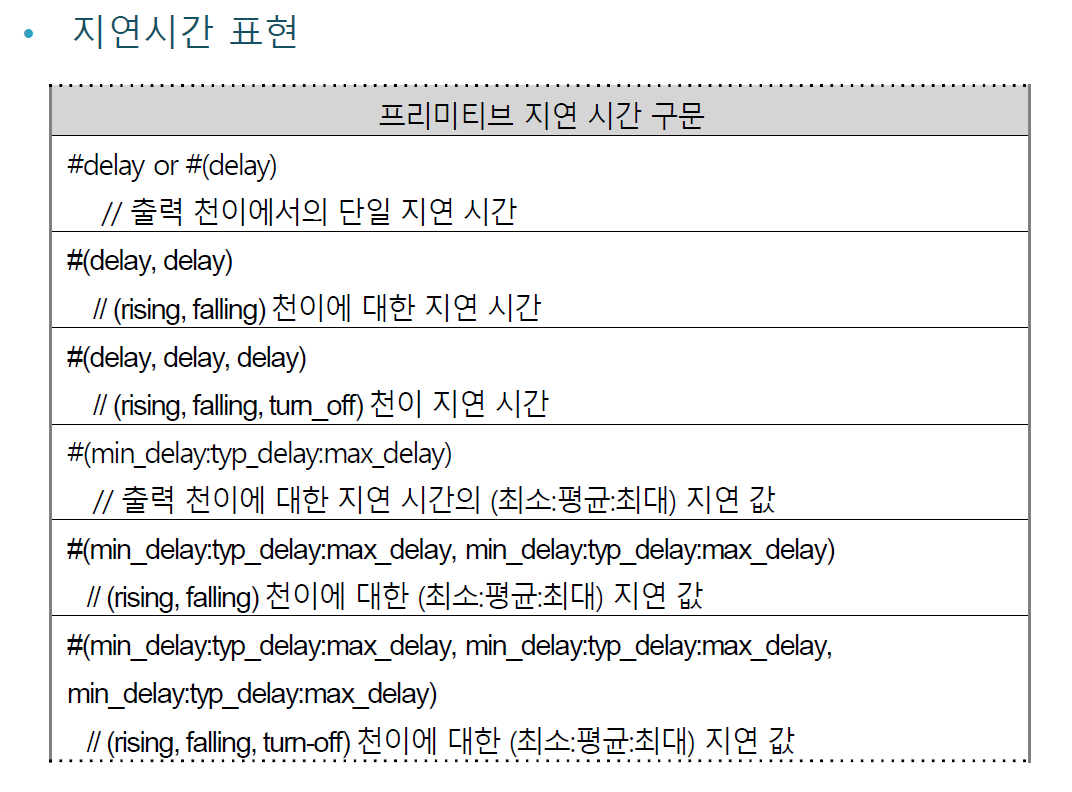

delay : 선택, 프리미티브를 통과할 때에 발생하는 전달지연 시간

-> 지연 값은 정수 혹은 실수 사용. 미정의시 default 값은 0(zero delay)

프리미티브 인스턴스에서 인스턴스 이름(instance_name)은 선택사항

-> 시뮬레이션에서 같은 프리미티브를 사용하였을 때 구분하기 위하여 인스턴스 이름을 사용할 수 있다.인스턴스 배열 범위(instance_array_range)는 선택사항

-> 다중 프리미티브를 인스턴스할 때 각 인스턴스가 벡터의 분리된 비트로 사례

- 인스턴스에서 신호연결은 순서에 의한 연결만 가능

- user-defined-primitives도 여러 입력을 받고 출력은 1개

- High Z는 회로가 Opne된 것처럼 동작

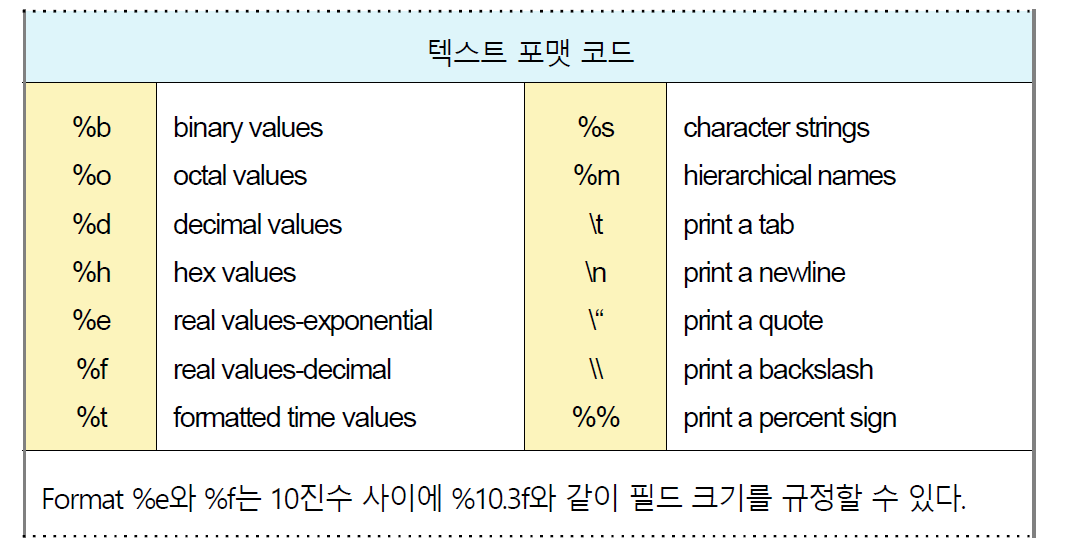

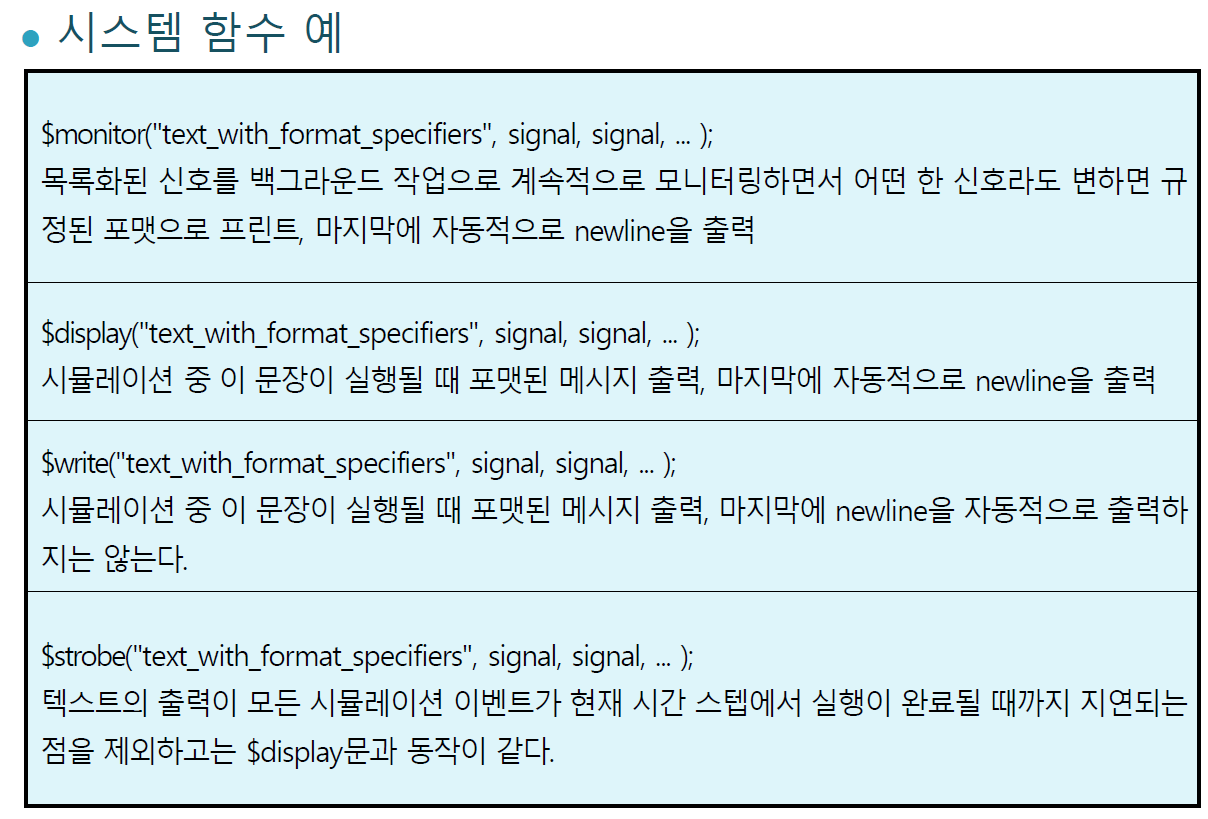

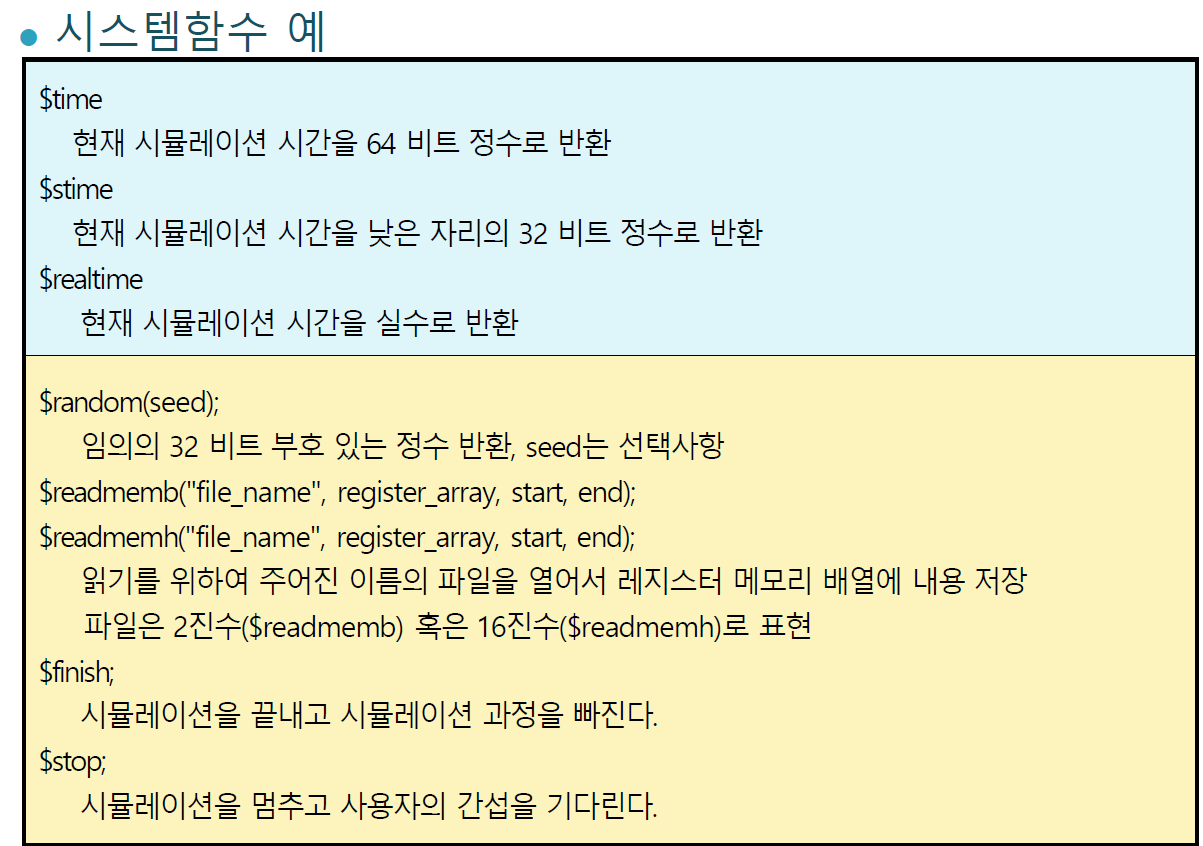

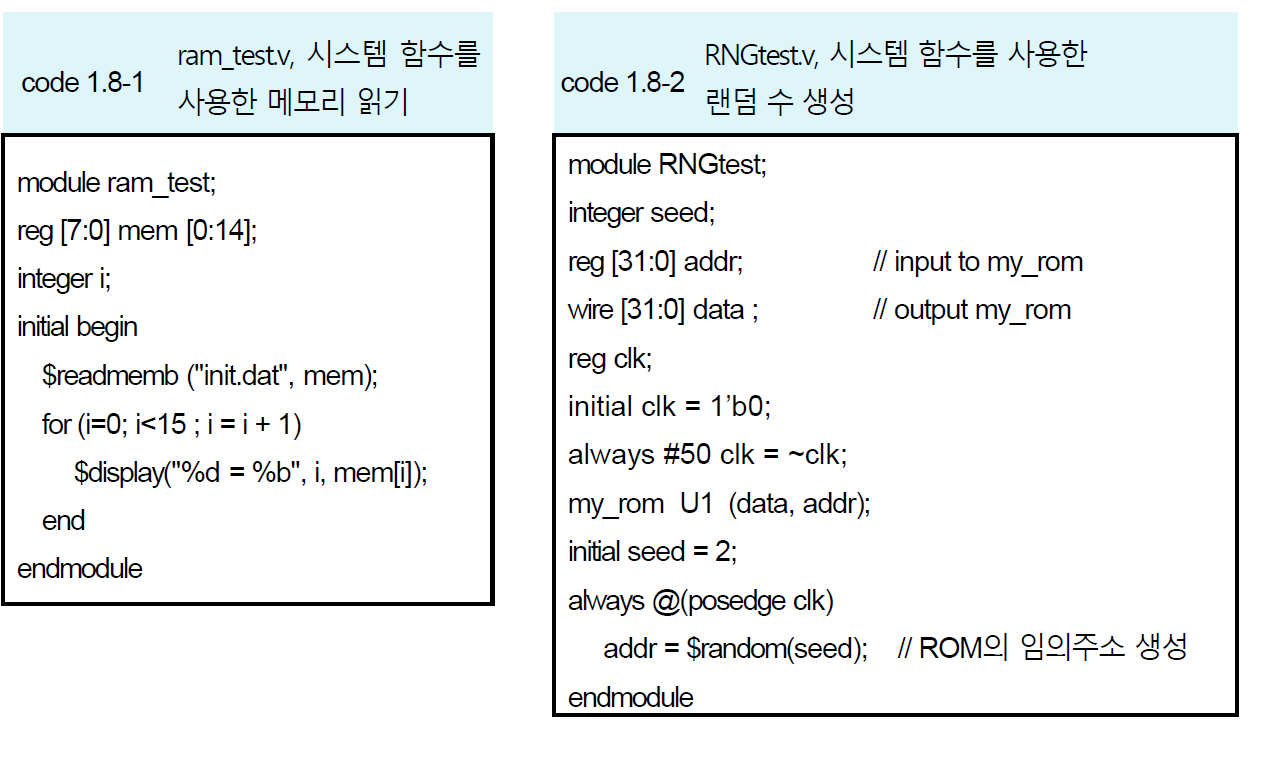

시스템 함수

Verilog를 지원하는 툴 환경에서 지원

- 시스템 태스크와 함수는 $ 부호로 시작

- 텍스트 출력이나 파형 디스플레이 등을 일반적으로 포함

-> ex)

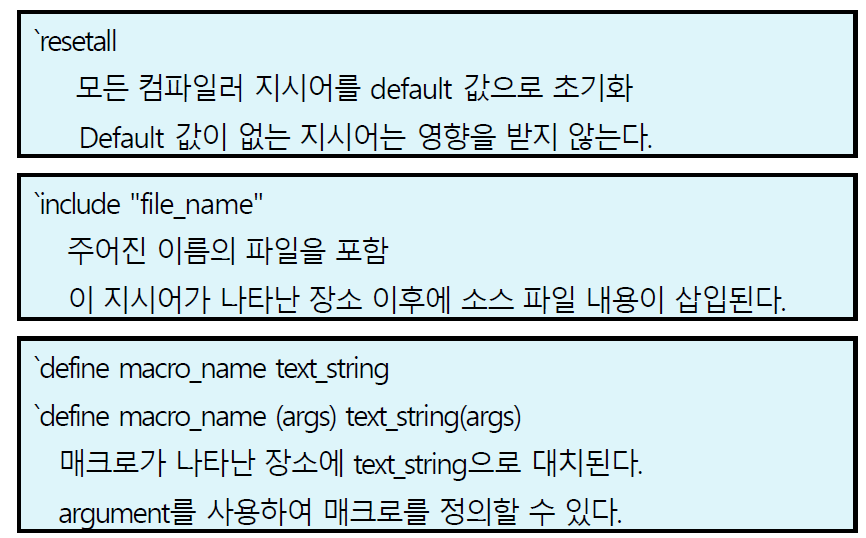

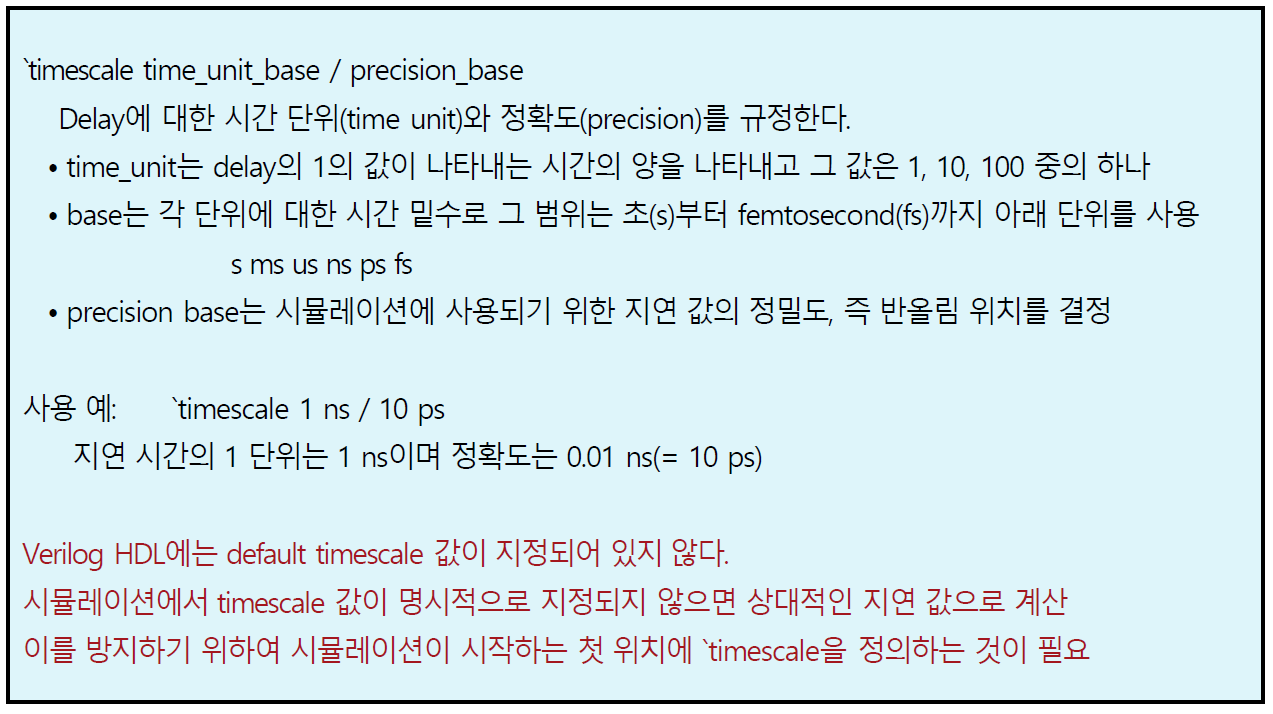

컴파일러 지시어

컴파일러 지시어(compiler directive)는 Verilog HDL 모델의 해

석을 제어하기 위한 방법으로 제공

- accent grave 문자 (`)로 시작

- Verilog HDL 구문이 아니므로 문장 끝에 ;이 없다.

- 모듈이나 Verilog의 소스 파일에 국한되지(bound) 않는다.

- 컴파일러 지시어를 툴이 만날 때 그 지시어는 다른 지시어에 의하여 수정되거나 제거될 때까지 유효하게 살아 있다.

-> 지정해주지 않으면 무슨 값이 나올자 알 수가 없다.