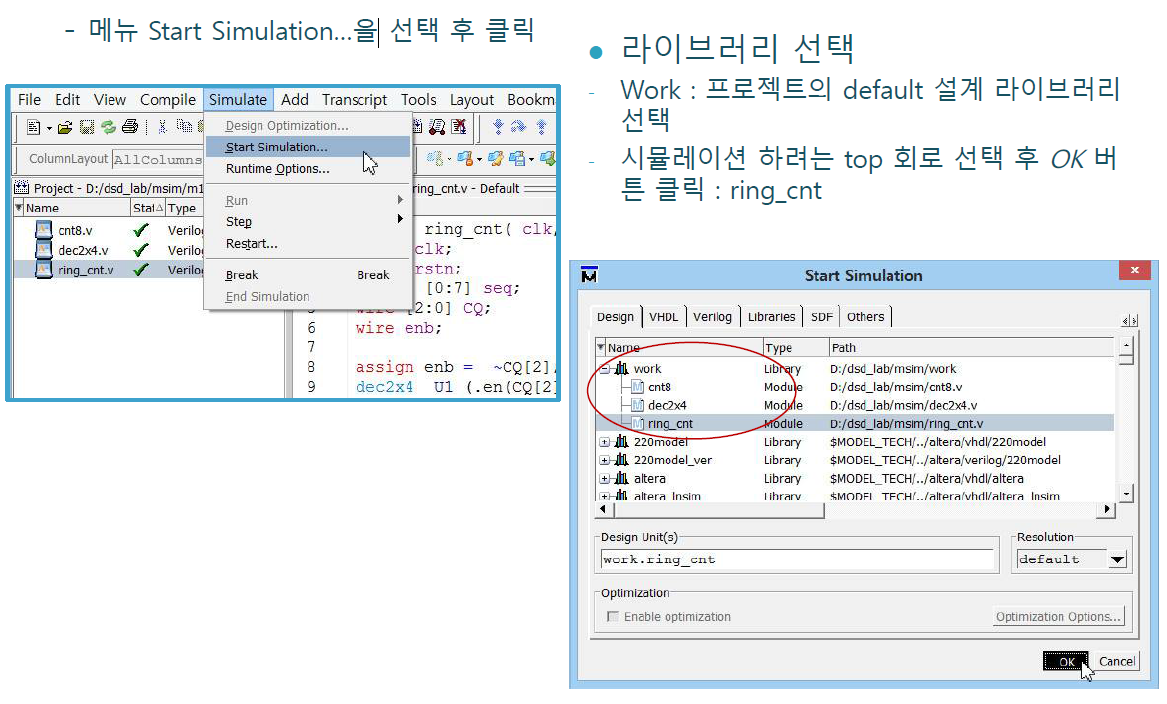

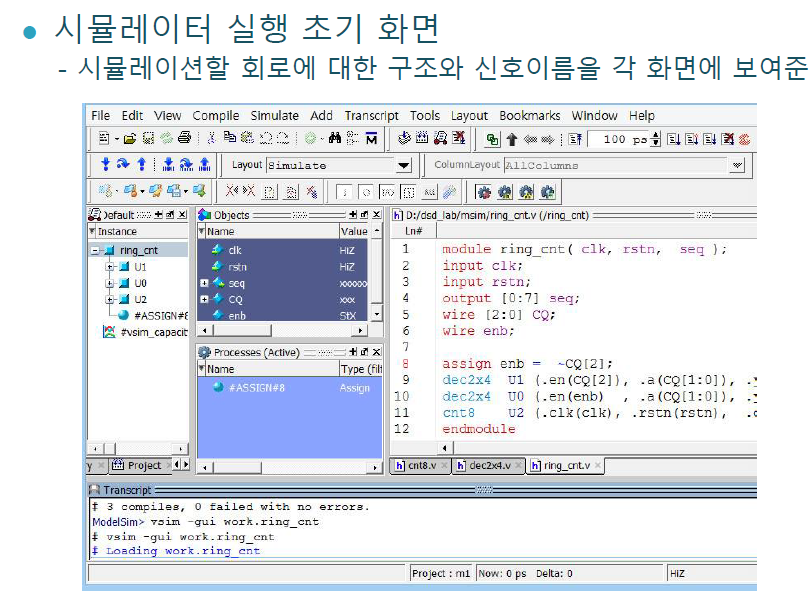

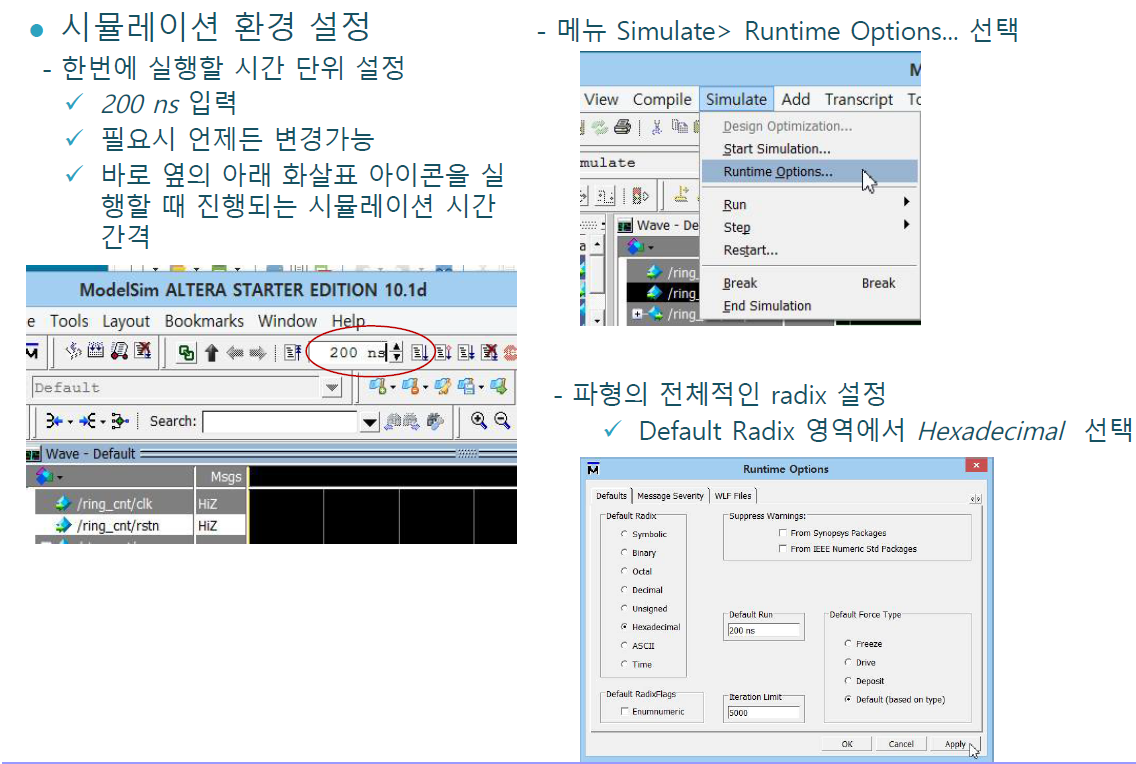

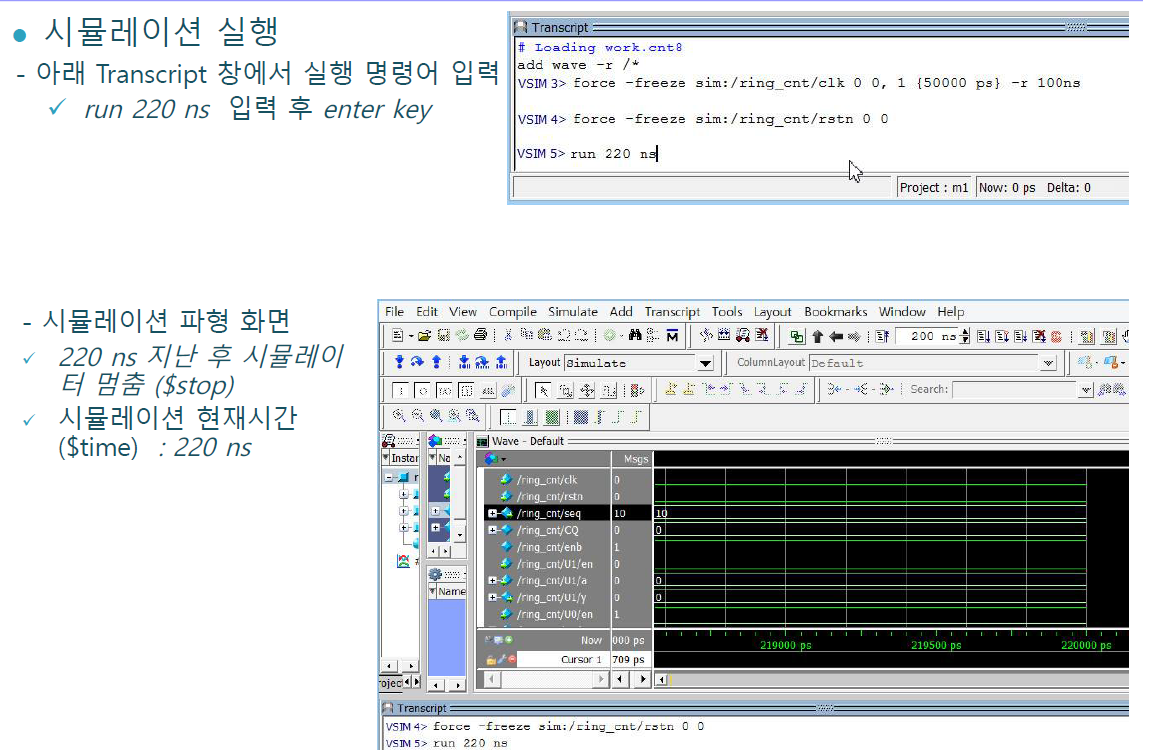

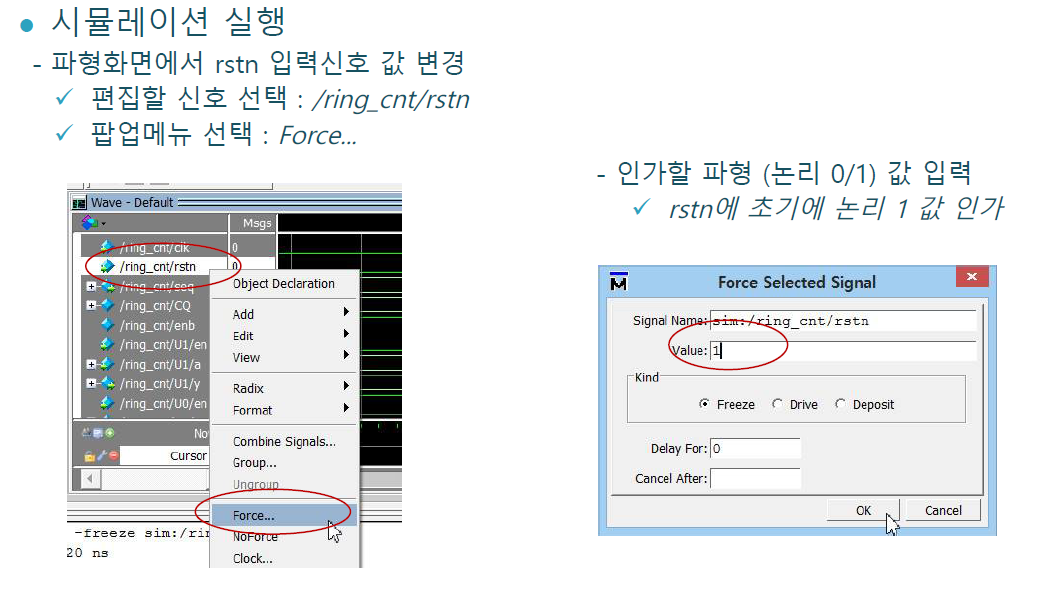

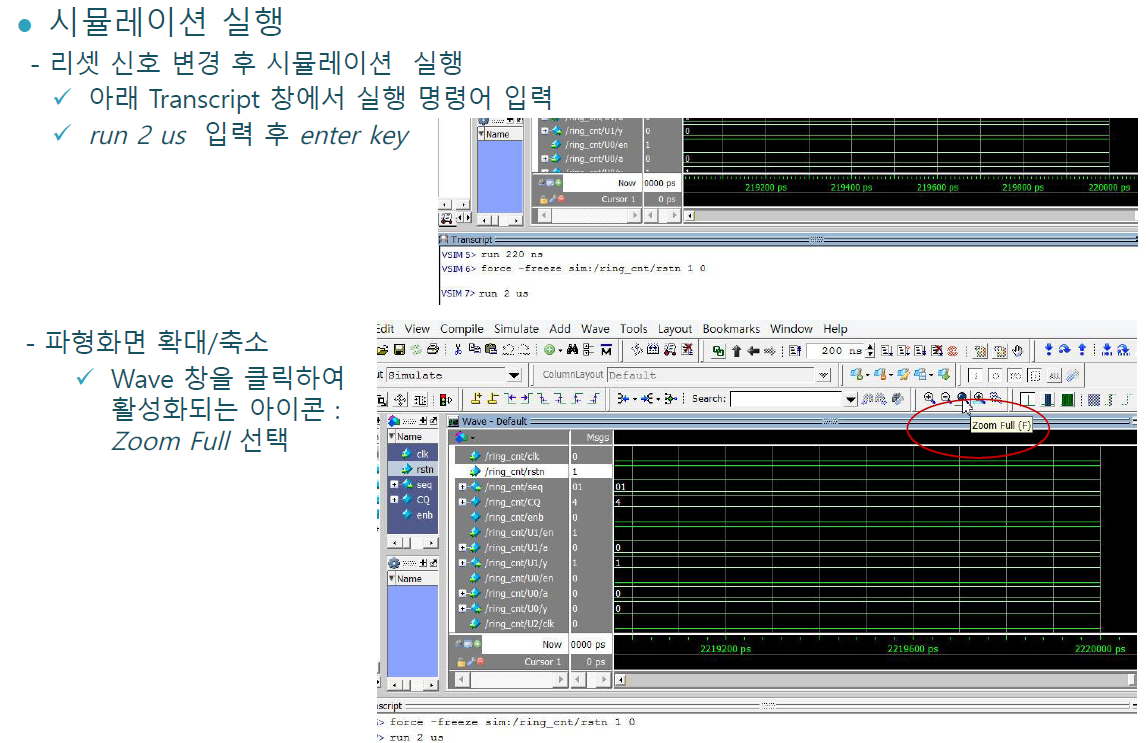

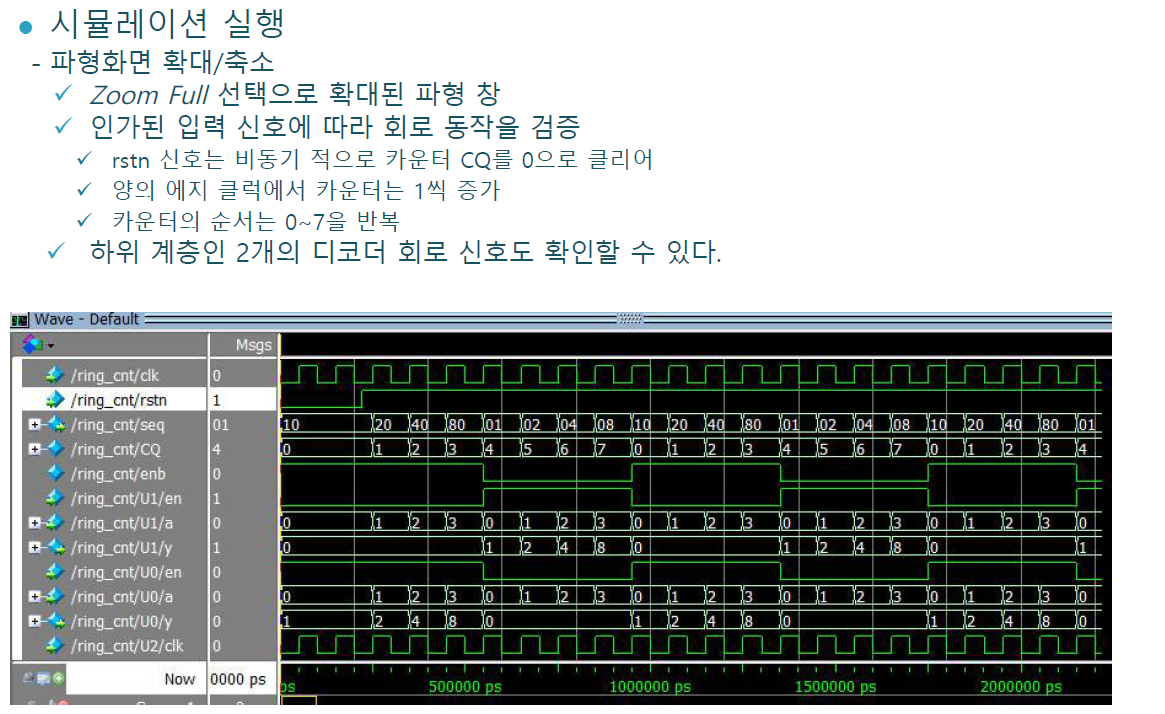

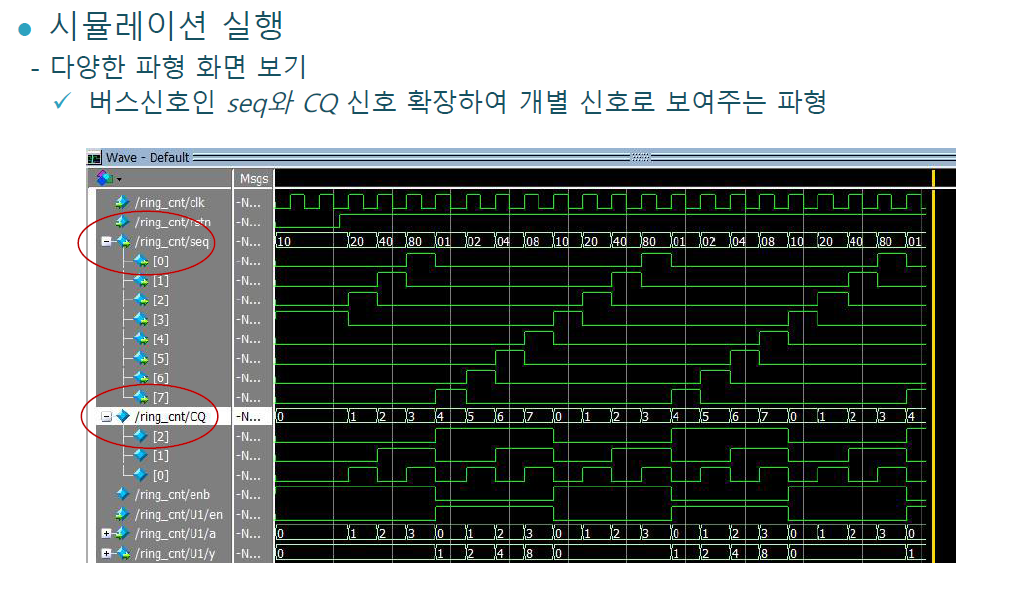

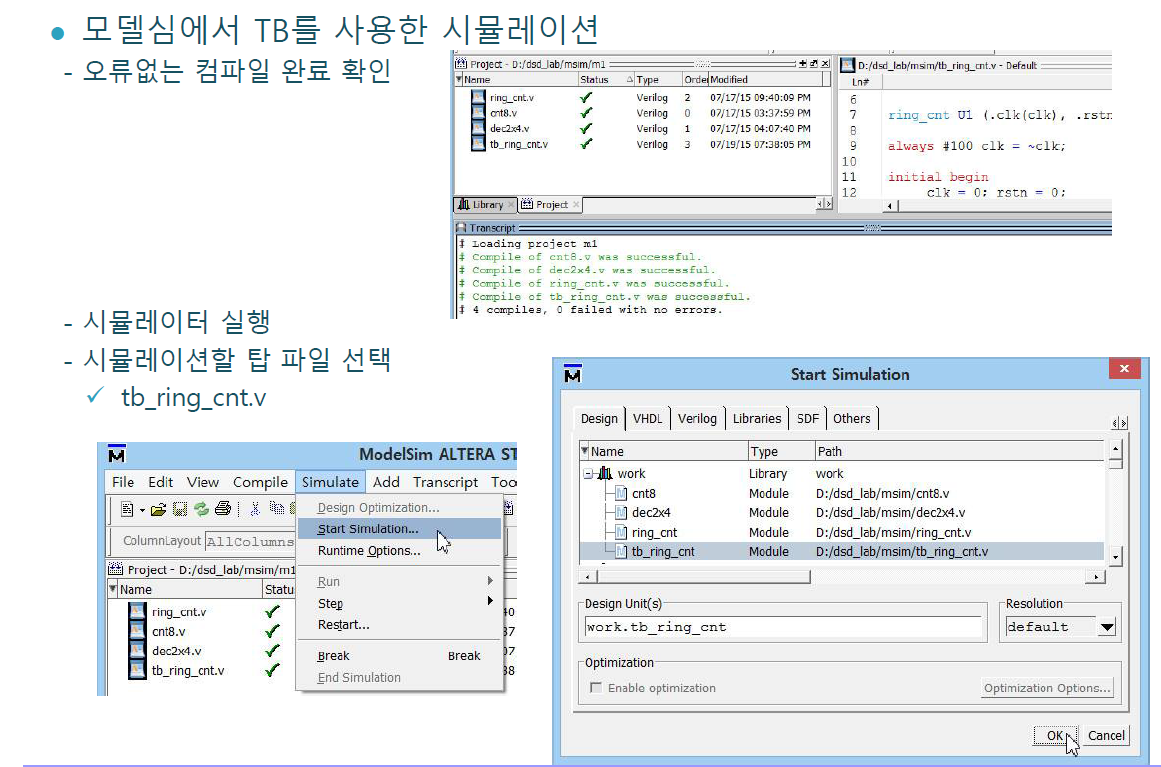

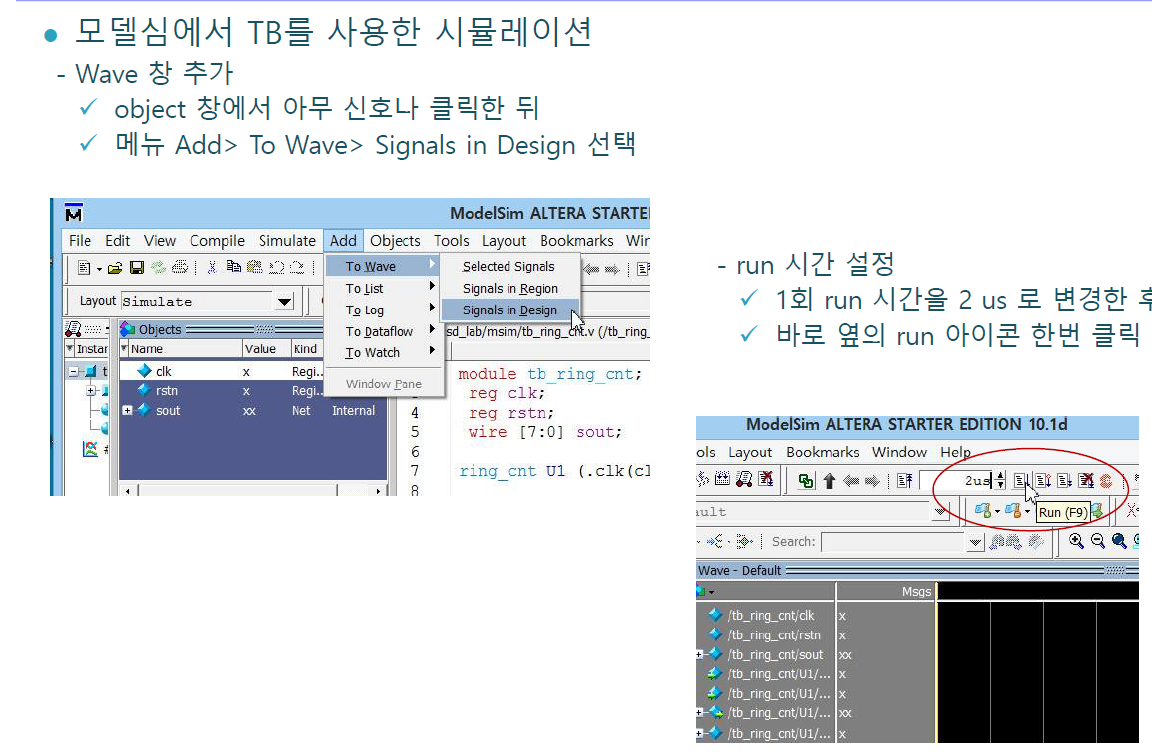

시뮬레이션 실행

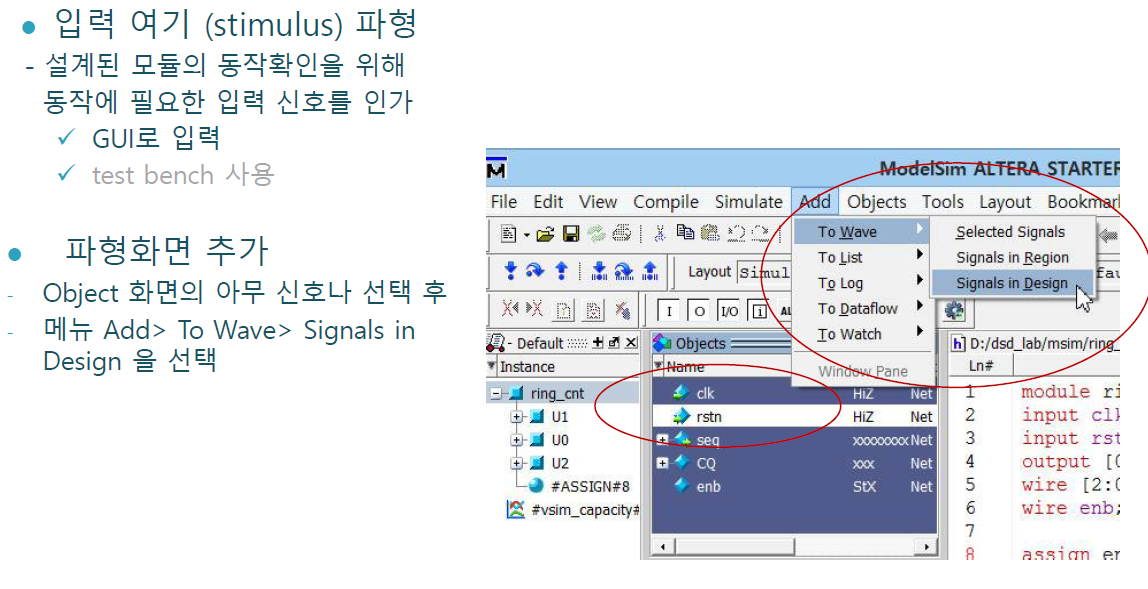

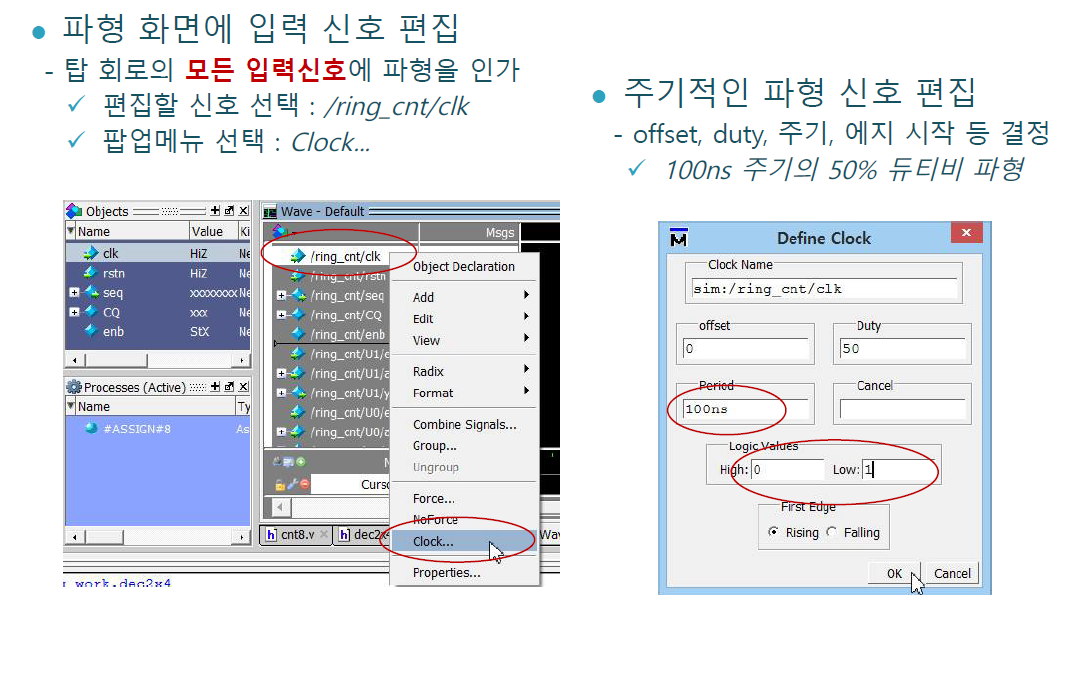

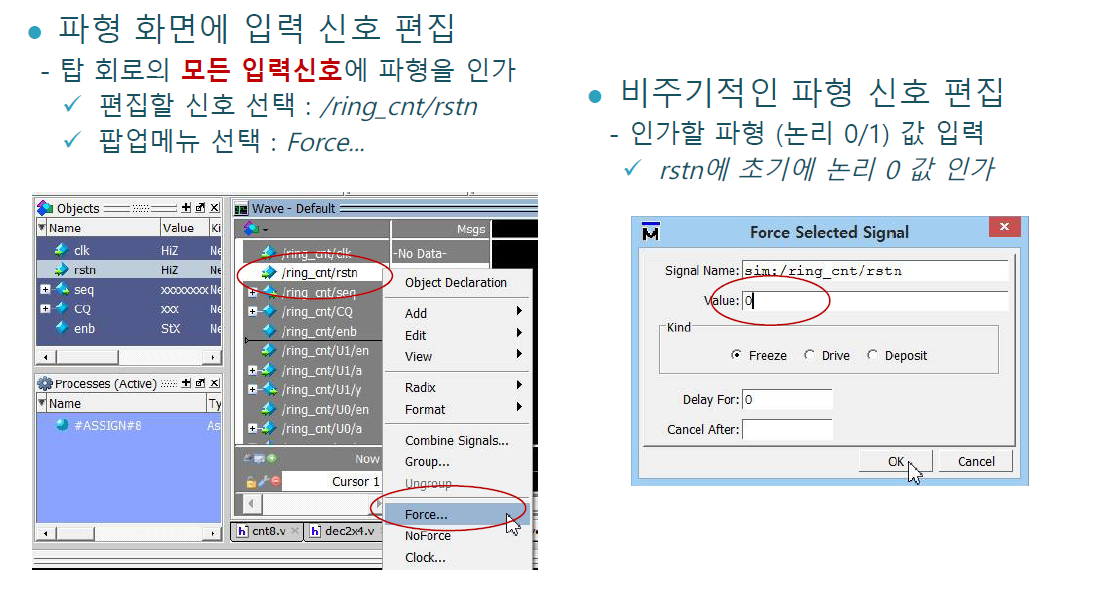

입력 simulation 파형

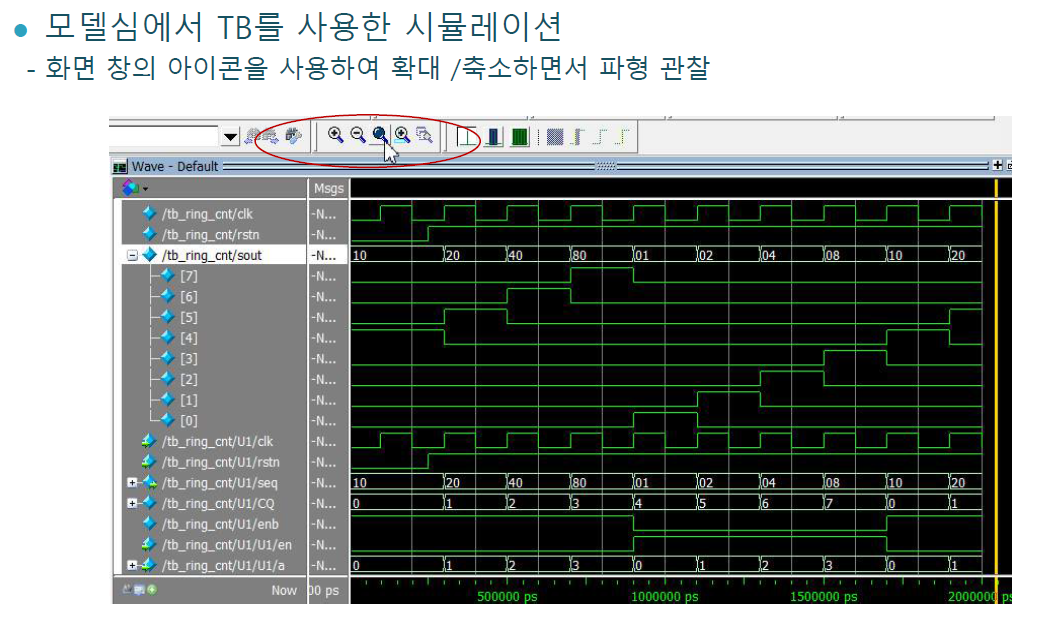

출력 파형(Waveform) 검증

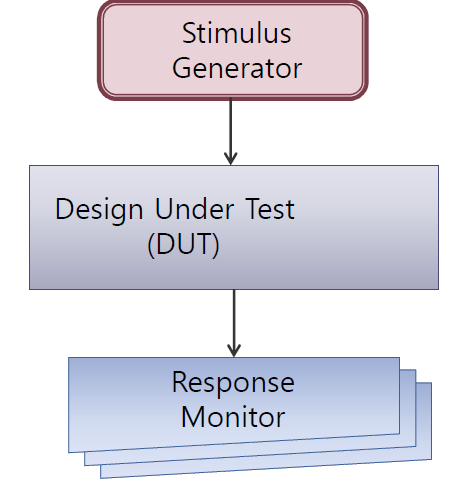

테스트 벤치(Test Bench)

테스트 벤치(Test Bench: TB)

- HDL로 설계한 회로(DUT)의 동작을 확인하기 위한 과정인 시뮬레이션을 위한 동일 HDL framework

- DUT (Design Under Test) : 하드웨어로 합성하기 위한 회로로 입력 파형이 인가되면 설계된 회로의 동작에 따라 출력이 생성되는 모듈

테스트 벤치에서는 구조적 모델링으로 인스턴스(instance)되어진다.

- 입력 stimulus : DUT의 입력 포트에 인가할 신호

- Response monitor : DUT의 출력 파형을 연결

-> 코드로 작성하거나

-> GUI로 관찰 - 합성(synthesis -> HW)과 시뮬레이션(-> SW)의 분리

- 테스트 벤치 자신의 모듈에는 입력 및 출력 포트가 없는 것이 일반적이다

테스트 벤치 구조

- DUT (Design Under Test) : 하드웨어 모듈의 인스턴스

- Stimulus Generator : 동작적 모델링으로 작성되는 파형 생성기

- Response Monitor : 출력파형으로 동작 확인

- 한 개의 Verilog 모듈로 작성

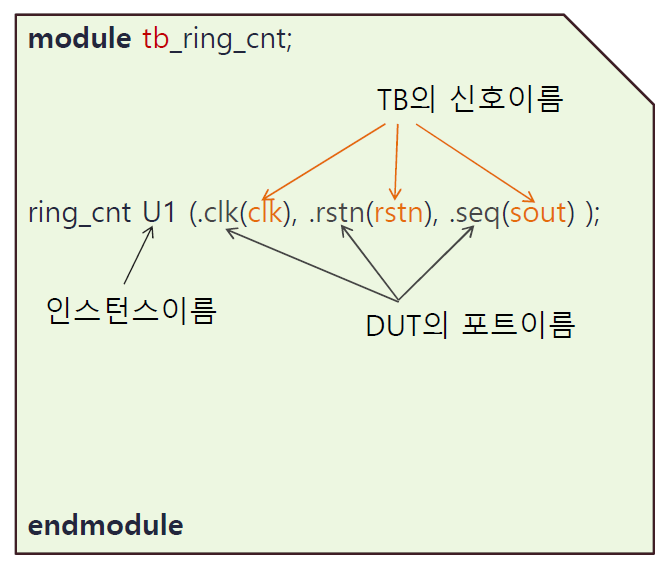

ring_cnt에 대한 TB 설계

- 모듈이름 : tb_ring_cnt

- DUT : ring_cnt 모듈 인스턴스

-> 포트와 동일한 신호이름 사용하면 편리

-> 포트연결은 순서에 의한 연결 가능

예 : ring_cnt U1 (clk, rstn, sout); - 모델심의 m1 프로젝트에서 메뉴

File> New> Source> Verilog를 선택

하여 편집기 사용

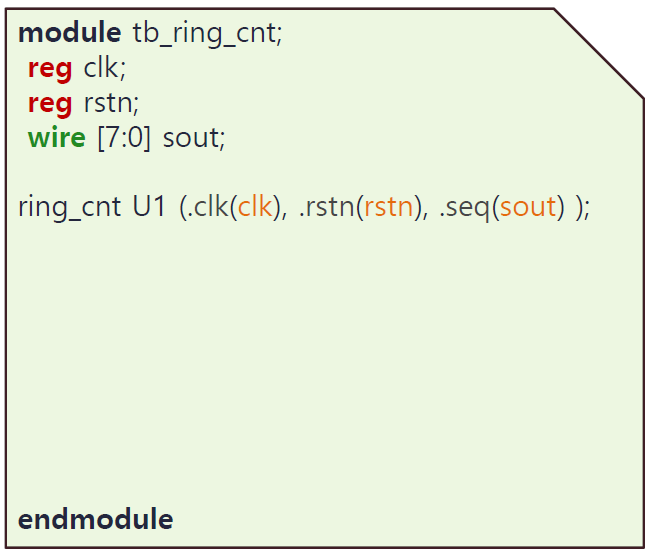

TB 신호 선언

- DUT 입력포트로 연결될 모든 신호는

reg 형으로 선언

-> stimulus 파형을 생성하여야 하는 신호 - DUT의 출력포트로 연결될 모든 신호는 wire 형으로 선언

-> 모니터를 통하여 출력으로 볼 수 있는 신호

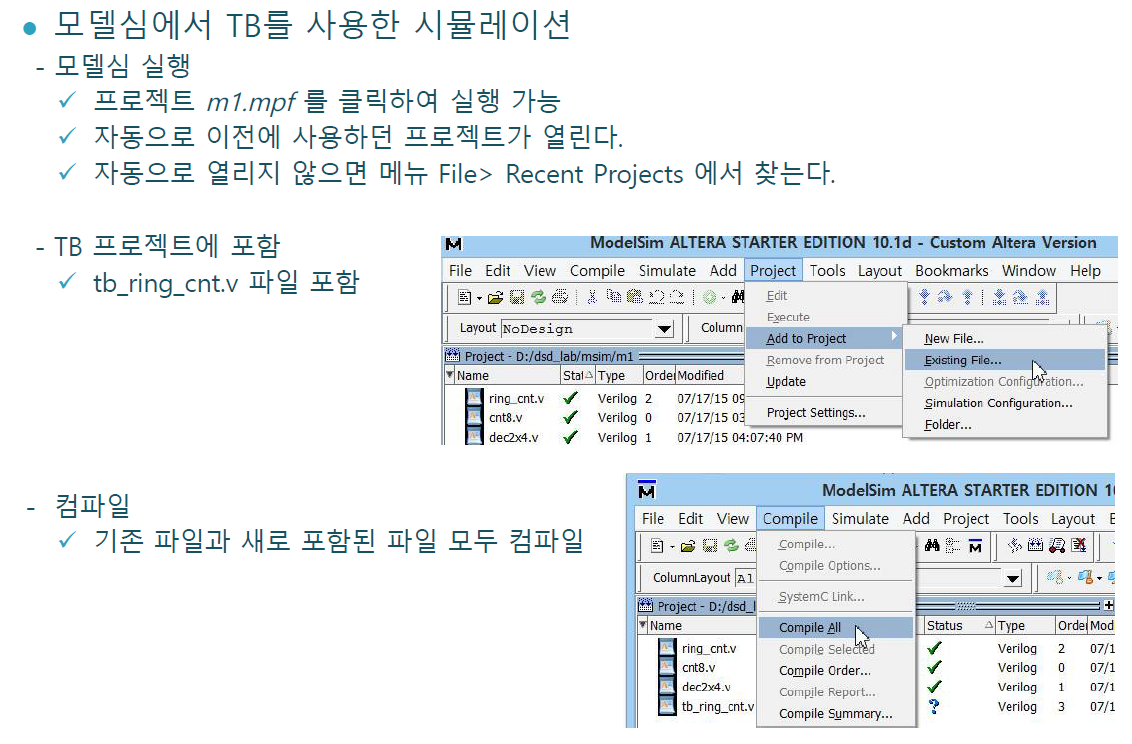

테스트 벤치 시물레이션

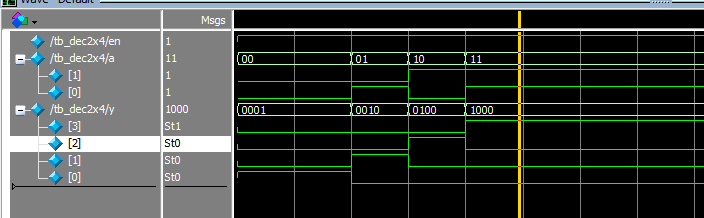

2:4 디코더의 모듈과 test bench

dec2x4.v

module dec2x4 (en, a, y);

input en;

input [1:0] a;

output [3:0] y;

wire [1:0] a;

reg[3:0] y;

always @ (en, a)

if (!en) y = 4'b0000;

else if (a==2'b00) y = 4'b0001;

else if (a==2'b01) y = 4'b0010;

else if (a==2'b10) y = 4'b0100;

else y = 4'b1000;

endmodule

tb_dec2x4.v

`timescale 1ns/1ns

module tb_dec2x4;

reg en;

reg[1:0] a;

wire [3:0]y;

dec2x4 U1 (.en(en), .a(a), .y(y));

initial

begin

en = 1;

a = 4'b0;

# 100 a = 2'b00;

# 100 a = 2'b01;

# 100 a = 2'b10;

# 100 a = 2'b11;

end

endmodule위 코드의 파형