KOCW에 공개된 영남대 최규상 교수님 컴퓨터 구조 강의를 수강 후 정리한 내용입니다.

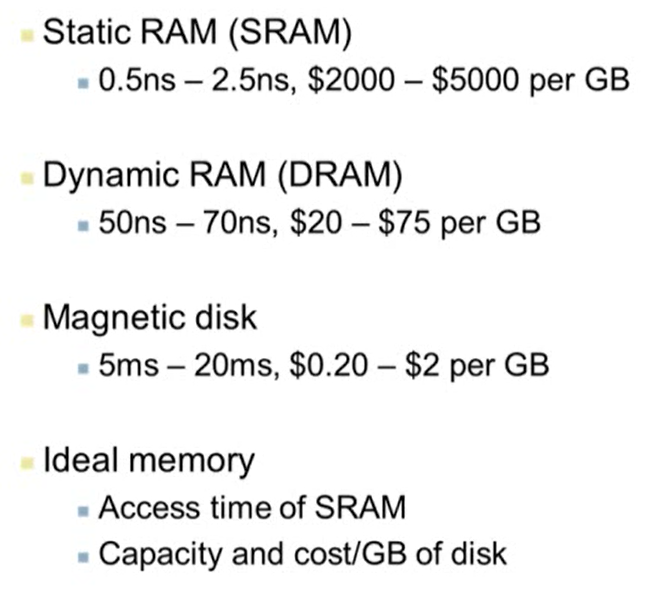

5.2 Memory Technologies

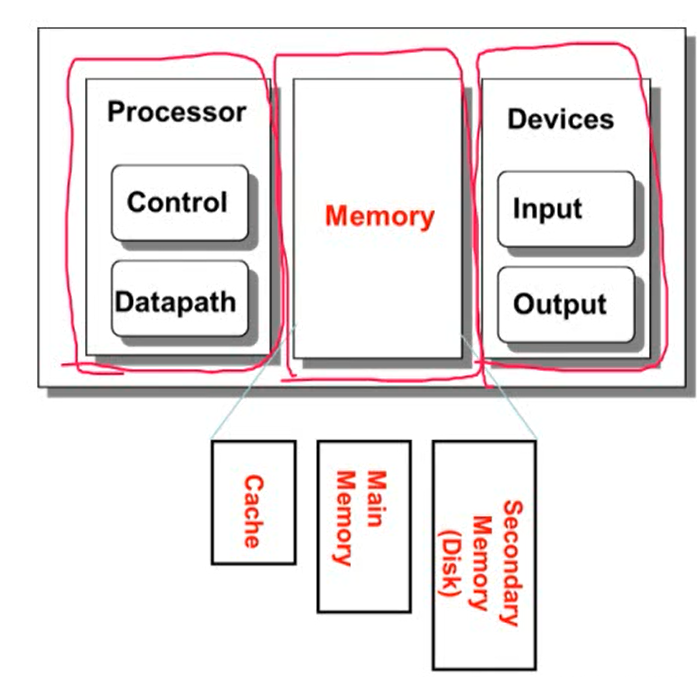

Major Components of a Computer

Memory Technology

- ROM: Read Only Memory. 비휘발성 메모리

- RAM: Ramdom Access Memory. 휘발성 메모리

- Magnetic disk = HDD

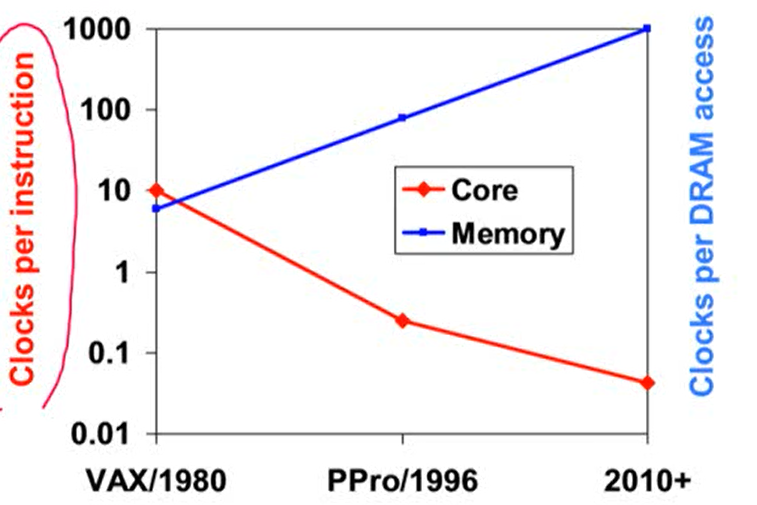

The "Memory Wall"

- 프로세서의 성능 향상 비율에 비해 DRAM의 성능 향상 비율은 느리게 증가. 이로 인해 성능 향상이 저하되는 현상

- Good memory hierarchy는 전체적인 성능에 아주 중요한 영향을 줌

5.1 Introduction

1. Principle of Locality (지역성의 원리)

- 프로그램에서 특정 시간에 메모리 주소에서 아주 적은 부분을 access하는 것

- 어떤 시간에 프로그램 전체 중에서 특정 부분만 access하는 것

- access하는 그 공간을 계속해서 access한다는 의미

1. Locality 종류

- Temporal locality

- 최근에 access한 item를 가까운 시간 내에 다시 access할 확률이 높다 (시간적인 의미)

- ex) loop 안의 명령어, induction variables

- Spatial locality

- 최근에 access한 item의 근처에 있는 다른 item을 access할 확률이 높다 (공간적인 의미)

- sequential instruction access

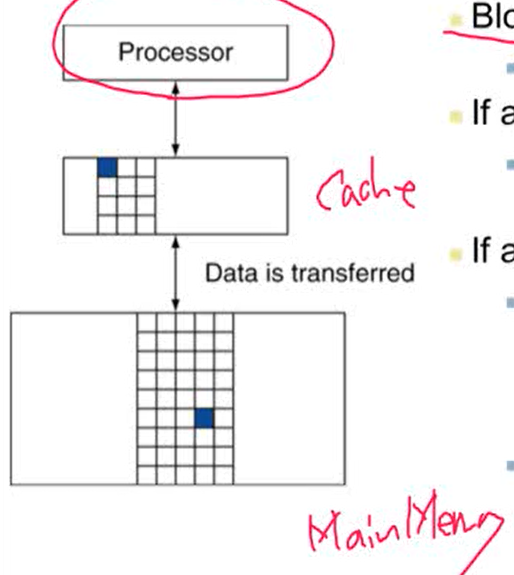

2. Taking Advantage of Locality

- memory hierarchy 사용해서 자주 사용하는 정보를 CPU와 가까운 곳으로 복사함

- 모든 중요한 정보는 disk에 존재. 자주 사용하는 정보는 disk에서 DRAM(main memory)으로 올림. DRAM에서 자주 사용하는 정보를 SRAM의 작은 memory 부분(cache)에 올림

- 캐시는 CPU와 통합되어 있음

- 모든 중요한 정보는 disk에 존재. 자주 사용하는 정보는 disk에서 DRAM(main memory)으로 올림. DRAM에서 자주 사용하는 정보를 SRAM의 작은 memory 부분(cache)에 올림

2. Memory Hierarchy Levels

- Block(line): copy의 단위. 한 block은 여러 개의 word로 구성되어 있음

- Hit: CPU가 어떤 데이터에 접근하고자 할 때 접근할 데이터가 upper level에 존재하는 경우

- hit ratio: hits/accesses

- Miss: CPU가 어떤 데이터에 접근하고자 할 때 접근할 데이터가 upper level에 없는 경우, 즉 lower level에서 데이터를 가져와야하는 경우

- miss penalty: lower level에서 데이터를 가져오는데 걸리는 시간

- miss ratio = missess/accesses = 1 - hit ratio

- miss가 발생할 경우 upper level로 데이터를 전달해줌

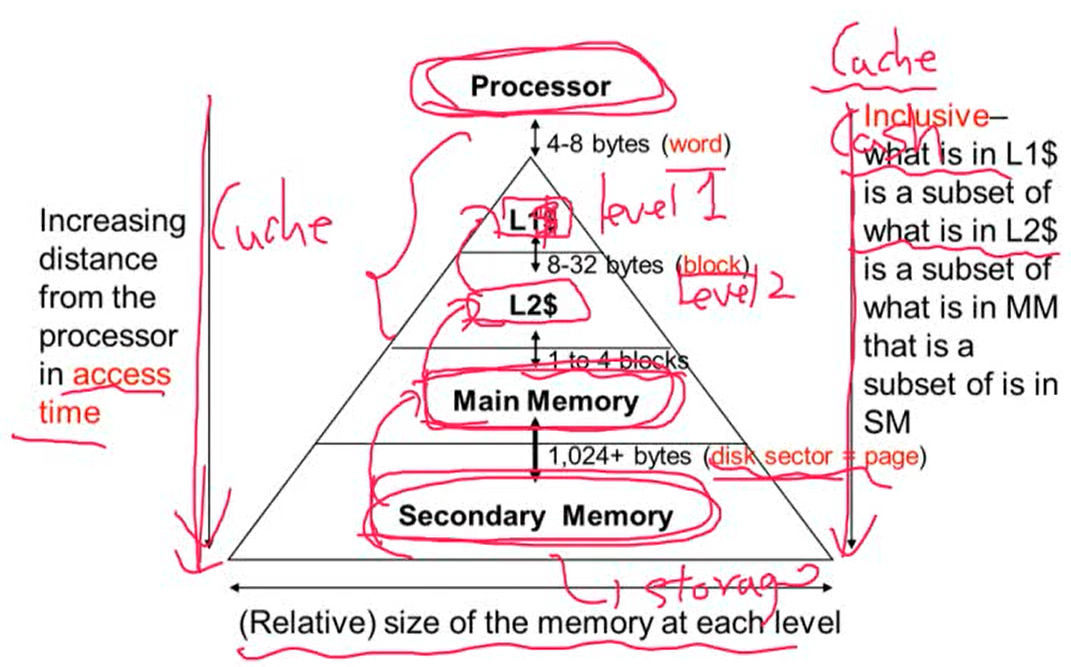

Characteristics of the Memory Hierarchy

- secondart memory: storage

- L1$ + L2$: cache. cache를 간단하게 표한하고 싶을 때 $를 사용

- 프로세서에서 멀수록 access time은 증가. 밑의 level로 올수록 메모리의 크기는 커짐

- L1$ 에 있는 정보는 L2$에 있는 정보의 subset. inclusive의 특징을 가짐

3. DRAM Technology

- capacitor에 charge를 하는 방식으로 저장됨

- 주기적으로 refresh 해주어야 함. SRAM의 경우 데이터를 한 번 쓰면 refresh해주지 않아도 됨

- 2차원 배열 모양으로 되어 있음

- row를 먼저 access한 다음 column를 access

- burst mode: row가 같고 column이 변하는 경우 row를 다시 access하지 않아도 되기 때문에 훨씬 빠르게 access할 수 있음.

- Double data rate (DDR) DRAM: rising edge와 falling edge 모두 데이터 전송이 가능

- Single data rate (SSR) DRAM: rising edge 또는 falling edge 모두 데이터 전송이 가능

- Quad data rate (QDR) DRAM: input, output 포트를 하나씩 더 만듦

4. DRAM Performace Factors

1. Row buffer

- row 단위로 데이터를 access할 때 row별로 buffer를 사용하기 때문에 여러 word를 한번에 read하거나 refresh하는 것이 가능

2. Synchronous DRAM (SDRAM)

- DRAM이 clock에 동기화 됨

- burst mode인 경우 연속된 access는 매번 주소를 줄 필요없이 바로 access 가능

3. DRAM banking

- 다음에 자세히

11주차 강의 끝!!!

게시물에 사용된 사진은 강의 내용을 캡쳐한 것입니다.