KOCW에 공개된 영남대 최규상 교수님 컴퓨터 구조 강의를 수강 후 정리한 내용입니다.

5.7 Virtual Memory

- 프로그램들은 main memory를 공유

- 각각의 프로그램들은 private virtual address를 가짐. 자주 사용하는 코드와 데이터를 올림

- 하나의 프로그램이 사용한 virtual address는 다른 프로그램으로부터 보호되어야 함

- CPU와 OS는 virtual memory를 physical address로 변환해주어야함

- VM에서 하나의 block를 page라고 부름

- VM translation에서 miss를 page fault라고 부름

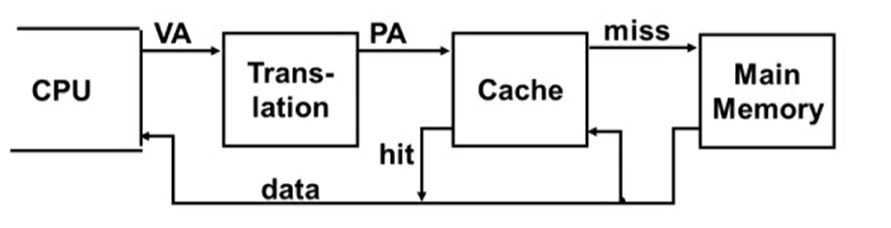

1. Virtual Addressing with a Cache

- CPU가 사용하는 주소는 virtual address, cache에서 사용하는 주소는 physical address

- translation: virtual address를 physical address로 변환

- translation를 하는데 extra memory가 필요

- translation 정보는 main memory에 저장되기 때문에 translation 정보에 access하기 위해서는 main memory에 access해야 함

- main memory를 access하는데 걸리는 시간은 cache 메모리에 access하는 시간보다 오래 걸림

- 따라서 매번 cache를 access하는데 main memory를 access하는 건 비효율적

- 하드웨어가 CPU에 Translation Lookaside Buffer(TLB)를 추가

- TLB: 최근에 address translation된 정보를 가지고 있는 buffer

- TLB에 먼저 접근해서 사용하고자하는 데이터의 주소가 TLB에 있다면 바로 사용하고, 없으면 main memory에 접근해서 address translation 수행

- 변환된 physical address를 사용해 cache에 access

- hit이 발생하면 데이터를 cpu에 보냄

- miss가 발생하면 physical address를 사용해 main memory에 access

2. Page Table

- placement information를 저장

- page table entry의 배열로 구성. virtual page number가 index

- CPU의 page table register는 physical memory의 page table를 가지고 있음

- page가 main memory에 있는 경우 PTE는 physical page number를 저장

- page가 main memory에 없는 경우 PTE는 disk의 swap space location를 저장

5.8 A Common Framework for Memory Hierarchies

1. The Memory Hierarchy

1. Block placement

- associativity와 관련. 1-way associativity(direct mapped), n-way set associativity, Fully associativity가 있음

- associativity가 높아지면 miss rate는 감소하지만 complexity, cost, access time은 증가

2. Finding a Block

- 하드웨어 cache의 경우 cost를 줄이기 위해 비교 횟수를 줄임

- virtual memory의 경우 miss rate를 줄이기 위해 full table lookup를 사용

3. Replacement

- LRU(Least recently used), Random이 있음

4. Write Policy

- write-through, write-back이 있음

- cache의 경우 두 방법 모두 사용 가능하지만 virtual memory의 경우 write-back만 사용

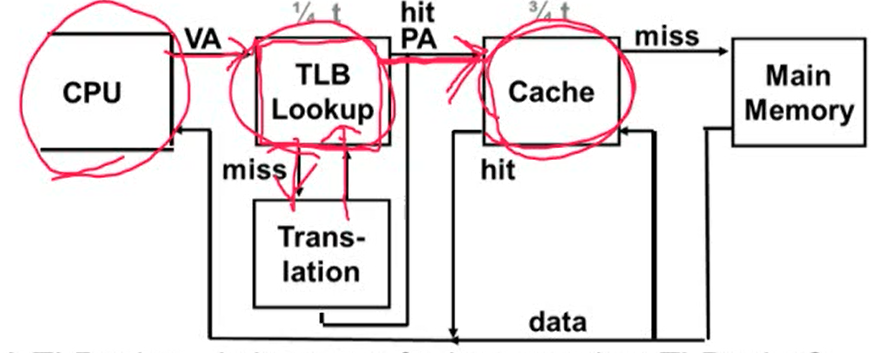

2. Sources of Misses (miss의 원인)

1. Compulsory misses (aka cold start misses)

- block를 처음 access할 때 발생하는 miss

- 피할 수 없는 miss

2. Capacity misses

- upper memory의 cache 크기가 low memory의 cache 크기보다 작아서 발생

- 하나의 block을 replace하는데 replace한 block를 다시 접근하면 miss 발생

- cache의 크기가 memory의 크기와 같은 경우 발생하지 않음

3. Conflict misses (aka collision misses)

- non-fully associative cache에서 set안에 경쟁에 의해 발생하는 misses

- fully associative cache에서는 발생하지 않음

3. Cache Design Trade-off

5.9 Using a Finite State Machine to Control A Simple Cache

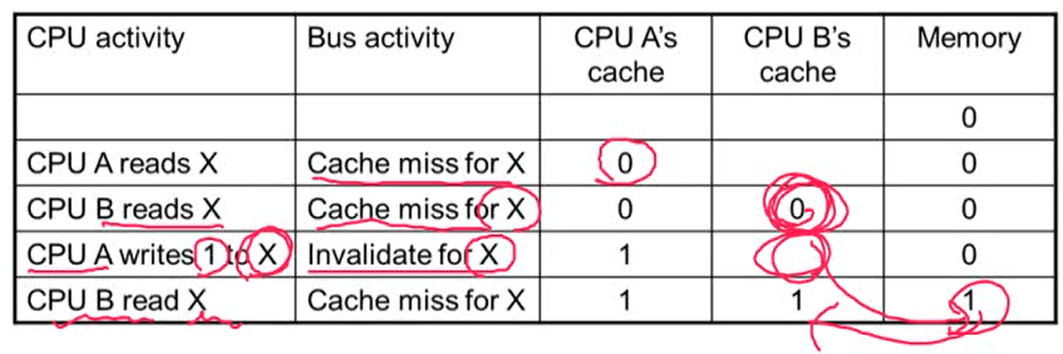

Cache Coherence Problem

- Cache에 있는 같은 physical memory에 대해서 서로 다른 cache의 다른 data가 가지고 있을 때 cache coherence 문제가 발생

- 항상 가장 최근에 쓴 값을 읽게되는 것을 원함. p가 X를 쓰고 o가 X를 썼을 때 X에는 o가 쓴 값이 들어가 있어야 함

Cache Coherence Protocols

- Snpoping protocol: 각각의 cache들은 bus의 read, write를 모니터링하다가 본인 cache에 올라와있는 entry에 해당되는 data가 read 혹은 write되면 본인 cache를 update

- bus를 share하는 경우 많이 사용

- invalid message를 bus에 broadcasting해서 다른 cache에 있는 해당되는 data를 invalid시킨 후에 read 혹은 write를 수행

- bus를 share하는 경우 많이 사용

- Directory-based protocols: directory에서 cache의 각각의 status 정보를 가지고 있음

- core의 수가 많거나 memory가 다 차지 않은 경우 적합

5.16 Concluding Remarks

1. 빠른 메모리일수록 크기가 작고, 큰 메모리일수록 느림

- 빠르고 큰 메모리를 원하지만 실제로 구현할 수 없기 때문에 cache를 사용해 빠르고 큰 메모리를 사용하는 것 같은 착각을 줌

2. Principle of locality

3. Memory hierarchy

- L1, L2, ..., DRAM memory, disk

4. 메모리 시스템 디자인은 멀티코어에서 성능에 큰 영향을 주기 때문에 매우 중요

13주차 강의 끝!!!

게시물에 사용한 사진은 강의 내용을 캡쳐한 것입니다.