1. Before RISC-V

- Fixed length instruction

- Example

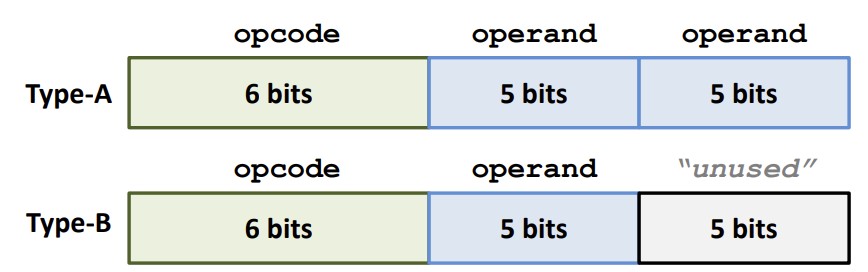

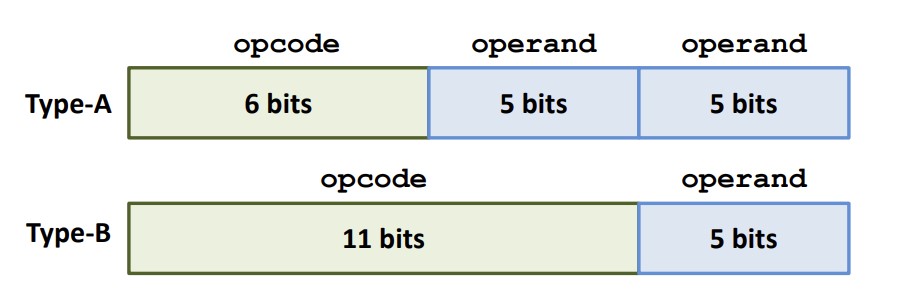

- 16-bit fixed length instructions, with 2 types of instructions

- Type-A : 2 operands, 5-bit respectively

- Type-B : 1 operand of 5-bit

- Solution I : Make same format -> MSB로 Type A, B 구별 -> 2^5 + 2^5 = 64

- Solution II : Expand opcode -> Type-A를 고정함으로써 구별

-> if Type-A 가 1일 경우 -> 1 + (2^6 - 1) x 2^5

-> if Type-A 가 10일 경우 -> 10 + (2^6 - 10) x 2^5

-> Type-A 가 작을 수록 만들 수 있는 명령어의 갯수는 최대

- 16-bit fixed length instructions, with 2 types of instructions

2. Instruction format of RISC-V

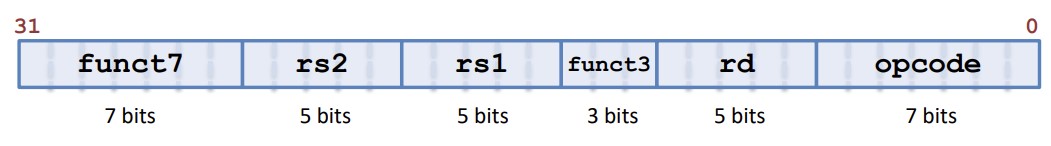

1. R-Type - Arithmetic

-

Need three operands : one for destination and two sources

- ex) add a, b, c / a <- b + c

- ex) sub, a, b, c / a <- b - c

-

Data in memory cannot be addressed directly ALU instructions

- Compiler must use data in register

- Register is faster -> Register optimization

- Compiler must use data in register

-

R-Type instruction format

- Assembly : ADD, rd, rs1, rs2

- Semantics : GPR[rd] <- GPR[rs1] + GPR[rs2]

- opcode : basic operation

- rd : destination register

- rs1, rs2 : source register

- func3, func7 : additional opcode

-

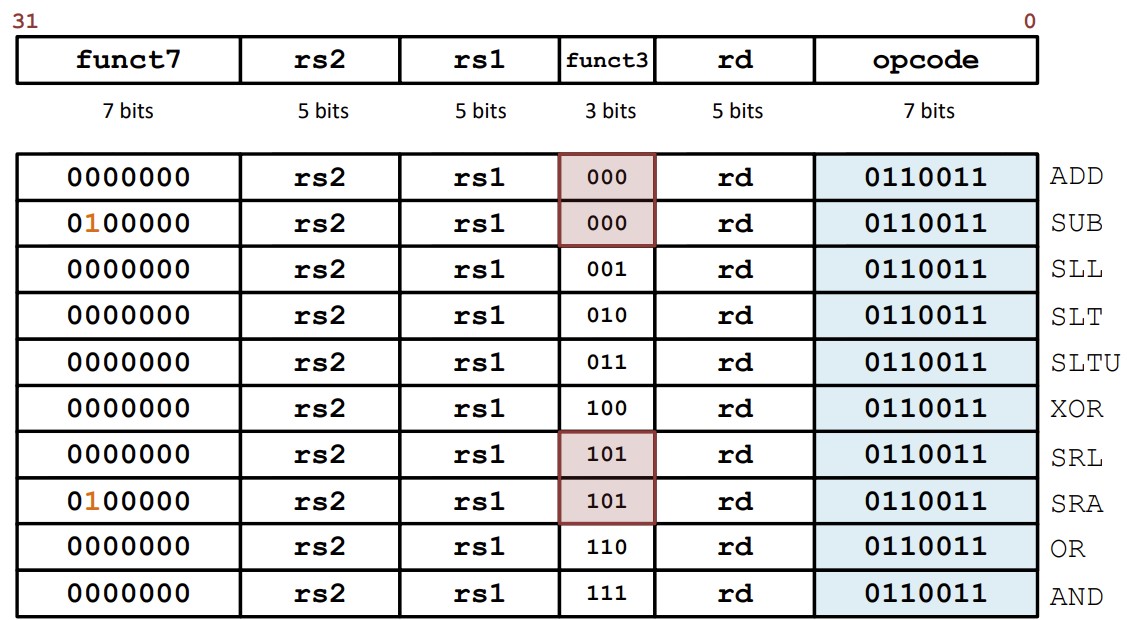

R-Type opcode

-

opcode 로 구분하지 않고 func 으로 구분하는 이유?

-> opcode 의 bit 조작 없이 func 만 추가하면 되므로 설계가 더 간단하고 확장에 유리하다.- SLL (SRL) : Shift Left (Right) Logical

- SLL: The low-order bit is replaced by a zero bit and

the high-order bit is discarded. - SRL: The high-order bit is replaced by a zero bit and

the low-order bit is discarded.

- SLL: The low-order bit is replaced by a zero bit and

- SRA : Shift Right Arithmetic

- Vacant bits are filled with sign bit (Sign extension)

- SLA does not need to be supported because MSB will be discarded

- SLT : Set Less Than

- SLT, rd, rs1, rs2 => if rs1 < rs2 then: 1 else: 0

- SLT(U) : Set Less Than (Unsigned)

- 부호 고려하지 않고 Comparison

- SLL (SRL) : Shift Left (Right) Logical

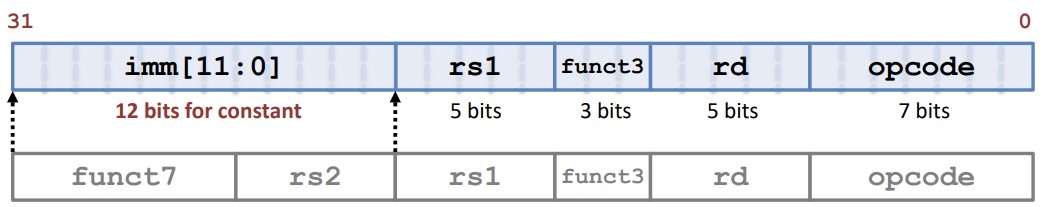

2. I-Type - Constant or Immediate

- Arithmetic uses a constant number

- ex) addi x22, x22, 4 => x22 <- x22 + 4

- Immediate operand instructions are faster due to no additional memory access

- I-Type instruction format

- Assembly : ADDI, rd, rs1, imm12

- Semantics : GPR[rd] <- GPR[rs1] + sign-extend (imm)

- 부호를 구별하므로 sub 연산이 없다!

- The range of imm is from -2^11 to 2^11 - 1

- Imm is sign extended to 32-bits

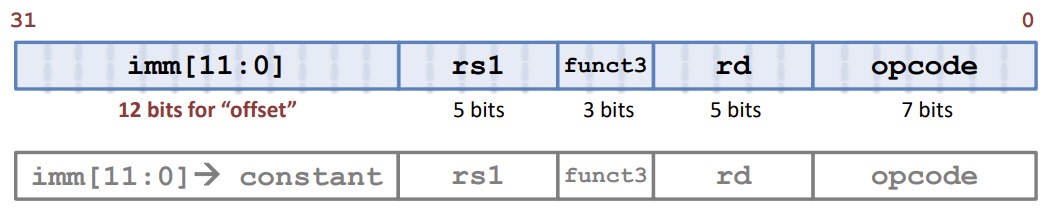

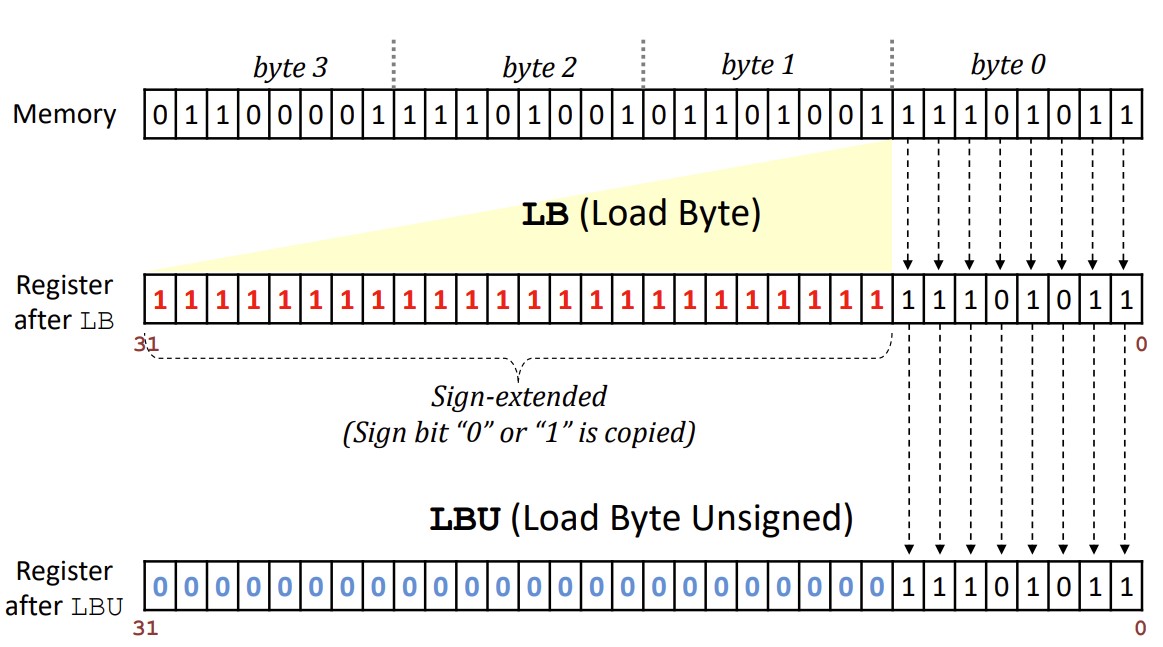

3. I-Type - load

- Memory operand

- The capacity of registers are limited; therefore, we need to load data from memory to register

- Load instruction format

- Assembly : LW, rd, offset (base register)

- Semantics : GPR[rd] <- Mem[byte_address]

- ex) ld, x2, 16(x3) => x2 <- x3 + offset(16)

- lb(sign extend) vs lbu(zero extend)!

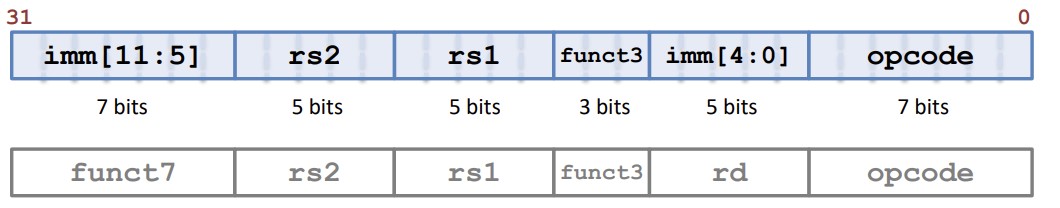

4. S-Type - store

- Store instruction format

- Assembly : SW, rs2, offset (base register)

- Semantics : Mem[byte_address] <- GPR[rs2]

- no need the destination address of register

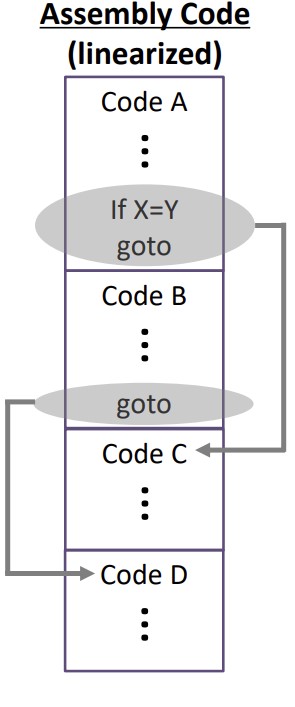

4. SB-Type - branch

- Assembly code 는 linearized 되어있기 때문에 pc값을 원하는 값으로 변경할 수 있는 명령어가 필요하다.

-

Branch : change of control flow

- Conditional branch : change control flow depending on outcome of comparison

- Unconditional branch : just branch

-

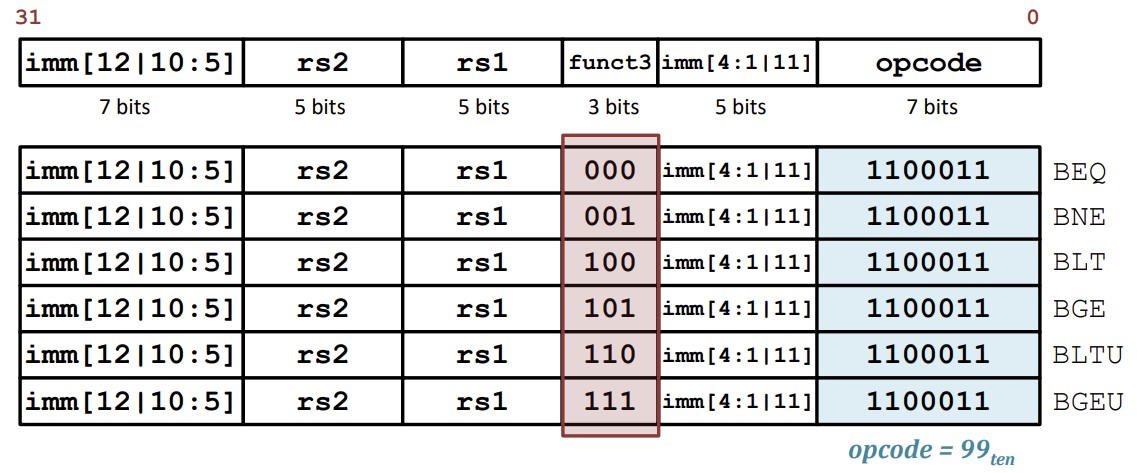

Branch instruction format

- Assembly : BEQ, rs1, rs2, Label

- Semantics : if GPR[rs1] = GPR[rs2] then PC <- target (Label)

else : PC <- PC + 4

- beq : branch if equal

- bne : branch if not equal

- blt : branch if less than

- bge : branch if greater than

- bltu, bgeu : unsigned

-

imm field is 13 bits because imm[0] is assumed to be always 0

-

if moving individual lines of code, branch immediate field should be changed

-

if moving all of code, branch immediate field does not need to be changed -> branch immediate field has PC-relative offsets

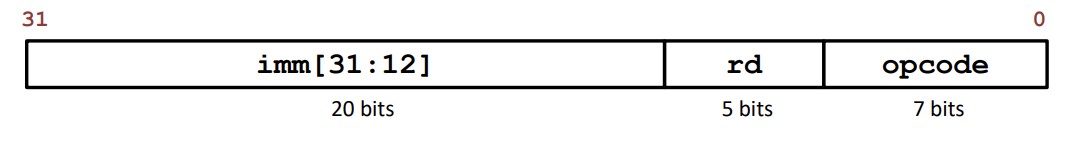

5. U-Type

-

There are times when constants are too big to fit into 12 bits

-

Load 20bit constant into position 31~12

-

Rightmost 12 bits should be zero

-

possible to create 32-bit value by addi

-

there is an issue when using addi due to sign-extended

- solution : Assembler can handle this problem by using pseudo-instructions

꾸벅