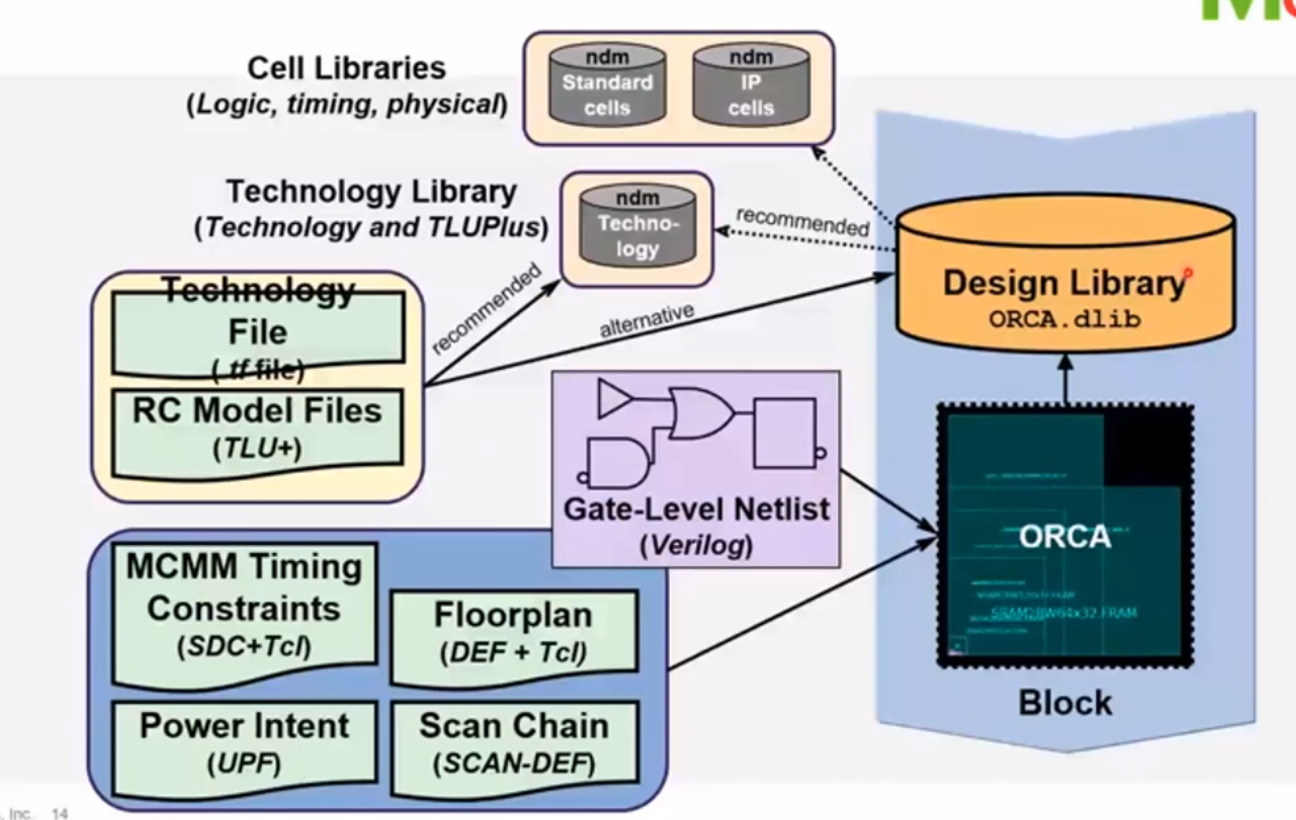

Design Setup

| Design Setup |

|---|

|

Create a "Container": The Design Library

lappend search_path <x/y/ndms>

create_lib <ORCA.nlib> \

-use_technology_lib <abc14_9m_tech.ndm> \

- ref_libs { \

abc14_9m_tech.ndm \

<abc14_hvt_std.ndm> <abc14_svt_std.ndm> <abc14_lvt_std.ndm> \

<abc14_srams.ndm> <abc14_ip.ndm> \

<abc14_level_shifters.ndm> \

<abc14_physical_only.ndm> \

}

lappend: 아래 모든 경로에 <>안이 추가됨

-use_technology_lib에서.tf가 아닌.ndm를 쓰면 밑에-ref_libs에도 추가해줘야함

아닐 경우 아래와 같이create_lib <ORCA.nlib> -technology <abc14_9m_tech.tf> -ref_libs ...

Technology Information

create_lib ORCA.nlib -tecnology abc_14_9m_tech.tf -ref_libs ...

read_parasitic_tech -tlup <$TLUPLUS_MAX_FILE> -name <maxTLU>

read_parasitic_tech -tlup <$TLUPLUS_MAX_FILE> -name <maxTLU>

set_attribute [get_site_defs <unit>] is_default true

set_attribute [get_site_defs <unit>] symmetry Y

set_attribute [get_layers {M1 M3}] track_offset 0.03

set_attribute [get_layers {M1 M3 M5}] routing_direction horizontal

set_attribute [get_layers {M2 M4 M6}] routing_direction verticalRebind a Design Library

icc2_shell> open_lib $DESIGN_LIBRARY

icc2_shell> set search_path "/new_location"

icc2_shell> set_ref_libs -rebind

icc2_shell> report_ref_libs

icc2_shell> save_lib

-rebind: 현재 연 디자인의 libs들을 위에서 설정한search_path로 설정

Read the Netlist and Create a Design

lappend search_path <./netlist>

read_verilog -top <ORCA> <ORCA.v>

link_block검사법들

report_design_mismatch -verbos

get_cells -hierarhical -filter is_unbound

Specify Unused Layer

set_ignored_layers -max_routing_layer <M7>

report_ignored_layersUPF

load_upf <ORCA.prime.upf>

commit_upfCreate Voltage Areas (for MV Designs)

create_voltage_area -power_domains PD1 \

-guard_band {{10 10}} \

-region {{377 377} {215 377} {215 485} \

{404 485} {404 215} {377 215}}

create_voltage_area -power_domains PD2 \

-guard_band {{10 10}} \

-region {{215 215} {350 350}}Connect PG Pins

connect_pg_net

check_mv_design

set_dont_touch [get_lib_cells */TIE*] false

set_lib_cell_purpose -include optimization [get_lib_cells std_cell_hvt/TIE*]바로 VDD나 VSS로 cell을 연결하면 cell에 문제가 생기므로 tie cell 사용