일단 기능검증을 위해 매우 간략하게 구현하였다.

실제로는 Kogge-Stone Adder로 구현될 것이다.

// Sint16_adder.v

module cnt

(

input clk,

input rstn,

input [15:0] data_A,

input [15:0] data_B,

output [15:0] data_C,

output Cout

);

reg [16:0] data_OUT;

assign data_C = data_OUT[15:0];

assign Cout = data_OUT[16];

always @(posedge clk, negedge rstn) begin

if(!rstn) begin

data_OUT = 17'b0_0000_0000_0000_0000;

end

else begin

data_OUT = (data_A + data_B);

end

end

endmodule

//sim_main.cpp

// DESCRIPTION: Verilator: Verilog example module

//

// This file ONLY is placed under the Creative Commons Public Domain, for

// any use, without warranty, 2017 by Wilson Snyder.

// SPDX-License-Identifier: CC0-1.0

//======================================================================

// Include common routines

#include <verilated.h>

#include <iostream>

using namespace std;

// Include model header, generated from Verilating "top.v"

#include "VSint16_adder.h"

#include "verilated_vcd_c.h"

int main(int argc, char** argv, char** env) {

// See a similar example walkthrough in the verilator manpage.

// This is intended to be a minimal example. Before copying this to start a

// real project, it is better to start with a more complete example,

// e.g. examples/c_tracing.

// Prevent unused variable warnings

if (false && argc && argv && env) {}

// Construct the Verilated model, from Vtop.h generated from Verilating "top.v"

VSint16_adder* top = new VSint16_adder;

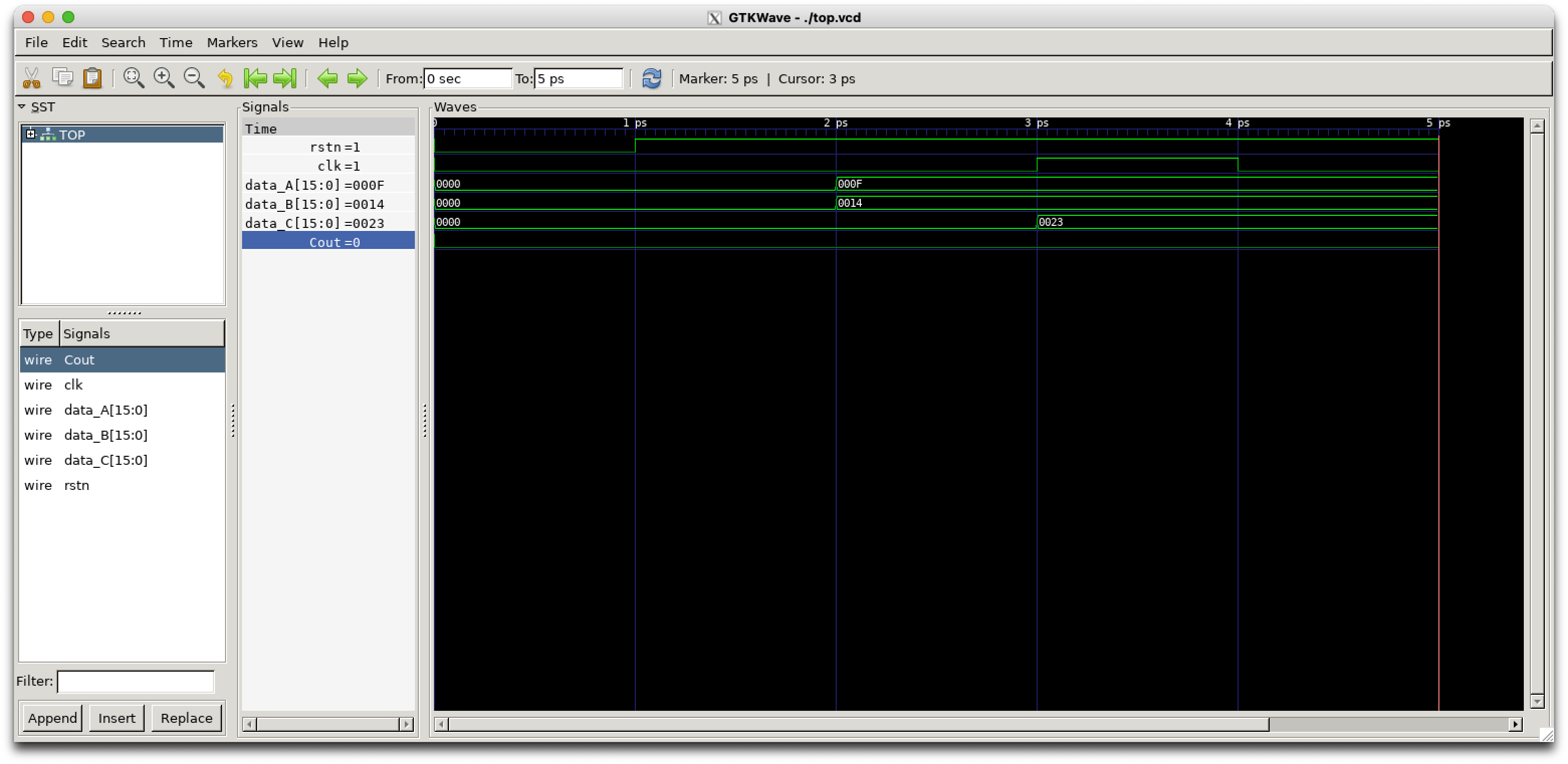

// FOR WAVEFORM

Verilated::traceEverOn(true);

VerilatedVcdC* wave_fp = new VerilatedVcdC;

int time = 0;

top->trace(wave_fp, 999);

printf("waveform file name is top.vcd\n");

wave_fp->open("./top.vcd");

top->rstn=0;

top->clk=0;

top->data_A=0;

top->data_B=0;

top->eval();

wave_fp->dump(time); time++;

top->rstn=1;

top->clk=0;

top->data_A=0;

top->data_B=0;

top->eval();

wave_fp->dump(time); time++;

top->data_A=15;

top->data_B=20;

top->clk=0;

top->eval();

wave_fp->dump(time); time++;

top->clk=1;

top->eval();

wave_fp->dump(time); time++;

cout<<top->data_A<<" + "<<top->data_B<<" == "<<top->data_C<<endl;

// Final model cleanup

top->final();

wave_fp->close();

// Destroy model

delete top;

delete wave_fp;

// Return good completion status

return 0;

}

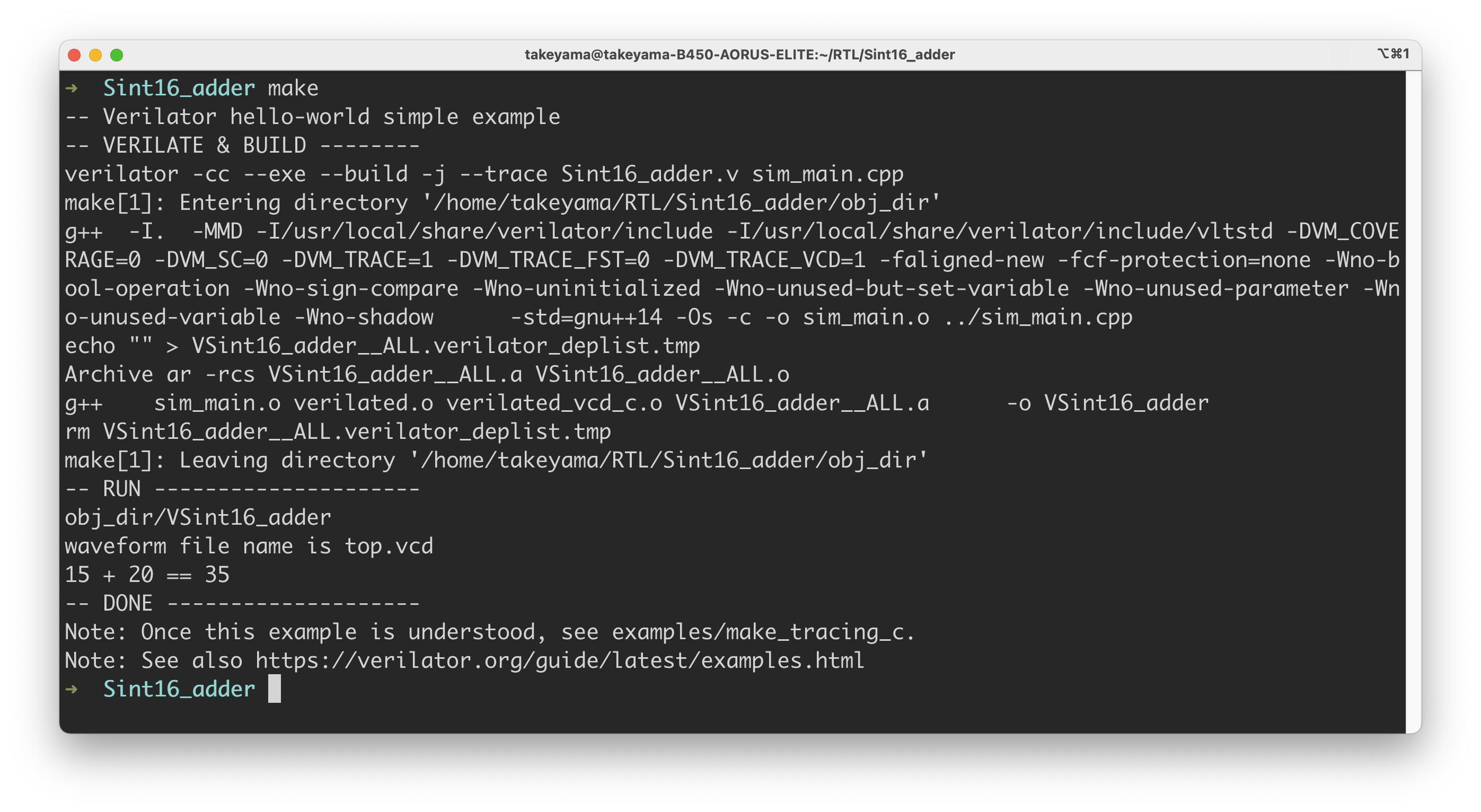

Makefile

######################################################################

#

# DESCRIPTION: Verilator Example: Small Makefile

#

# This calls the object directory makefile. That allows the objects to

# be placed in the "current directory" which simplifies the Makefile.

#

# This file ONLY is placed under the Creative Commons Public Domain, for

# any use, without warranty, 2020 by Wilson Snyder.

# SPDX-License-Identifier: CC0-1.0

#

######################################################################

# Check for sanity to avoid later confusion

ifneq ($(words $(CURDIR)),1)

$(error Unsupported: GNU Make cannot build in directories containing spaces, build elsewhere: '$(CURDIR)')

endif

######################################################################

# This is intended to be a minimal example. Before copying this to start a

# real project, it is better to start with a more complete example,

# e.g. examples/make_tracing_c.

# If $VERILATOR_ROOT isn't in the environment, we assume it is part of a

# package install, and verilator is in your path. Otherwise find the

# binary relative to $VERILATOR_ROOT (such as when inside the git sources).

ifeq ($(VERILATOR_ROOT),)

VERILATOR = verilator

else

export VERILATOR_ROOT

VERILATOR = $(VERILATOR_ROOT)/bin/verilator

endif

MODULENAME = Sint16_adder

default:

@echo "-- Verilator hello-world simple example"

@echo "-- VERILATE & BUILD --------"

$(VERILATOR) -cc --exe --build -j --trace $(MODULENAME).v sim_main.cpp

@echo "-- RUN ---------------------"

obj_dir/V$(MODULENAME)

@echo "-- DONE --------------------"

@echo "Note: Once this example is understood, see examples/make_tracing_c."

@echo "Note: See also https://verilator.org/guide/latest/examples.html"

######################################################################

maintainer-copy::

clean mostlyclean distclean maintainer-clean::

-rm -rf obj_dir *.log *.dmp *.vpd core

모듈 인수 선언시

input [15:0] data_A,

가 아니라

input data_A [15:0] ,

로 하면 에러남.

되는걸로 알고있는데, Verilator는 안해주나보다.

찾느라 10분 삽질함