[chisel-tutorial] VecShiftRegisterSimple.scala: Seq 사용 - Seq.fill(4) { 0.U(8.W)}

0

Chisel 독학

목록 보기

26/44

VecShiftRegister.scala문제의 하위호환이다.

바로 풀었다.

다만, 참고할 점이 있었다.

풀이

Test Code

// See LICENSE.txt for license details.

package problems

import chisel3.iotesters.PeekPokeTester

class VecShiftRegisterSimpleTests(c: VecShiftRegisterSimple) extends PeekPokeTester(c) {

val reg = Array.fill(4){ 0 }

for (t <- 0 until 16) {

val in = rnd.nextInt(256)

poke(c.io.in, in)

step(1)

for (i <- 3 to 1 by -1)

reg(i) = reg(i-1)

reg(0) = in

expect(c.io.out, reg(3))

}

}

정답

// See LICENSE.txt for license details.

package problems

import chisel3._

// Problem:

//

// Implement a shift register with four 8-bit stages.

// Shift should occur on every clock.

//

class VecShiftRegisterSimple extends Module {

val io = IO(new Bundle {

val in = Input(UInt(8.W))

val out = Output(UInt(8.W))

})

val initValues = Seq.fill(4) { 0.U(8.W) }

val delays = RegInit(VecInit(initValues))

// Implement below ----------

delays(0) := io.in

for(i <- 1 until 4){

delays(i) := delays(i-1)

}

io.out := delays(3)

// Implement above ----------

}

What I learned

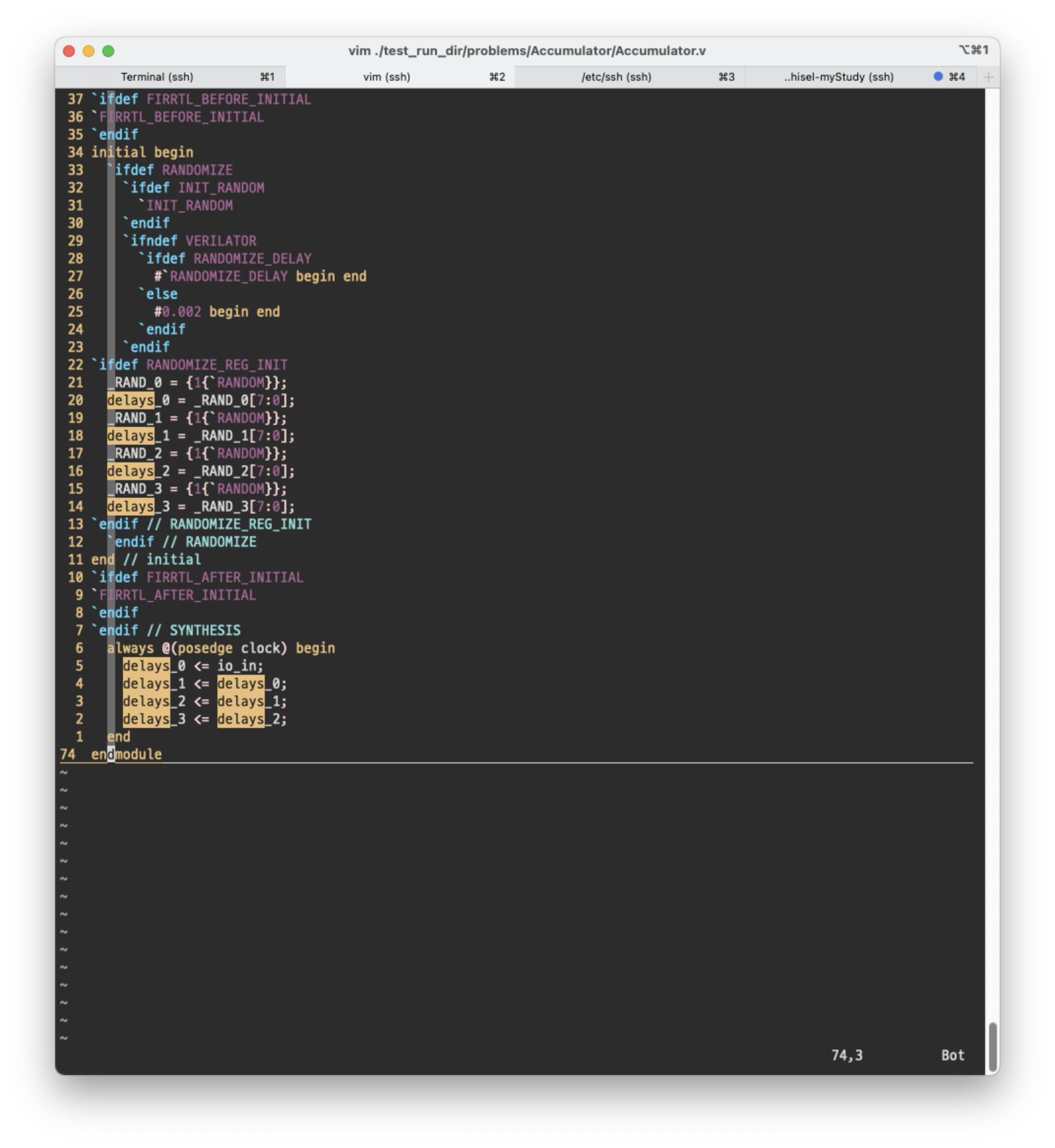

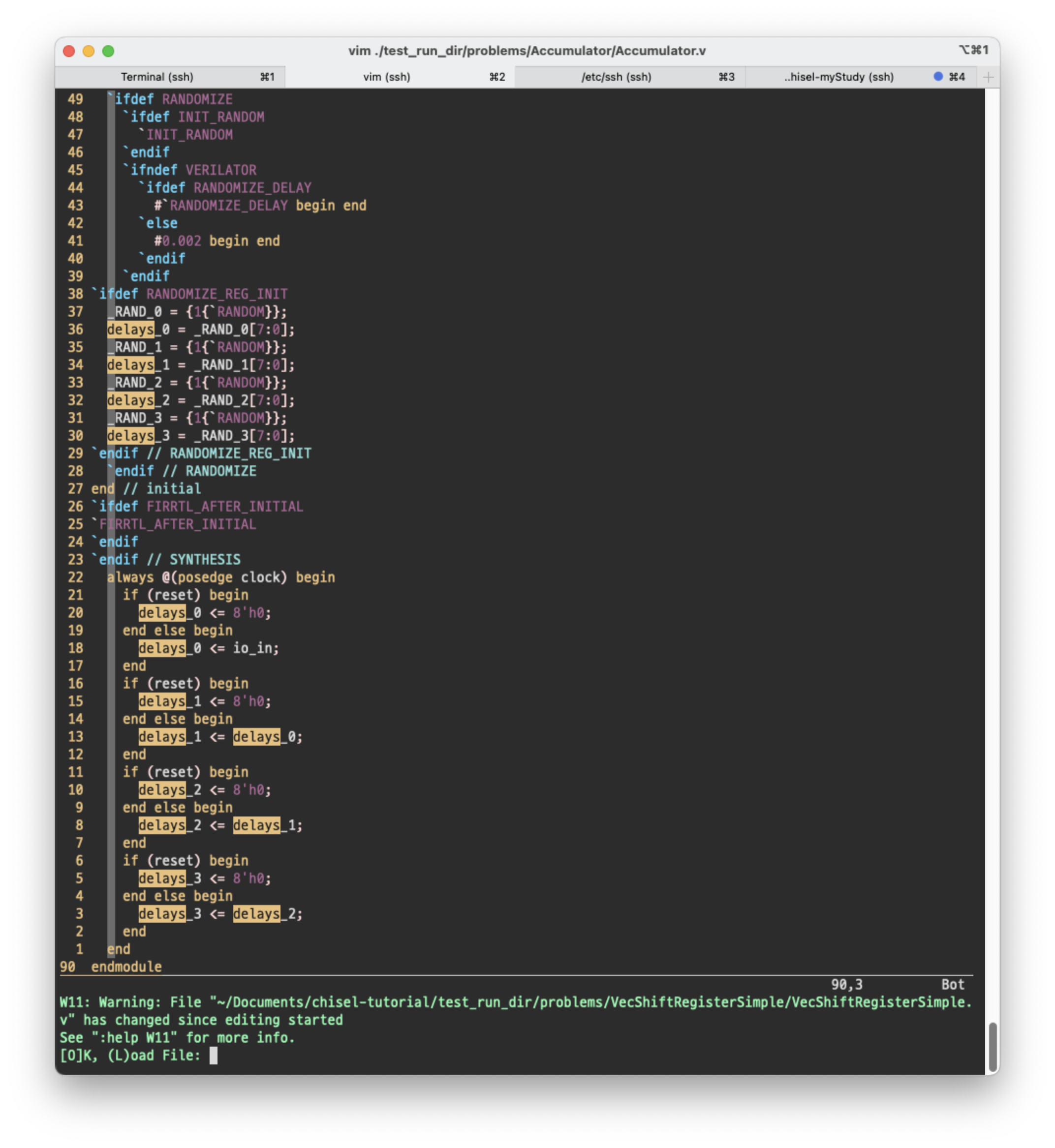

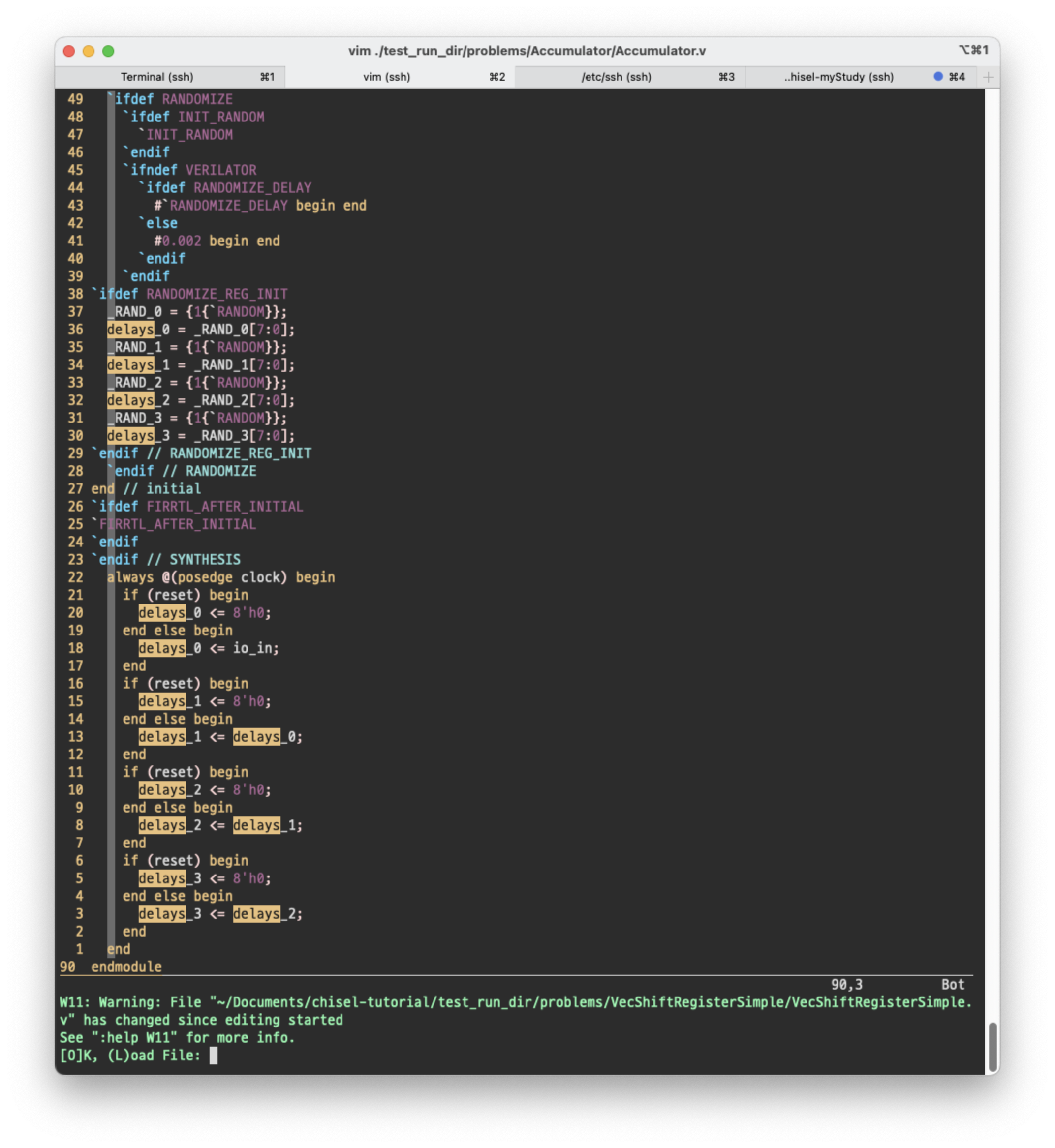

- Seq.fill하여 4*8을 만든 뒤, 해당 seq로 Vec을 만들고, 이걸로 RegInit을 하여 메모리를 선언할 수도 있다.

이 경우, reset이 구현된 상태로 elaborate되게 된다.

val initValues = Seq.fill(4) { 0.U(8.W) }

val delays = RegInit(VecInit(initValues))

- 기존의 나는 이렇게 선언하고 썼는데,

이 경우 RegInit 및 VecInit을 하지 않았으므로

reset이 생략된 채로 구현된다.

val delays = Reg(Vec(4, UInt(8.W)))