Data Path

Chapter 2 전체에 걸쳐서 명령어들의 종류를 알아보고, 그 명령어들이 어떻게 동작하는지 알아봤었습니다. 이번 챕터에서는 명령어가 실행되었을 때, 데이터와 제어신호가 어떻게 움직이는지 알아보겠습니다.

Data Path에 대한 정의는 이렇게 내릴 수 있습니다.

컴퓨터의 명령어 처리 과정에서 데이터가 이동하고 연산되는 경로

주로 CPU 내부에서 프로세서가 명령어를 실행하는 동안 데이터와 제어신호가 이동하는 경로를 포함합니다.

Digital Systems

자세히 알아보기 전에 간단하게 알아야 할 정보들이 있습니다. 논리회로와 같은 지식이 있다면 넘어가도 될 내용이지만, 한 번 정리하기 위해 간단히 기술하겠습니다.

디지털 시스템을 구현하기 위해서 필요한 요소가 3개 있습니다.

- Combinational elements: input에 반응하여 즉각적으로 output

- Sequential elements: clock signal에 동기화되어 동작

- Clock signals: 메모리 요소를 업데이트하기 위한 신호

Combinational Elements

이 단원에서 사용할 combinational elements의 예시로는 Adder와 ALU, Multiplexer가 있습니다.

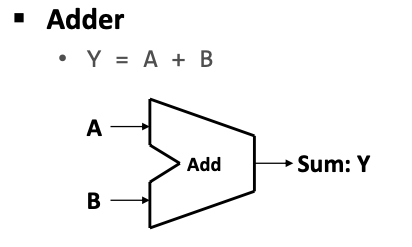

Adder

Adder는 위와 같은 구조로 되어 있으며, A와 B 값에 의해 즉각적으로 Sum을 출력합니다. 주로 PC 값을 계산할 때 사용됩니다.

ALU

ALU는 위와 같은 구조로 되어 있으며, A와 B 값에 더불어서 ALU control 값에 영향을 받습니다. ALU control 값에 따라 AND, OR, ADD와 같은 연산들을 수행하게 됩니다. R-type 명령어에서 연산을 하거나, immediate 값에 따라 달라지는 주소값을 연산할 때 사용됩니다.

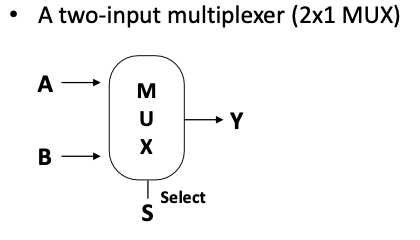

Multiplexer

Multiplexer는 MUX라고도 불리며, 쉽게 설명하면 input으로 들어온 요소들 중 하나를 선택해서 output으로 내보내는 역할을 합니다. Select 값에 따라 어떤 값을 출력할 지 정해집니다.

Sequential Elements

이 단원에서 사용하게 될 Sequential elements의 예시로는 레지스터와 메모리가 있습니다.

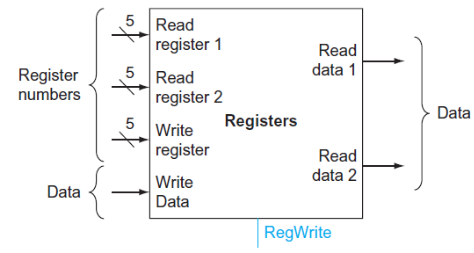

Register

레지스터는 정보를 읽고 쓰는 역할을 하며, 이 동작은 clock 신호가 있을 때만 실행됩니다. 더불어서 RegWrite 신호 또한 1로 설정이 되어있어야합니다.

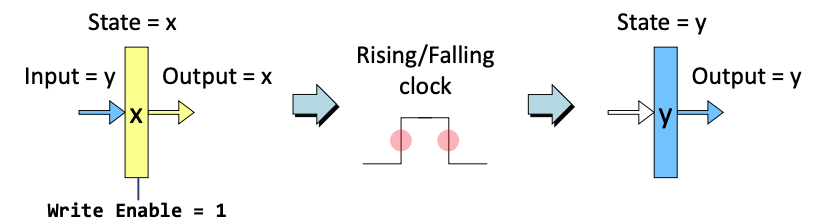

단순화된 과정은 아래와 같습니다. input에 즉각적으로 반응하지 않고, clock signal이 있어야만 값이 변경되는 것을 볼 수 있습니다.

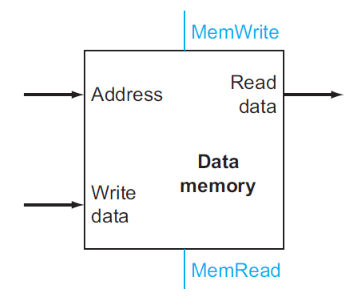

Memory

메모리도 레지스터와 같이 데이터를 저장할 때 clock signal이 발생하고, MemWrite가 1인 경우에만 데이터를 쓸 수 있습니다. 구조는 아래와 같습니다.

Clock

clock은 read/write 작업을 제어하는 역할을 합니다. clock은 rise와 fall의 2가지 신호를 가지며 각각 , 의 신호를 나타냅니다.

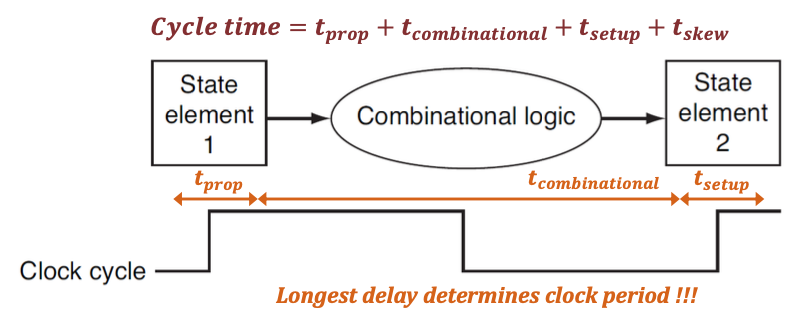

clock의 개념을 하나의 그림으로 나타내면 아래와 같습니다.

Cycle time은 state의 변화가 일어나는 총 시간입니다. CPU의 performance를 나타낼 때 사용했던 그 cycle time을 나타내는 것과 동일한 개념입니다.

이 시간은 총 4개로 나누어 볼 수 있는데, 설명의 편의상 부터 설명하겠습니다.

- : input data가 처리되어 output이 나올 때까지 걸리는 시간이며, 가장 오래 걸리는 작업을 기준으로 생성됩니다.

- : 데이터를 안전하게 받아들이기 위해 신호가 미리 도착해야하는 시간입니다.

- : 데이터가 조합 논리로 전달되는 데 걸리는 시간이며, 이 시간 안에는 도 포함 되어있습니다. 는 신호가 도달한 후 유지되어야하는 시간을 나타냅니다.

- : 동일한 클럭 신호가 서로 다른 위치에 도달하는 데 걸리는 시간 차이입니다.

Build Datapath

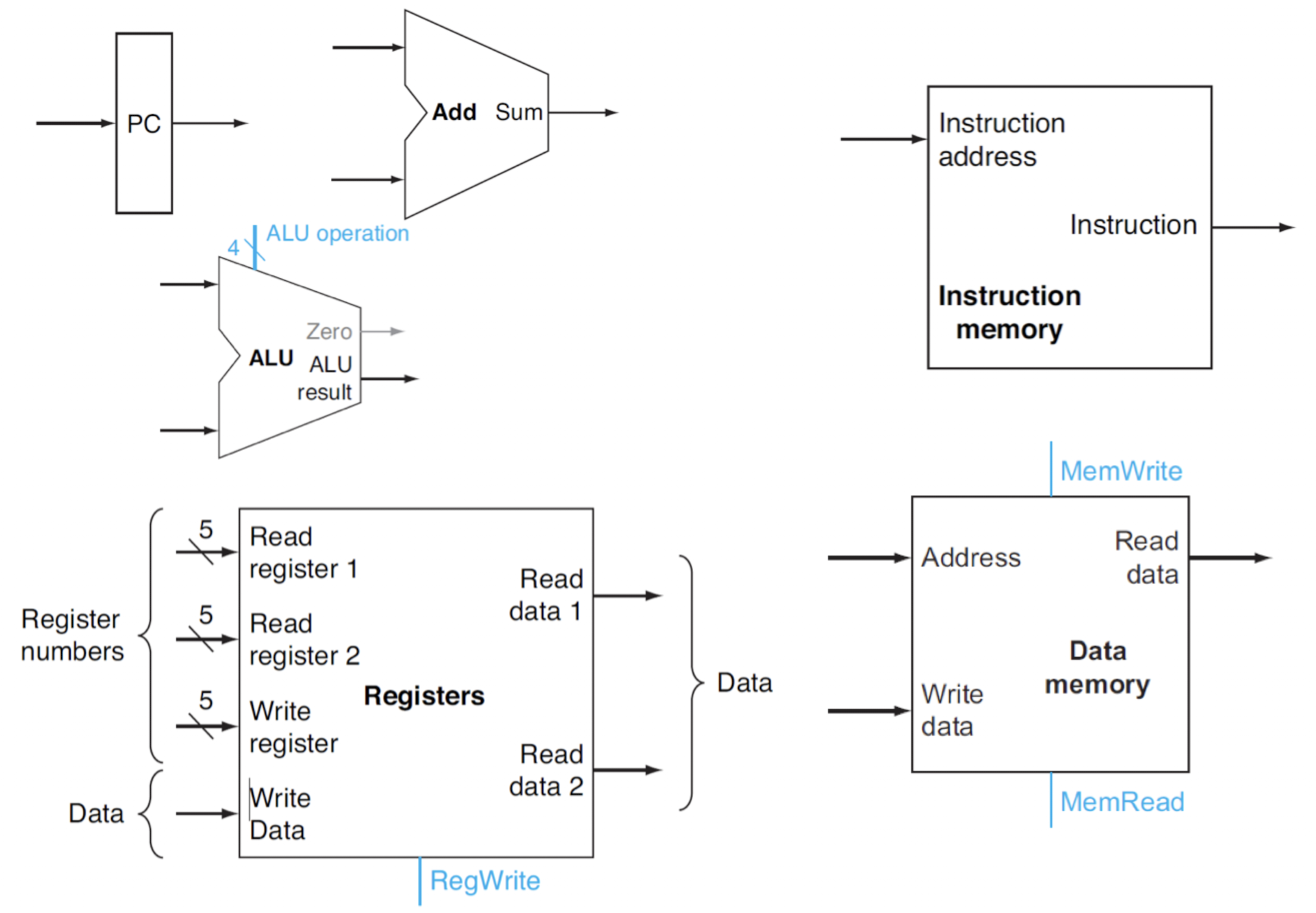

Single Cycle Implementation을 위한 재료들은 아래 그림과 같습니다.

각각의 요소들마다 자세한 동작들을 설명해야하지만, 글의 길이와 시간상 생략하도록 하겠습니다.

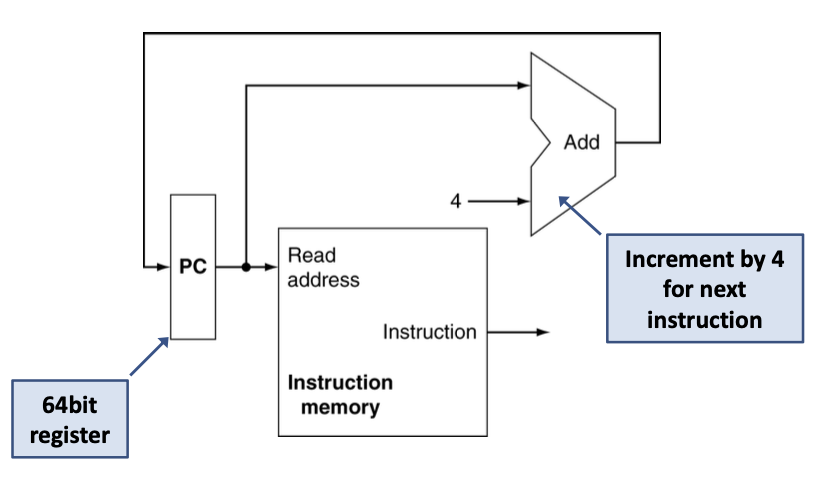

Instruction Fetch

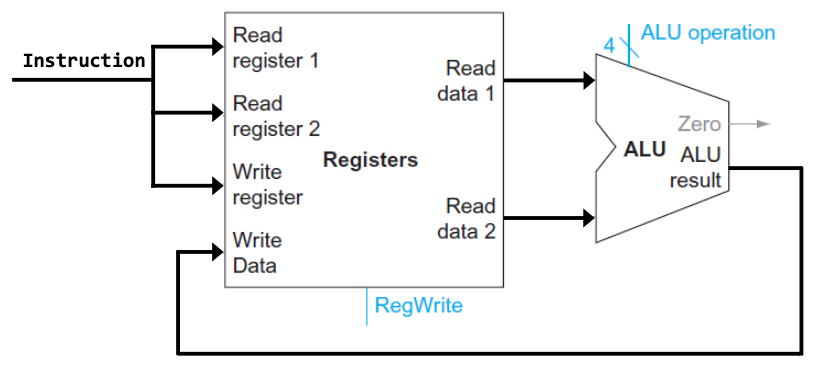

R-Format

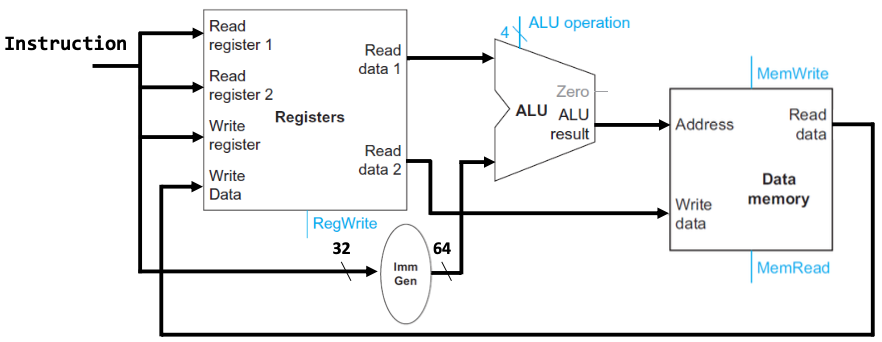

Load/Store

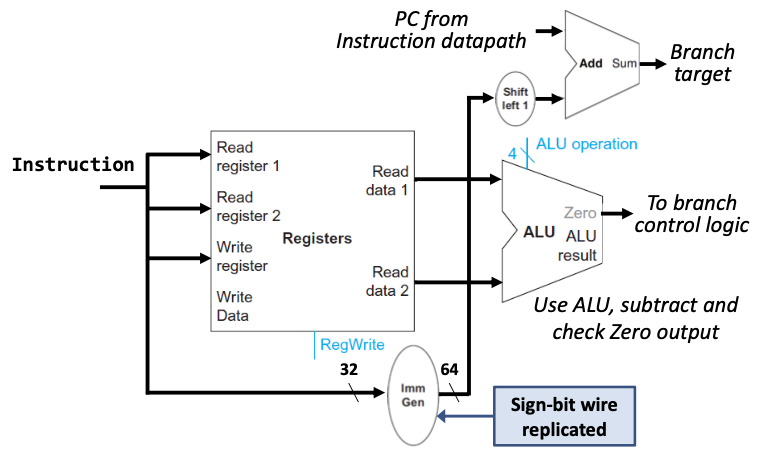

Branch

Main Control Unit

얘는 조금은 결이 다른 부분입니다. main control unit은 명령어를 해석하여 제어신호를 만드는 역할을 합니다. 레지스터에 쓸 지, 메모리에 쓸 지 읽을 지, 어떤 ALU 연산을 수행할 지 와 같은 신호를 만듭니다.

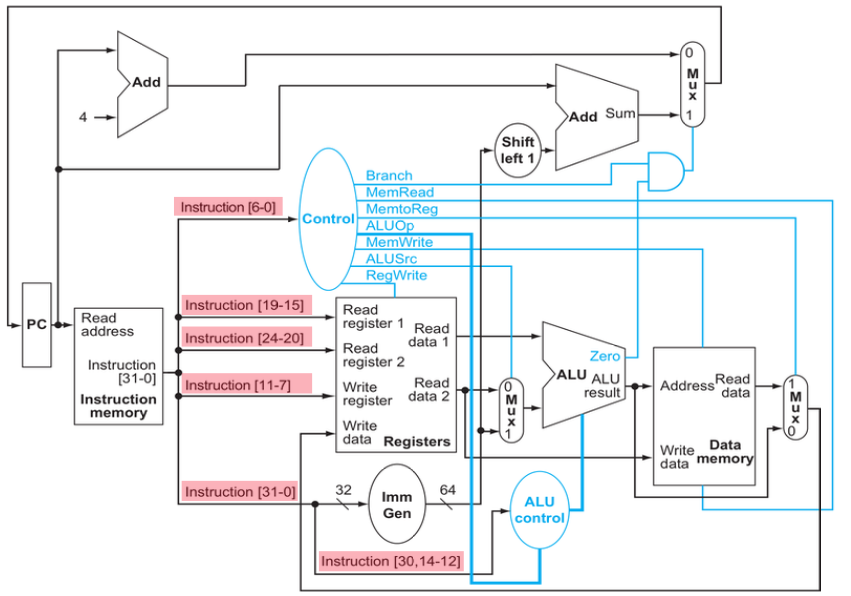

Complete Single Cycle DataPath

최종적인 완성 모습입니다.