Verilog를 사용하여 4x2 인코더를 구현하는 방법을 소개하겠습니다. 인코더는 하나의 활성화된 입력 신호를 이진 코드로 변환하는 장치입니다. 이 글에서는 동작적 모델링과 데이터 플로우 모델링을 사용하여 인코더를 구현하는 방법을 다루겠습니다.

1. 동작적 모델링을 이용한 4x2 인코더

동작적 모델링은 특정 조건이나 이벤트에 따라 동작을 정의하는 방식입니다. 아래는 동작적 모델링을 사용한 4x2 인코더의 Verilog 코드입니다.

module encoder_4x2(

input [3:0] signal,

output reg [1:0] code

);

always @(signal) begin

case(signal)

4'b0001 : code = 2'b00;

4'b0010 : code = 2'b01;

4'b0100 : code = 2'b10;

4'b1000 : code = 2'b11;

default : code = 2'b00; // 기본값 설정

endcase

end

endmodule이 코드는 always 블록을 사용하여 입력 신호 signal의 값에 따라 출력 신호 code를 설정합니다. case 문을 사용하여 4비트 입력 signal을 2비트 출력 code로 변환합니다. 만약 여러 입력 신호가 동시에 활성화된다면, 이 인코더는 가장 높은 비트의 입력 신호를 우선시하여 처리합니다.

2. 데이터 플로우 모델링을 이용한 4x2 인코더

데이터 플로우 모델링은 데이터의 흐름을 수식으로 표현하는 방식입니다. 아래는 데이터 플로우 모델링을 사용한 4x2 인코더의 Verilog 코드입니다.

module encoder_4x2_d(

input [3:0] signal,

output [1:0] code

);

assign code = (signal == 4'b0001) ? 2'b00 :

(signal == 4'b0010) ? 2'b01 :

(signal == 4'b0100) ? 2'b10 :

(signal == 4'b1000) ? 2'b11 :

2'b00;

endmodule이 코드는 assign 문을 사용하여 삼항 연산자로 입력 신호 signal을 평가하고, 이에 따라 출력 신호 code를 설정합니다. 조건에 따라 데이터를 직접 할당하는 방식으로 간결하게 구현되었습니다.

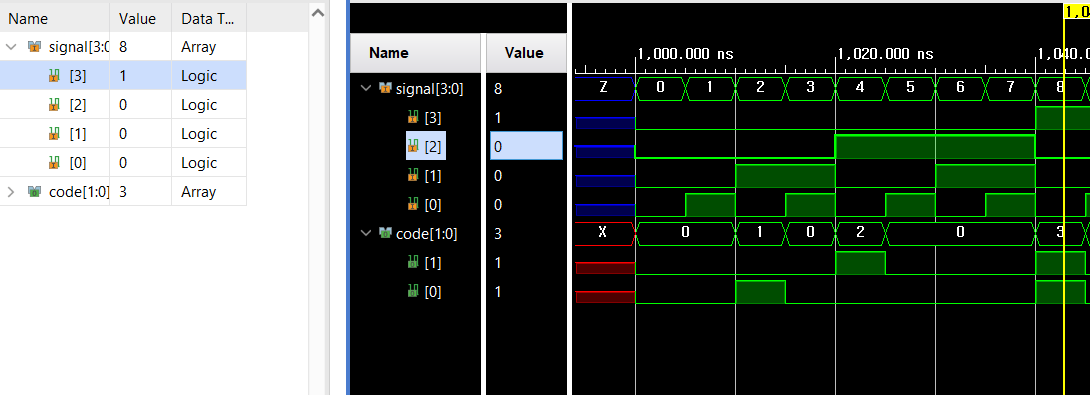

시뮬레이션 결과입니다. 각 시그널 입력 값이 들어갈때마다 code출력값이 제대로 나오는 것을 볼 수 있습니다.