Verilog HDL

1.Verilog HDL 소개

오늘은 Verilog HDL(하드웨어 설명 언어)에 대해 소개해드리려고 합니다. Verilog은 디지털 회로 설계 및 검증에 필수적인 언어로, FPGA 및 ASIC 설계에서 매우 중요한 역할을 합니다. Verilog에 대해 처음 들어보는 분들이나 더 깊이 이해하고 싶은

2.Verilog를 이용한 Half Adder 구현 예제

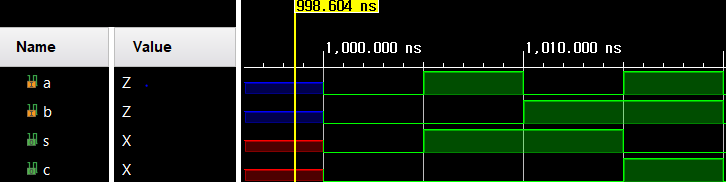

오늘은 Verilog를 사용하여 Half Adder를 구현하는 세 가지 방법을 소개하겠습니다. 각각의 방법은 구조적 모델링, 동작적 모델링, 데이터 플로우 모델링을 사용합니다. 이를 통해 Verilog의 다양한 모델링 기법을 이해하고, 각 기법의 장단점을 살펴보겠습니다

3.Verilog를 이용한 Full Adder 구현 예제

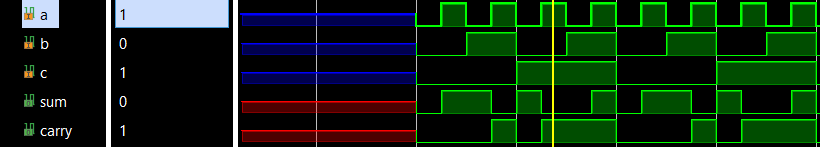

Verilog를 사용하여 Full Adder와 4비트 Adder를 구현하는 여러 가지 방법을 소개하겠습니다. 각각의 방법은 구조적 모델링, 동작적 모델링, 데이터 플로우 모델링을 사용하며, 이를 통해 Verilog의 다양한 모델링 기법을 이해할 수 있습니다.구조적 모델

4.4비트 Adder 구현 예제

오늘은 Verilog를 사용하여 4비트 Adder를 구현하는 여러 가지 방법을 소개하겠습니다. 각각의 방법은 구조적 모델링, 동작적 모델링, 데이터 플로우 모델링을 사용합니다.4비트 Adder는 4개의 Full Adder를 사용하여 구현할 수 있습니다. 아래는 구조적

5.Verilog를 이용한 비교기 구현 예제

오늘은 Verilog를 사용하여 Comparator를 구현하는 여러 가지 방법을 소개하겠습니다. 각각의 방법은 데이터 플로우 모델링과 동작적 모델링을 사용하며, 이를 통해 Verilog의 다양한 모델링 기법을 이해할 수 있습니다.데이터 플로우 모델링은 데이터의 흐름을

6.Verilog를 이용한 2x4 Decoder 구현 예제

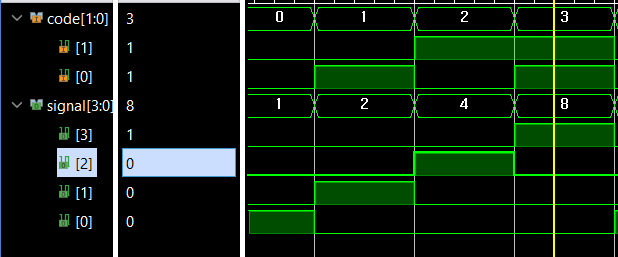

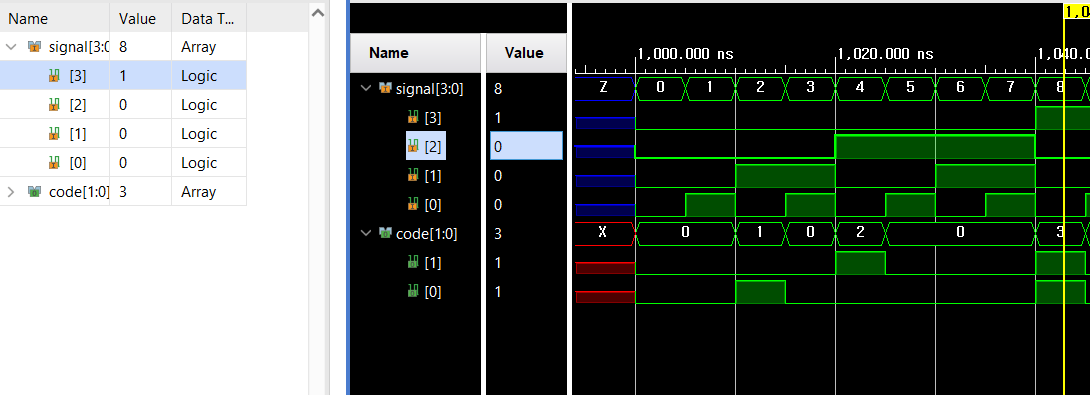

오늘은 Verilog를 사용하여 2x4 디코더를 구현하는 방법을 소개하겠습니다. 디코더는 입력된 이진 코드를 특정 출력을 활성화하여 변환하는 장치입니다. 이 글에서는 동작적 모델링과 데이터 플로우 모델링을 사용하여 디코더를 구현하는 방법을 다루겠습니다. 1. 동작적

7.4x2 인코더 구현 예제

Verilog를 사용하여 4x2 인코더를 구현하는 방법을 소개하겠습니다. 인코더는 하나의 활성화된 입력 신호를 이진 코드로 변환하는 장치입니다. 이 글에서는 동작적 모델링과 데이터 플로우 모델링을 사용하여 인코더를 구현하는 방법을 다루겠습니다.동작적 모델링은 특정 조건

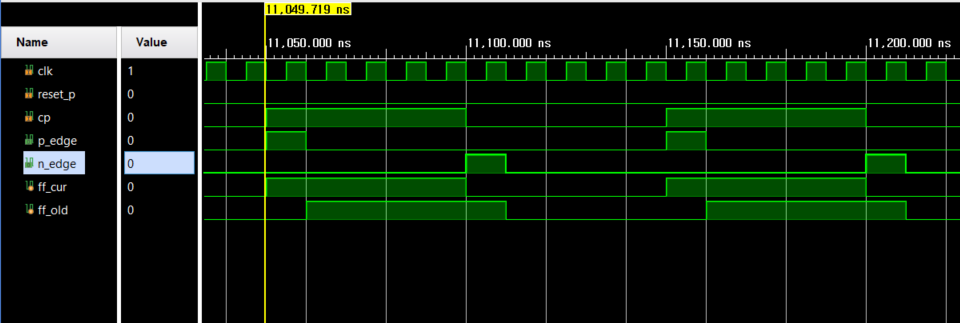

8.엣지 검출기

오늘은 Verilog를 사용해 엣지 검출기(Edge Detector)를 구현하는 방법에 대해 알아보겠습니다. 신호 처리나 디지털 시스템에서 엣지 검출기는 중요한 역할을 합니다. 신호가 특정 순간에 변할 때 이를 감지하여 트리거로 사용할 수 있기 때문입니다. 그럼 Ver

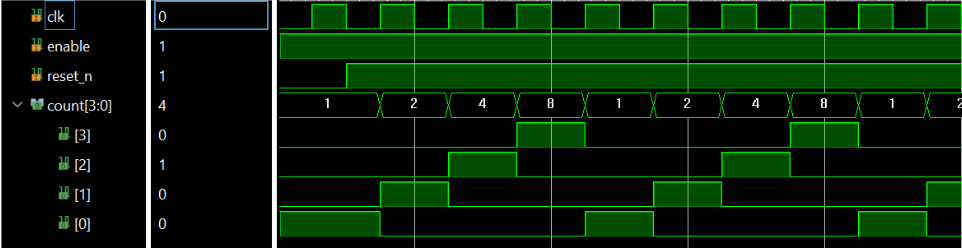

9.Verilog로 링 카운터 설계

이번 글에서는 베릴로그를 활용해 링 카운터를 설계하는 방법을 소개하고자 합니다. 링 카운터는 시프트 레지스터의 한 종류로 특정 비트가 회전하는 방식으로 동작하며 여러 디지털 시스템에서 사용됩니다.가장 간단한 형태의 링 카운터는 4비트 시프트 레지스터를 사용하여 구현됩니