오늘은 Verilog를 사용해 엣지 검출기(Edge Detector)를 구현하는 방법에 대해 알아보겠습니다. 신호 처리나 디지털 시스템에서 엣지 검출기는 중요한 역할을 합니다. 신호가 특정 순간에 변할 때 이를 감지하여 트리거로 사용할 수 있기 때문입니다. 그럼 Verilog 코드 예제를 통해 하강엣지 검출기의 원리와 구현 방법을 알아보겠습니다.

엣지 검출기란?

하강엣지 검출기는 입력 신호가 '1'에서 '0'으로 변하는 순간을 감지하는 회로입니다. 반대로 상승엣지 검출기는 '0'에서 '1'으로 변하는 순간을 감지합니다. 이 순간은 종종 중요한 이벤트를 나타내며, 이를 감지하여 시스템의 다른 부분에서 트리거로 사용할 수 있습니다. 예를 들어, 키보드에서 키를 누르는 동작을 검출하거나, 신호 전송에서 데이터의 변화 순간을 잡아내는 데 사용될 수 있습니다.

Verilog 코드로 구현하기

아래는 하강엣지 검출기를 Verilog로 구현한 코드입니다. 이 코드는 p_edge(positive edge)와 n_edge(negative edge)라는 두 개의 출력 신호를 생성하여 각각 상승엣지와 하강엣지를 검출합니다.

module edge_detector(

input clk, reset_p,

input cp,

output p_edge, n_edge

);

reg ff_cur, ff_old;

always @(negedge clk or posedge reset_p) begin

if (reset_p) begin

ff_cur <= 0;

ff_old <= 0;

end else begin

ff_cur <= cp; // 현재 cp 값을 ff_cur에 저장

ff_old <= ff_cur; // 이전 ff_cur 값을 ff_old에 저장

end

end

assign p_edge = (ff_cur == 1 && ff_old == 0) ? 1 : 0; // 상승엣지 검출

assign n_edge = (ff_cur == 0 && ff_old == 1) ? 1 : 0; // 하강엣지 검출

endmodule코드 설명

1. 입력과 출력

clk : 시스템의 클럭 신호

reset_p : 리셋 신호로, high신호에서 리셋이 활성화

cp : 감지하고자 하는 신호

p_nedge : 상승엣지 검출 신호

n_edge : 하강엣지 검출 신호

2. 레지스터

ff_cur: 현재 클럭 주기에서의 cp 신호 상태를 저장

ff_old: 이전 클럭 주기에서의 cp 신호 상태를 저장

3. 동작

always @(negedge clk or posedge reset_p): 클럭의 하강엣지에서 ff_cur와 ff_old를 갱신합니다. 리셋 신호가 활성화되면 두 레지스터는 0으로 초기화됩니다.

assign p_edge: ff_cur가 1이고 ff_old가 0일 때 p_edge가 1로 설정됩니다. 이는 상승엣지를 의미합니다.

assign n_edge: ff_cur가 0이고 ff_old가 1일 때 n_edge가 1로 설정됩니다. 이는 하강엣지를 의미합니다.

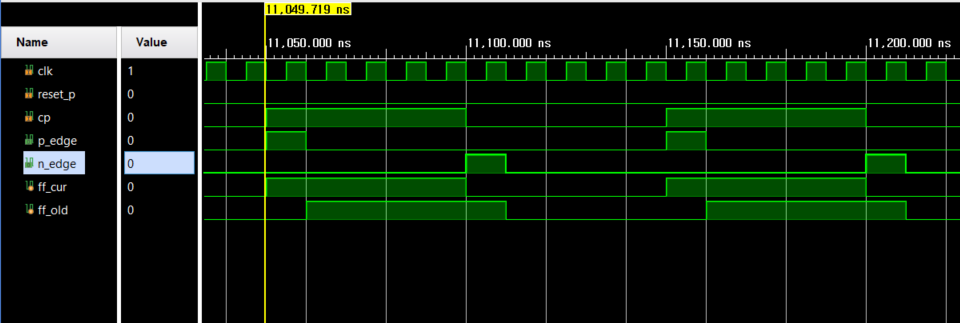

시뮬레이션 결과

cp의 상승엣지와 하강엣지에서 p_edge와 n_edge가 클럭의 한 주기로 생성된 모습을 볼 수 있습니다.

활용 예)

엣지 검출기는 다양한 디지털 회로 설계에서 유용하게 사용됩니다. 예를 들어, 버튼이 눌릴 때 발생하는 노이즈를 제거하거나, 신호의 변화에 민감하게 반응해야 하는 타이밍 제어 장치에 사용할 수 있습니다.