Virtual Memory

프로세스마다 할당되어, 실제 메모리 공간보다 훨씬 큰 가상의 공간을 할당하여 프로세스가 마음놓고 메모리를 사용하도록 하는 것 (Disk 기반)

서로의 메모리 공간을 침범하지 않도록 하는 것이 중요

하드웨어쪽에서는 소프트웨어에서 사용하기 편리하도록 구조를 잡아놓아야 하고,

소프트웨어는 사용자가 사용하기 편리하도록 여러 가지 기능들을 만들어 놓아야 한다.

Disk Block는 VM Page에 해당

VM Translation Miss는 Page fault

이 처럼 각각의 용어에 대한 개념이 거의 비슷하다.

2 Parts of VM

1) Naming and Protection

각각의 프로세스에게 크고 연속적인 메모리 공간을 할당하고,

다른 프로세스의 메모리에서 이를 침범하지 못하도록 보호하는 것

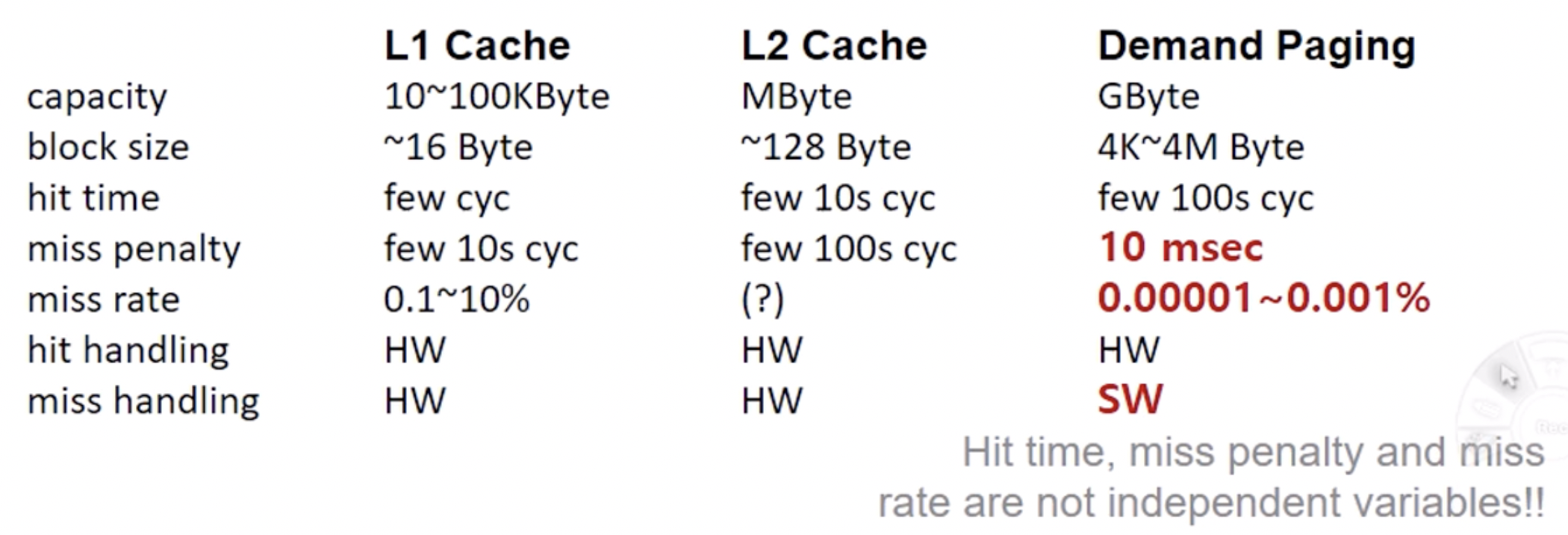

2) Demand Paging (for hierarchy)

자주 사용되는 데이터는 고속의 메모리에 저장하고,

그렇지 않은 데이터는 Disk등에 저장하여 메모리를 효율적으로 관리하는 것

Address Mapping

물리적 저장 공간은 작지만, Mapping등을 통해 메모리를 원활하게 관리해 주어야 한다.

사용자는 Effective Address(EA)로 메모리에 접근

하드웨어는 받은 EA를 Physical Address(PA)로 변환시켜서 실제 저장공간에 접근

변환은 Page Table을 거치게 된다.

이 때 OS에 의해 관리되어, Protection 절차를 거치게 된다.

이 변환 과정을 Translation(또는 Mapping)이라 함

Virtual Memory System

VM이 없다면

CPU -> DRAM(Main Memory)로 바로 접근

VM이 있다면

1. CPU에서 Virtual Address를 Page Table로 보냄

2. Page Table에서 Physical Address로 변환

3. 현재 DRAM(Main Memory)에 데이터가 올라와 있다면 DRAM에서 바로 데이터에 접근

4. Page Fault 발생하면 Disk에서 데이터 접근

Page Table

Virtual Address가 들어오면, 해당 VA에 Mapping되는 Physical Address가 존재

그 PA를 가지고 Cache 또는 Main Memory에 접근하게 된다.

Page Table에는 Main Memory에 데이터가 있는지 없는지 표시가 되어 있어, 데이터가 없다고 표시가 되어 있다면 바로 Disk에 접근

이 때 Disk는 Main Memory보다 용량이 훨씬 크기 때문에, Page Fault가 발생할 수 밖에 없다. 이 Fault를 최소화 시키는게 중요

Page Table은

Valid Bit,Access Rights,Frame으로 구성

- Valid Page

Access Rights가 허용되면 Physical Address로 바로 접근

허용되지 않으면Protection fault발생 - Invalid Page

Page Fault를 발생시켜, 처리 작업을 OS로 넘김

Page Fault

Page Fault가 일어나면, 처리해야 할 단계가 많아 시간이 오래 걸리게 된다.

Page Size가 크기 때문에 miss rate는 굉장히 작지만, 한 번 Fault가 일어나게 되면 10ms라는 오랜 시간을 소모해야 한다.

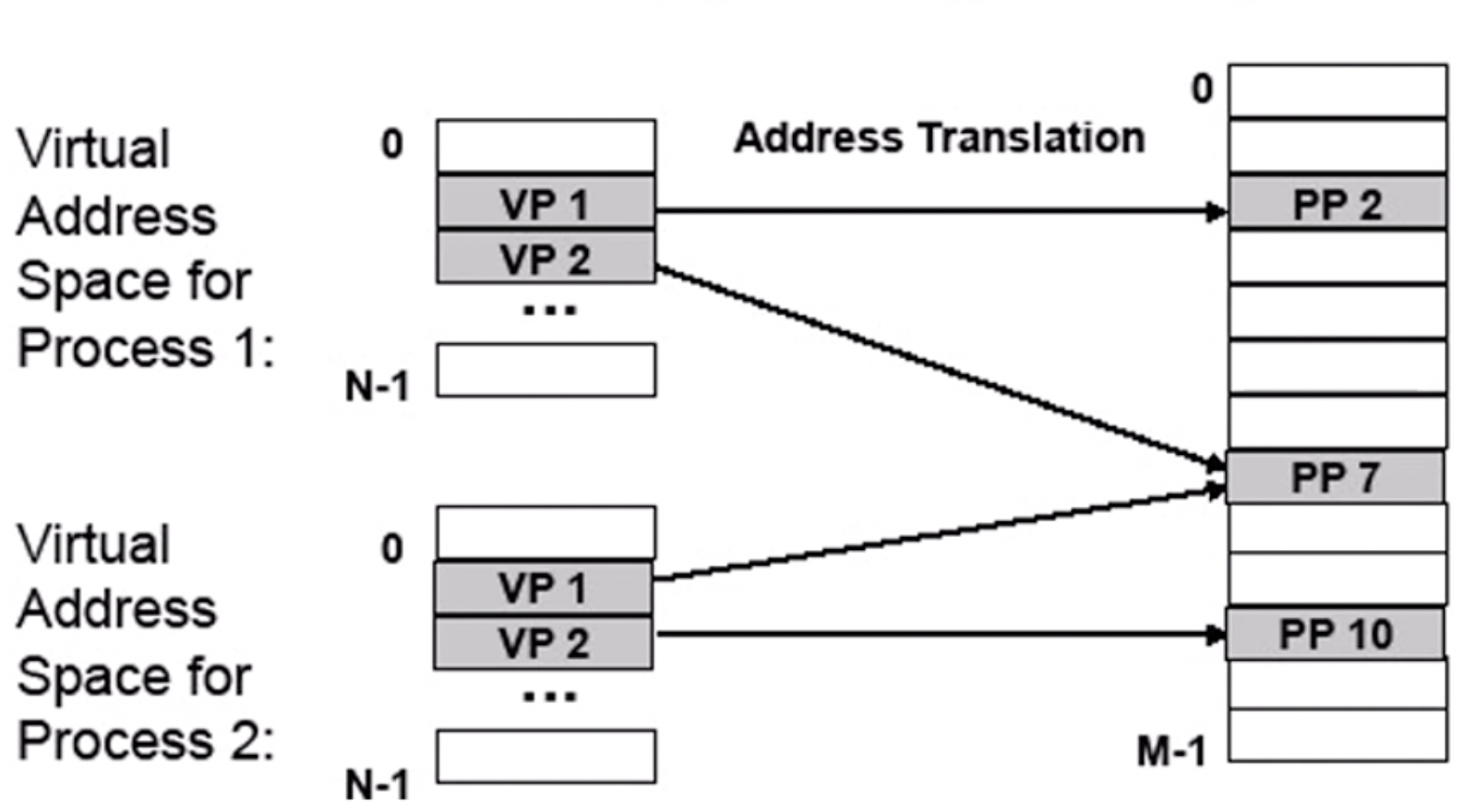

Memory Protection

두 사용자가 있고, 각각의 사용자에게 Virtual Memory를 할당해 주면

각각의 사용자의 VP1이라 해도 Page Table을 거쳐 각기 다른 Physical Memory로 변환되면 실제 메모리 주소인 PA가 나오게 된다.

위 사진의 경우 VP1은 Data Sharing

Memory Protection이 없다면,

- 여러 사용자의 여러 프로세스를 관리(Multitasking)하는 것이 불가능

- 사용자가 직접 PA에 접근

Access Protections

기본적으로 R(Readable), W(Writeable), E(Executable)

Normal Data Segment: RW(!E)

Shared Data Segment: R(!W)(!E)

Code Segment: R(!W)E

Illegal Segment: (!R)(!W)(!E)

각각의 정보를 Page Table에 기록

Virtual Memory Problem

Page Table이 Main Memory에 있으므로, 실제 데이터에 접근하기 위해서는

Main Memory를 2번 접근하는 꼴이 된다.

그래서 속도가 빠른, Cache 기능을 갖고 있는 Page Table이 생성

--> TLB

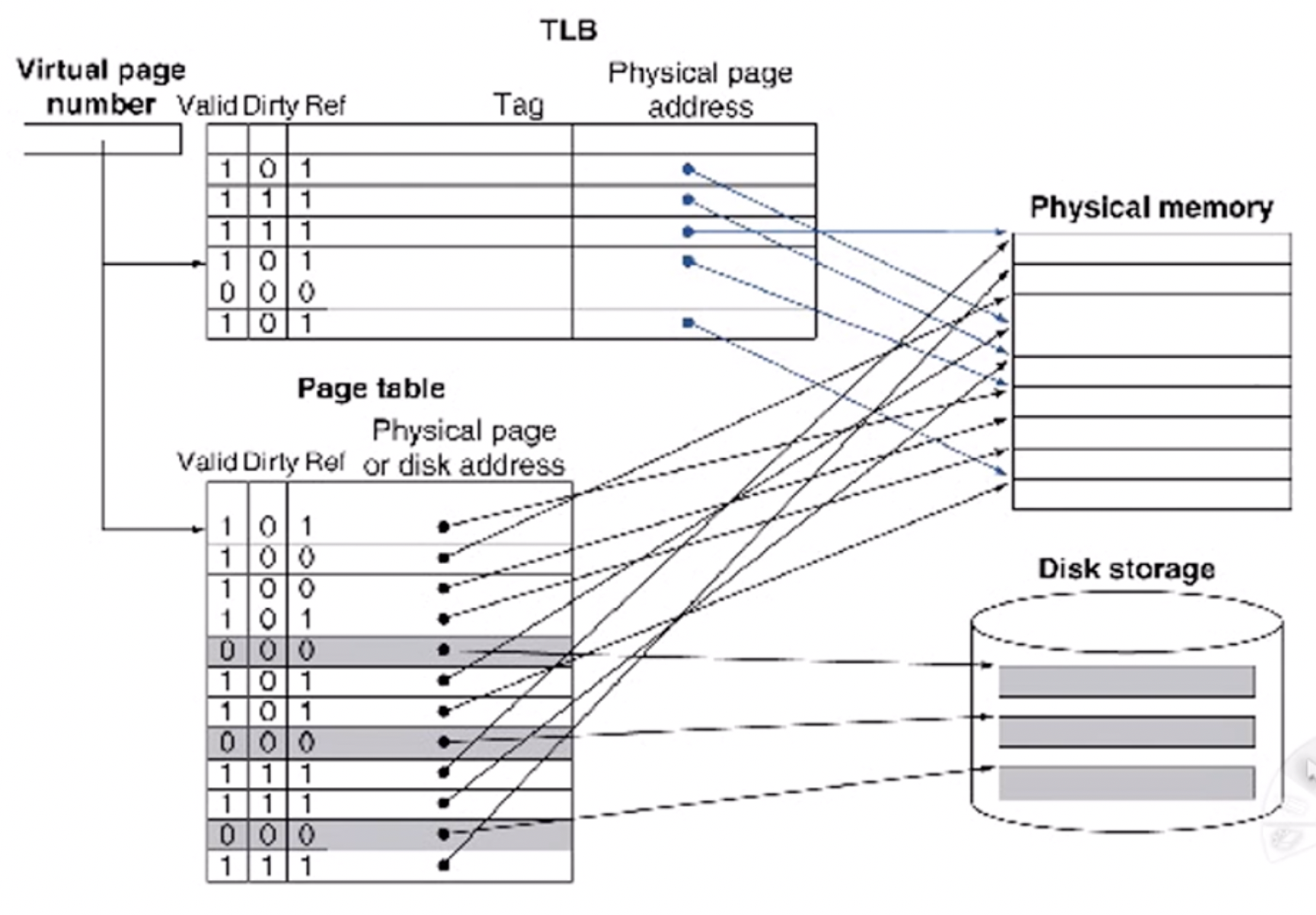

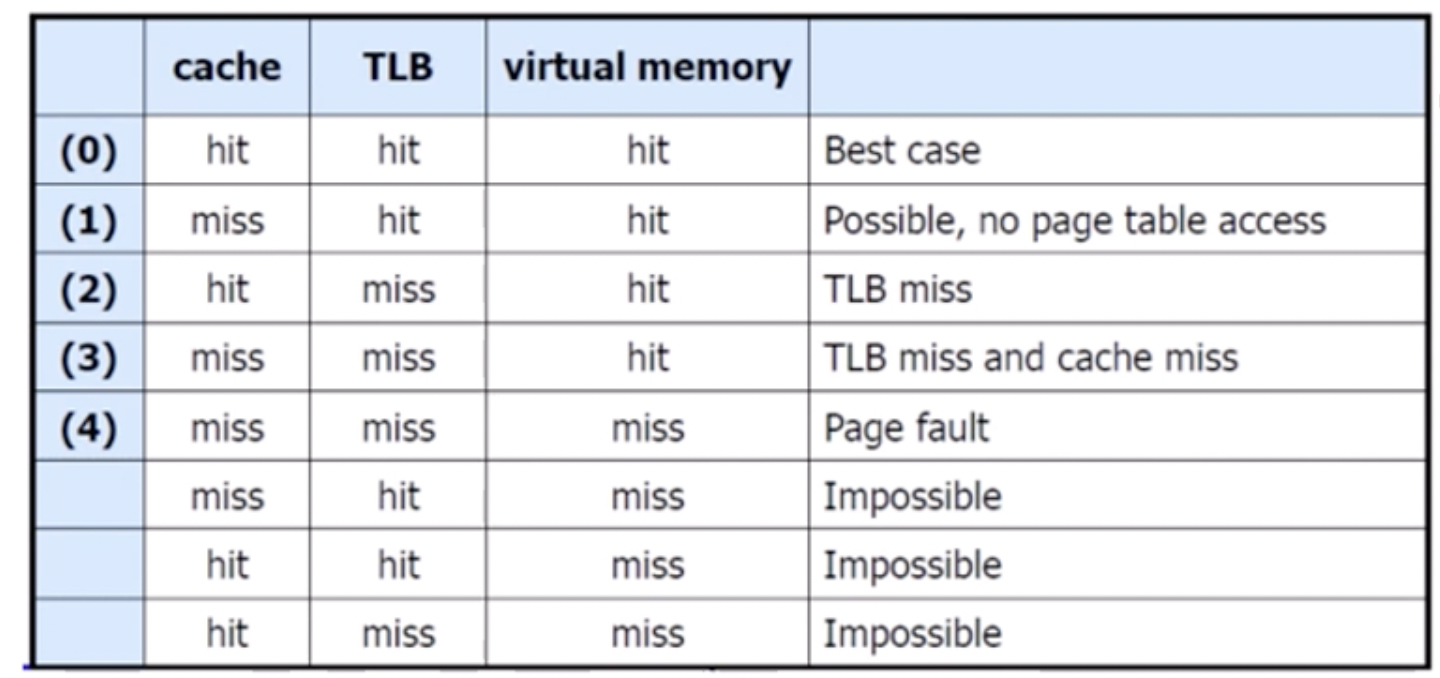

TLB (Translation Lookaside Buffer)

Virtual Page Number가 들어오면

1. TLB에서 해당 VP에 해당하는 PA가 있는지 확인, 있다면 바로 PA로 접근한다. 접근 시 바로 Main Memory로 가는 것이 아닌, Cache를 먼저 확인하게 된다.

2. (1)에서 없다면, Page Table을 확인, 있다면 해당 PA로 접근

3. (2)에서 없다면, 최종적으로 Disk접근

TLB는 Page Table의 내용에, Dirty, Ref정보가 추가로 담겨 있다.

Dirty

해당 데이터가 변경되었는지에 대한 정보Ref

해당 데이터가 얼마나 자주 접근되었는지에 대한 정보

단점

Process Switching이 일어날 때, TLB의 내용을 모두 비워야 한다.

Multitasking이 많으면 많을수록 TLB의 활용도가 떨어짐