PLL 성능에 큰 영향을 미치지 않고 간단한 PFD, Divider를 먼저 설계하였다.

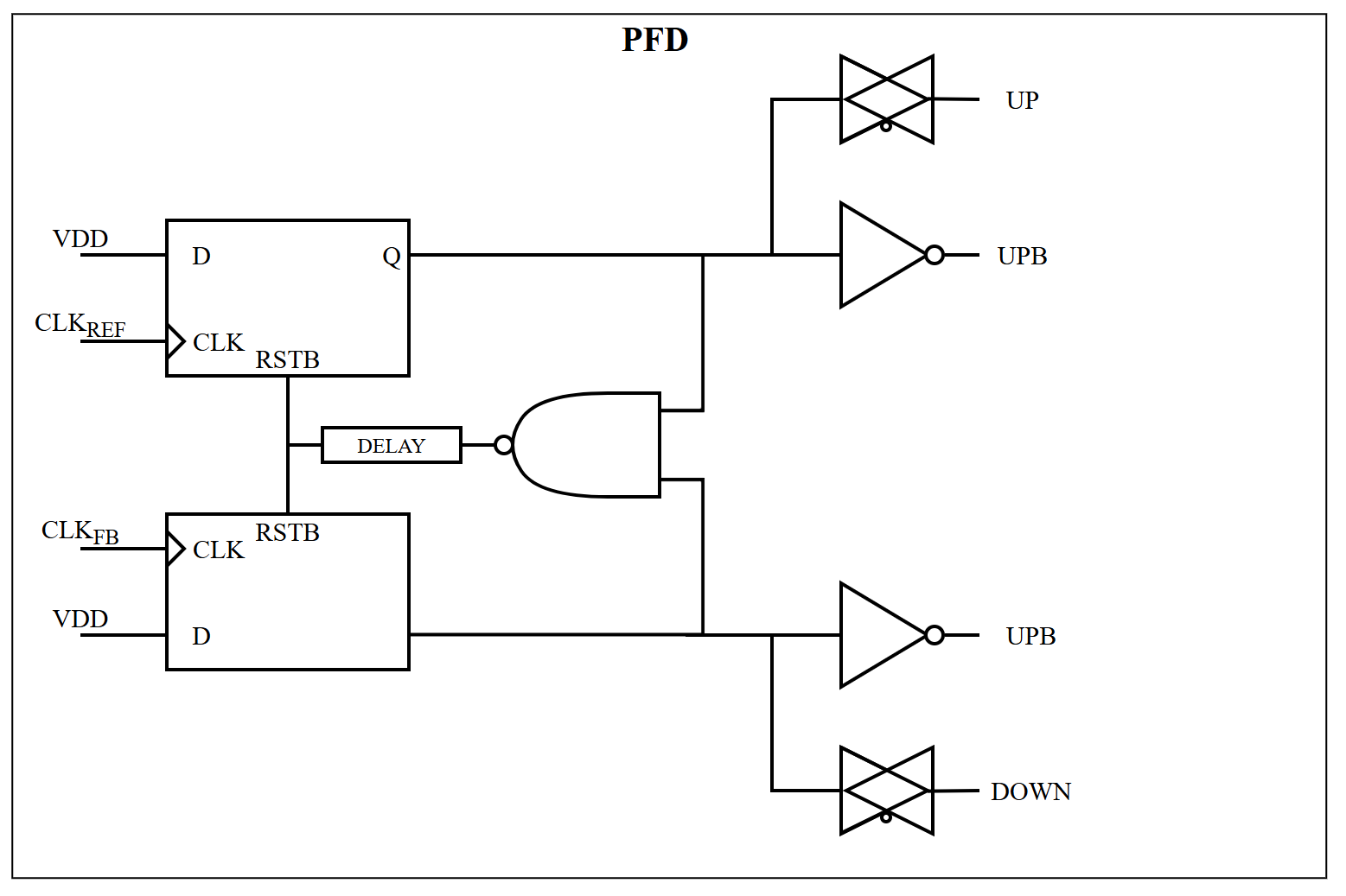

내가 이번에 사용한 PFD의 구조는 기본적인 구조의 PFD로, 다음과 같다.

내가 사용할 Charge Pump는 UP, DOWN 신호 외에도 UPB, DOWNB이 필요하기 때문에 Inverter를 사용하고, Charge Pump에서 신호 간 Delay로 인한 특성 악화를 방지하기 위해 1개의 Inverter와 최대한 비슷한 Delay를 갖는 Transmission Gate를 설계하여 사용하였다.

Blind-Zone을 해결하기 위한 Reset 신호 Delay로는 Inverter를 짝수단으로 사용하였으며, 시뮬레이션을 통해 적당한 Delay값을 갖는 단수를 선정하였다. 저속인 PFD에서는 생각보다 많은 수의 Inverter를 사용해야 유의미한 변화가 있었다.

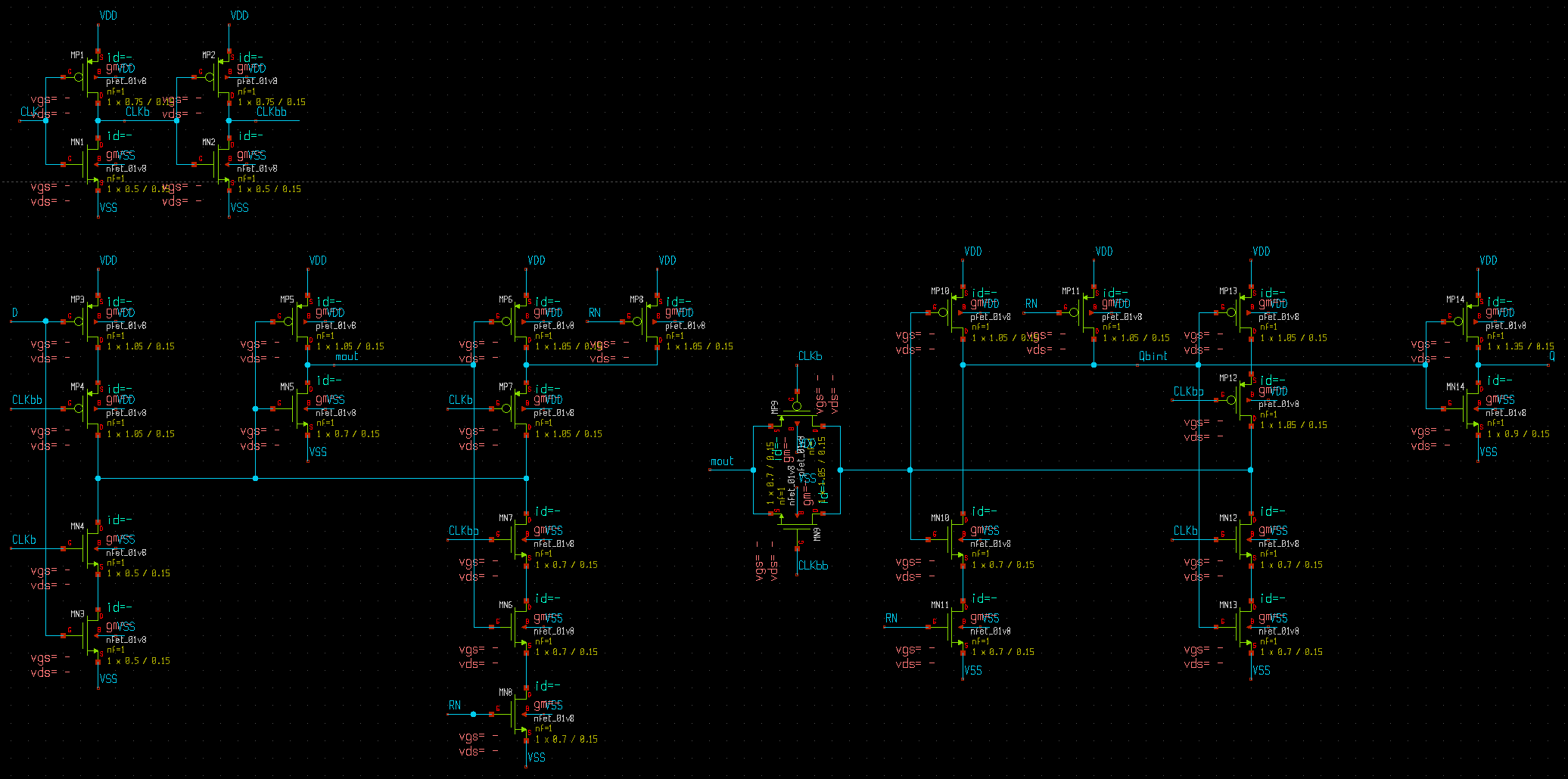

D-Flip Flop의 경우, Master-Slave DFF를 사용하였다. 처음에는 Divider에서 재사용할 것을 염두해서 비교적 고속에서도 잘 동작하는 TSPC DFF를 사용하였다. 하지만 PFD를 완성하고 시뮬레이션 하였는데, 제대로 동작하지 않고 UP과 DOWN이 동시에 1이 되어야 하는 부분에서 Ringing이 발생하였다.

원인을 파악한 결과, DFF이 일반적인 상황에서는 Edge-Triggered로 작동하였지만 ResetB가 0에서 1로 바뀌었을 때 Clock이 High인 경우, Positive Edge가 아닌데도 출력이 변하는 것을 확인할 수 있었다. 이로 인해 DFF가 Reset되고, 아직 Positive Edge Clock이 아님에도 바로 D가 출력에 반영되어 출력값이 Reset 되고 1이 되기를 반복하여 Ringing 하였던 것이었다.

문제를 해결하기 위해, 상대적으로 저속(Reference CLock Frequency 근처)으로 동작하는 PFD의 특성을 고려하여, 확실하게 Edge-Triggered 되는 Master-Slave 구조의 DFF로 교체하였고, 문제를 해결하였다.

<사용한 D-Flip Flop의 Schamatic>