N줄 요약

- IBM은 5월 6일, 2nm 칩셋을 만드는 독자 기술을 발표했다.

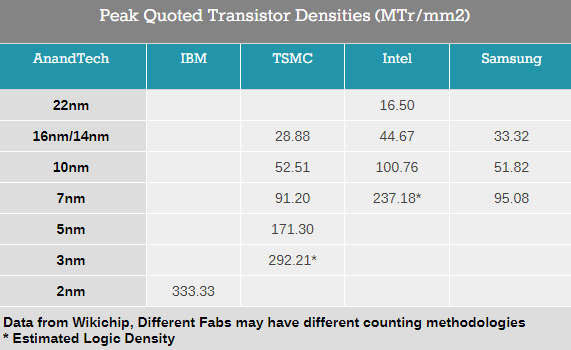

- 2nm 칩셋의 도입으로 트렌지스터 밀도는 333.33MTr/mm²를 달성했다.

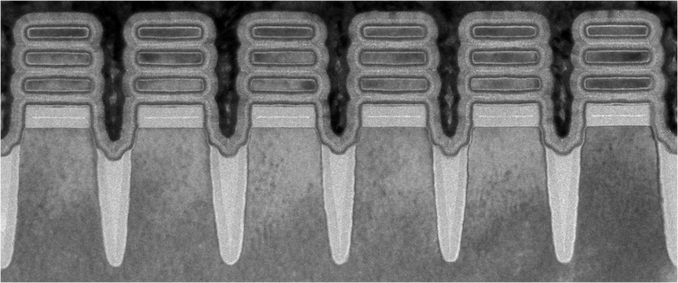

- IBm의 2nm 칩셋은 삼성의 GAAFET을 3-stack으로 사용한 것으로 보인다.

- 성능은 동일전력에서 45%, 전성비는 동일성능에서 75% 수준인 것으로 밝혔다.

요약

IBM은 이번 5월 6일에 독자 기술로 개발한 2nm 반도체 칩을 공개했다. 7nm 칩 대비 성능은 동일전력에서 45%, 전성비는 동일성능에서 75% 수준인 것으로 밝혔다. 자사의 Nanosheet 기술을 활용하면, 150mm² 크기에 최대 500억개의 트렌지스터를 실장해서 333.33MTr/mm²를 달성할 수 있다고 밝혔다.

IBM의 2nm 칩은 3-stack GAA로 설계됐다. 삼성은 3nm, TSMC는 2nm, 인텔은 5nm부터 GAA를 도입할 것으로 예상되는 것을 근거로 양산까지는 아직 시간이 많이 걸릴 것으로 보인다.

이 날 IBM이 밝힌 2nm 칩 제조를 위한 핵심 기술은 세 가지가 있다.

- Bottom Dielectric Isolation (바닥 유전체)

- Nanosheet와 Wafer 사이의 leakage current를 줄이기 위한 기술

- Inner Spacer dry process (등방성 건식 식각)

- 칩 내부 공간을 건조하게 만듦

- 게이트의 크기를 정밀하게 조절할 수 있는 환경을 조성함.

- Multi Vt Scheme (다중 임계 전압 전략)

- 칩이 활용되는 분야 (field, application)에 최적화된 문턱 전압을 조성해주는 기술.

감상 및 의견

반도체의 발전이 이전만큼은 아니라지만, 그래도 정말 무시무시하게 빠르다는 생각이 들었다. 우리는 인텔 덕분에 꽤 오랜 시간 14nm 얘기만 듣고 있었다. 엇 하는 사이에 AMD의 7nm Zen 3 프로세서가 등장하며 우후죽순 이곳저곳에서 7nm 공정을 사용한 제품이 나오기 시작했다. 체감상으로는 12nm, 10nm는 훅 뛰어넘어서 바로 절반으로 feature size가 줄어든 기분이다. 그러다가 Apple의 M1 칩으로 5nm 제품이 게임 체인저로 활약하면서 이젠 TSMC의 N5, N5P 공정이 종종 입에 오르내리곤 한다. 이런 흐름 속에서 이제는 IBM이 2nm 칩을 개발했다며 들고나왔다. 매번 '한계다', '더는 줄일 수 없다', '반도체의 한계 때문에 이제는 무리다.' 곡소리를 내면서도 2, 3년마다 한 단계씩 업그레이드해내는 플레이어들과 엔지니어들이 정말 대단하고 존경스럽다.

IBM의 발표자료에는 트랜지스터의 폭, 높이 그리고 피치는 있지만, 정작 2nm가 어디인지는 밝혀지지 않았다. 그 부분을 알 수 있었으면 좋았겠다는 아쉬움이 있었다. IBM은 이번 칩에 3-stack GAA를 사용했다. 이것으로 FinFET의 다음 세대를 책임질 구조는 GAA 또는 MBCFET인 것은 기정사실인 것으로 보인다. IBM은 현재 GlobalFoundary와 삼성전자 그리고 인텔과 일하고 있다. 따라서 2nm 양산에서 삼성전자가 어느 정도 역할을 할 것으로 예상된다. IDM 2.0으로 파운드리 진출을 선언한 인텔도 여기에 껴있다는 점이 쎄한 느낌이지만...

2nm 칩 개발로 300억대 밀도를 달성한 것은 놀라운 일이다. 하지만 이제 우리는 뼈저리게 알다시피, 높은 밀도가 반드시 성능 향상을 끌어오지는 않는다. 발열과 효율 문제를 확실하게 해결하지 못한다면 저번 삼성전자의 엑시노스 2100처럼 발열 문제로 소비자로부터 질타를 받을 수 있기 때문이다. 인텔이 14나노, 10나노 깎는 장인이라며 놀림당하지만, 그래도 '장인' 취급받는 이유가 있다. Feature size에서 큰 이득을 못 보고 다른 플레이어들보다는 느리지만, 계속해서 밀도를 2배씩 안정적으로 늘려가고 있기 때문이다. 결론적으로, 갑작스러운 2nm 칩의 도래지만, 페이스를 잃지 않고 각 플레이어가 자신들이 가진 장점은 그대로 유지한 체로 안정적이고 균형적인 발전으로 큰 이슈 없이 2024년, 2025년에는 2nm 칩 양산에 들어갈 수 있으면 좋겠다.