요약

삼성전자는 차세대 2.5D 패키지 기술인 'I-Cube 4'를 개발했다고 밝혔다.

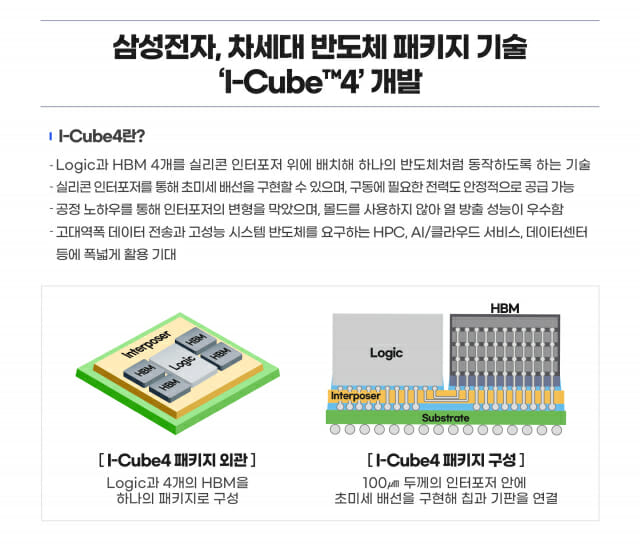

'I-Cube4'는 하나의 로직칩과 4개의 고대역폭 메모리 칩(HBM)을 하나의 패키지로 구현한 차세대 패키지 기술을 말한다. 'I-Cube4'는 단일 패키지 안에 다수의 HBM을 배치해서 전송속도를 높이면서 패키지 면적을 줄인다.

일반적으로 HBM은 칩과 칩 사이의 연결을 위해서 인터포저*(Interposer)를 삽입하게 되는데, 패키지 내부에 HBM이 많아질수록 인터포저의 면적이 비례해서 증가하기 때문에 공정상에 어려움을 겪게된다.

삼성전자는 매우 얇은 TSV 인터포저를 자사의 반도체 공정 노하우를 적용해서 적용했기 때문에 변형 위험이 적다고 밝혔다. 또한, 몰드*(mold)를 사용하지 않는 독자적인 구조를 적용해서 효율적인 열 방출을 이뤄냈다고도 밝혔다.

**인터포저(Interposer): IC칩과 PCB 사이의 회로 폭 차이를 완충시키는 미세회로 기판. HBM은 엄청 회로 밀도가 높은 반면에 PCB는 낮기 때문에 두 layer의 차이를 보완해줄 역할을 할 인터포저가 필수임.*

**몰드(Mold): 패키지 공정 중 발생 가능한 습기, 진동, 충격으로부터 칩을 보호하기 위해 열경화성 수지를 사용하여 칩을 감싸는 소재*

감상 및 의견

후공정과 패키징의 중요도가 지속적으로 증가하고 있다. 우수한 성능을 가진 SoC를 만들기 위해서는 CPU-메모리 간 병목을 최대한 줄여줘야 하는데, HBM이 탁월한 솔루션이 돼줄 것으로 생각한다.

먼 미래에는 SRAM, DRAM, NAND flash 라며 구분하던 메모리는 지금의 플로피디스크마냥 과학책에서나 보게 되고, SoC 혹은 CPU 자체에 HBM이나 NVM이 내장되지 않을까?