- 이번에 배울 내용은 증착 공정입니다. 일반적으로 반도체 8대 공정은 '증착 공정'과 '이온주입 공정'을 하나로 묶어서 다루고 있지만 내용이 너무 방대해지기 때문에 본 포스트에서는 두 공정을 분리해서 설명하도록 하겠습니다.

- 증착 공정을 공부하는 방법은 이전 공정들과 마찬가지로 전체적인 스토리를 개요 수준으로 간략하게 이해하되 서로 다른 증착 방법 및 종류에 집중해서 공부하시면 됩니다. 각 증착 방법이 탄생할 수 밖에 없었던 이유를 증착 공정이 마주한 문제상황들과 연관지어 이해하시면 됩니다.

1. 개요

1.1. 증착 공정이란?

- 증착 공정(Thin film Deposition)은 현대 CMOS 공정의 표준으로 자리잡은 공정 중 하나입니다.

- 이때 thin film이란, 기계 가공으로는 실현 불가능한 1㎛ 이하의 얇은 막을 의미합니다. 이정도로 얇은 막은 일반적인 방법으로는 실현이 불가능하므로 화학적인 방법으로 원자 단위로 증착하게 됩니다.

- 집적도가 굉장히 높은 현대 공정은 layer와 layer 사이에 전기적 신호를 굉장히 작고 얇은 hole과 via를 통해 전달하기 때문에 DC delay나 noise에 굉장히 예민하게 반응합니다.

- 그러므로 최대한 전기신호가 누설되지 않으면서 각 layer를 확실하게 구분하고 보호해주기 위해서 서로 다른 물질을 layer 단위로 위로 쌓아 올리면서 내부 회로를 구현하는 과정을 'Thin Film", 박막 증착 공정이라고 이해하시면 됩니다.

1.2. 관련 용어 정리

- Uniformity

- Wafer 전체에 일정한 두께로 target material이 증착됐는지에 대한 특성을 의미합니다.

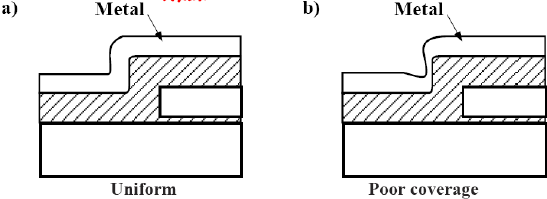

- Step Coverage

- Step coverage는 uniformity를 객관적으로 나타내는 지표입니다.

- 평평한 면에서의 두께와 hole 또는 via의 옆쪽 벽면에서의 두께의 비율 로 계산합니다.

- Step coverage가 높을 수록 wafer 표면의 모든 면이 일정한 두께로 잘 증착됐다고 판단할 수 있습니다.

- Aspect Ratio

- Aspect ratio는 증착 난도를 객관적으로 나타내는 지표입니다.

- 상이한 두 물질간의 증착 공정에서 step coverage만 비교하는 것은 의미없습니다. 같은 1등급이라도 수학 '가'형에서 맞은 것과 '나'형에서 맞은 건 분명히 다른 것과 같습니다.

- Aspect ratio는 로 나타내며 이 값이 높을수록 입구는 좁은데 높이는 길다는 의미이므로 공정 난도가 확 올라가게 됩니다. 따라서 채움성이 아주 좋은 물질을 사용해야겠죠.

- Mean Free Path

- Mean Free Path는 분자가 다른 분자와 충돌하지 않고 이동할 수 있는 평균 거리를 의미합니다.

- 높은 mean free path는 그만큼 분자가 직진성 좋게 이동했다는 것을 의미하고 이는 높은 step coverage를 보장합니다.

- Adhesion

- 증착하려는 target material의 접착력(adhesion)이 충분하지 않다면 증착한 물질이 떨어지게 됩니다.

- 예를 들어 도선으로 사용하기 위해 합금을 증착하려 할 때, 이 합금은 접착력이 낮은 물질이기 때문에 접착력을 끌어올려줄 다른 물질()을 사전에 증착시킨 뒤 합금을 증착해야 합니다.

1.3. 좋은 증착공정을 위한 조건

증착 공정이 잘됐는지 여부를 판단하기 위해서는 아래와 같은 세 가지 조건에 대해 고려해야합니다.

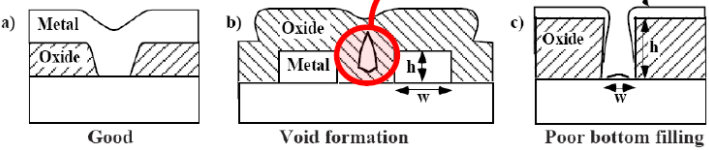

- Good filling of spaces (채움성이 좋은가)

- 집적도가 높아지면서 via나 hole의 두께는 상상 이상으로 작고 얇아지기 시작했습니다.

- 구멍이 얇고 작아질수록 내부를 채우기 어려워집니다. 따라서 채움성이 좋은 물질로 증착을 하지 않으면 via와 hole을 제대로 증착할 수 없게 되서 마치 도선이 단락된것과 같은 안좋은 효과가 나올 수 있습니다.

- Good uniformity and "Step Coverage"(일정한 두께로 plane하게 증착됐는가)

- Wafer 전체에 일정한 두께 (uniformity)로 layer를 증착하지 않으면 식각 공정(etching)에서 어느 부분은 과식각이 발생할 수도, 다른 부분은 식각이 제대로 이뤄지지 않아 후공정에서 contaminants로 작용할 수 있습니다.

- 따라서 일정한 두께로 증착이 됐는지를 판단하는 지표로 "Step Coverage"라는 지표를 사용하고

- 옛날에는 증착 후 좋은 해상도와 DoF 확보를 위해 CMP (Chemical-Mechanical Polishing)를 통해 표면을 매끄럽게 갈아버리는 방법을 사용했지만, 이제는 증착과 동시에 자동으로 planarization 될 수 있도록 spin 코팅을 응용한 spin-on-dielectric 방법으로 채움성과 uniformity를 동시에 높게 확보하는 방법을 사용합니다.

- Good composition with good electrical properties. (좋은 전기적 특성을 지닐 수 있는 조성비를 가지는가)

- Chip을 만들기 전에 추출한 요구사항에 맞는 전기적 특성을 가질 수 있도록 다양한 물질을 적절한 조성비로 섞은 뒤 증착을 시도해야할 것입니다.

- 소자의 전기적 특성이 악영향을 받지 않기 위해 반드시 low contamination을 유지해야 합니다.

1.4. 증착공정이 마주한 문제

공정의 미세화가 점점 진행될수록 증착 공정 역시 short channel effects로 인해 아래와 같은 세 가지 issue에 직면하게 됐습니다.

1.4.1. Step Coverage Issue

- 앞서 언급했다시피 hole과 via가 점점 작아지면서 내부 공간을 좋은 step coverage를 유지하면서 증착시키기가 굉장히 까다로워지고 있습니다.

- 위 그림을 보면, 좌측 그림은 높낮이에 따라 일정한 두께로 물질이 증착되는 것을 확인하실 수 있습니다. 반면에 우측 그림은 단차가 생기는 부위에 증착이 얇게 되면서 안좋은 step coverage를 갖게 되는 것을 확인하실 수 있습니다.

- Step coverage가 우측 그림처럼 낮아지게 되면 만일 hot carrier effect 같은 고온을 유발하는 문제가 발생할 경우 저 얇게 증착된 부분이 단선이 될 위험이 있습니다.

1.4.2. Filling Issue

- 앞서 언급했다시피 hole과 via가 점점 작아지면서 내부 공간을 채우기가 점점 어려워지고 있습니다. 머릿카락 두께의 구멍에 물이 들어가기 쉽지 않은 것과 비슷한 상황입니다.

- 채움성이 좋은 물질을 사용하지 않으면 가뜩이나 어려워지는 filling 과정에서 via와 hole을 제대로 금속 물질로 채우지 못해 단선이 될 위험이 있습니다.

1.4.3. Dimension Issue

- 앞서 살펴본 두 문제와 연장선상에 있는 문제입니다. 미세화 및 대용량화가 동시에 일어나면서 2D plane 구조에 한계를 느낀 최근 공정은 점점 3D 구조를 택하고 있습니다.

- 이어한 추세는 NAND의 3D VNAND와 DRAM의 VCAT 구조에서 확인하실 수 있지요.

- 2D 구조가 3D가 되면서 이번에는 완전히 새로운 방향에 대해서도 증착이 이뤄져야 하는데 문제는 새로운 방향에 대한 증착이 굉장히 어렵다는 점입니다.

- 따라서 원자 단위로 세밀한 컨트롤이 가능한 새로운 증착 방법이 요구됐고 후술할 ALD가 바로 그 방법입니다.

2. 증착 방법 종류

2.1. PVD vs CVD

- 증착 방법은 큰 범주에서 보자면 PVD (Physical Vapor Deposition)과 CVD (Chemical Vapor Deposition)으로 나뉩니다.

- 영문 명칭에서 유추하실 수 있다시피 PVD는 물리적인 방법을 사용해서 증착을 하고, CVD는 화학적인 반응을 사용해서 증착을 시도합니다.

2.2. PVD의 종류

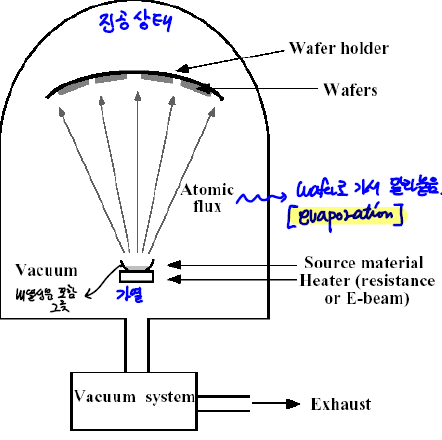

2.2.1. Thermal Evaporation

- PVD 중 가장 고전적인 방법은 열과 증발을 이용한 증착 방법인 Thermal evaporation입니다.

- 진공 상태의 chamber에 원하는 물질 (Source material)이 들어있는 내열 성분의 그릇을 놓고 가열을 합니다.

- 가열되어 증기형태로 날아가는 물질이 chamber의 천장 부분에 있는 wafer에 달라붙어 증착됩니다.

- 한 눈에 봐도 아시겠지만 step coverage가 당연히 나쁠 수 밖에 없고 조절도 불가능한 증착 방법입니다. 따라서 현대 반도체 공정에서 이 방법은 사용하지 않습니다.

2.2.2. Sputtering Deposition

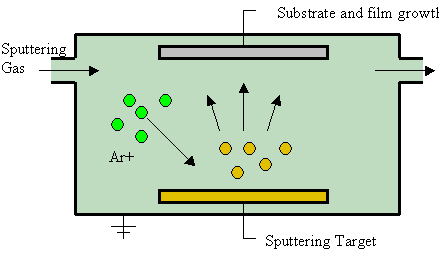

-

현대 반도체 공정에서 사용하는 PVD가 있다면 바로 이 sputtering 방법을 의미합니다.

-

Sputtering 증착 방법은 보통 도선으로 사용할 같은 합금을 증착할 때 사용합니다.

-

상단의 그림은 sputtering 방법의 과정을 보여주는 그림입니다.

- 진공관에 target material 금속 판을 놓고 sputtering을 진행해줄 촉매 역할 기체를 넣습니다. (보통 이 기체는 을 사용하니 알아둡시다.)

- 외부에서 열과 강한 DC 음전압을 걸어주면 내부의 sputtering gas가 플라즈마로 변하며 가속하며 target material 금속 판과 강하게 충돌합니다.

- 이때 target material 분자가 튕겨나오면서 상단의 wafer substrate에 달라붙게 됩니다.

-

2.2.1절의 방법과 비교하면, source를 작은 그릇에서 넓은 판으로 바꾸면서

-

상대적으로 target material 금속 이온의 직진성을 높혀서 wafer에 고르게 증착되도록 시도한 점

-

고밀도의 플라즈마를 사용해서 직진성을 향상시켜서 hole, via 바닥쪽의 증착률을 높혀 채움성을 좋게 만들려고 시도한 점

-

Target material 까지의 거리가 균일하여 최대한 정교하게 uniformity를 확보할 수 있다는 점

에서 장점을 얻을 수 있습니다.

-

2.3. CVD의 종류

2.3.1. 일반적인 CVD 과정

일반적인 CVD 공정은 아래와 같이 이뤄져 있습니다.

- Reactants를 chamber(또는 furnace)에 넣습니다.

- Mass transfer 단계: Reactants가 서서히 이동합니다.

- Wafer 표면에 흡착 (absorption)됩니다.

- Surface reactions 단계: Wafer 표면에서 화학적 반응이 발생하고 본격적인 증착이 이뤄집니다.

- 화학 반응 후 부산물(byproducts)이 탈착되어 밖으로 나갑니다.

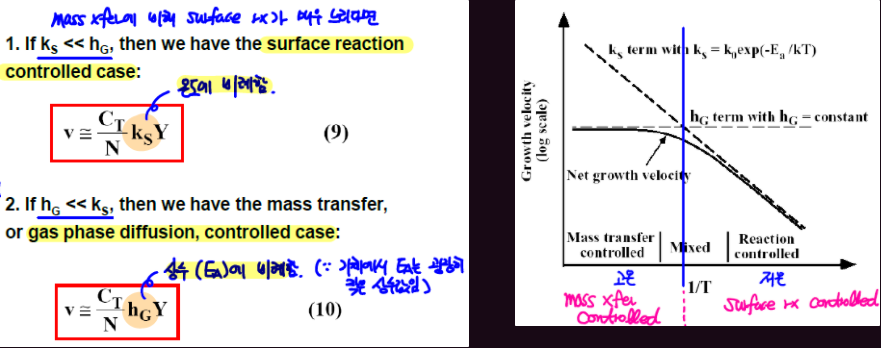

CVD는 serial process이므로 구성 과정들 중 가장 느린 bottle-neck 과정이 저체 공정 시간을 지배합니다. 일반적으로 2번 Mass xfer 단계 또는 Surface reaction 단계가 그 후보들인데 어떤 단계가 더 느리냐에 따라 "Surface reaction Controlled mode" 또는 "Mass transfer Controlled mode"로 나뉩니다. 주로 두 mode를 구분짓는 가장 좋은 factor는 온도입니다.

- Surface reaction Controlled mode:

- 장점: 우수한 step coverage와 geomatric uniformity를 얻을 수 있습니다.

- 단점: 상대적으로 온도가 낮은 환경에서 이뤄지므로 target material의 증착 및 성장 속도가 느립니다.

- Mass transfer Controlled mode:

- 장점: 상대적으로 온도가 높은 환경에서 이뤄지므로 target material의 증착 및 성장 속도가 빠릅니다.

- 단점: Step coverage와 uniformity가 상대적으로 낮습니다.

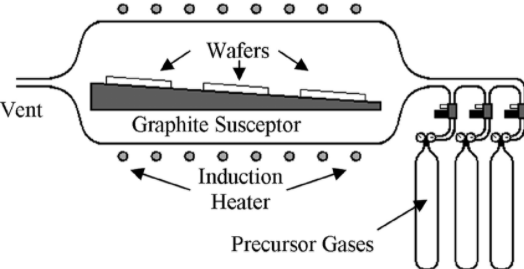

2.3.1. APCVD (Atmosphere CVD)

- APCVD은 두 가지 뚜렷한 특징을 가지고 있습니다.

- wafer가 내열특성을 가진 그래핀으로 구성된 'Susceptor'를 사용합니다.

- CVD 중 거의 유일하게 진공상태가 아닌 공간에서 진행합니다. (SACVD라고 또 있긴 한데 일단 넘어갑시다.)

- Susceptor 판은 살짝 경사져있는데 이 위에 약 10개 정도의 wafer를 놓고 CVD를 수행합니다.

- 대기압과 동일한 chamber에 susceptor와 wafers를 올려두고 예시로 든 target material인 와 산화제인 를 gas 형태로 주입하고 고온을 가하면 반응에 의해 CVD가 이뤄집니다.

- 그러나 susceptor의 크기를 키우는 것에도 한계가 있고 wafer도 끽해야 10여개만 올릴 수 있기 때문에 batch process가 불가능합니다. 따라서 생산 속도가 느리다는 단점이 있습니다.

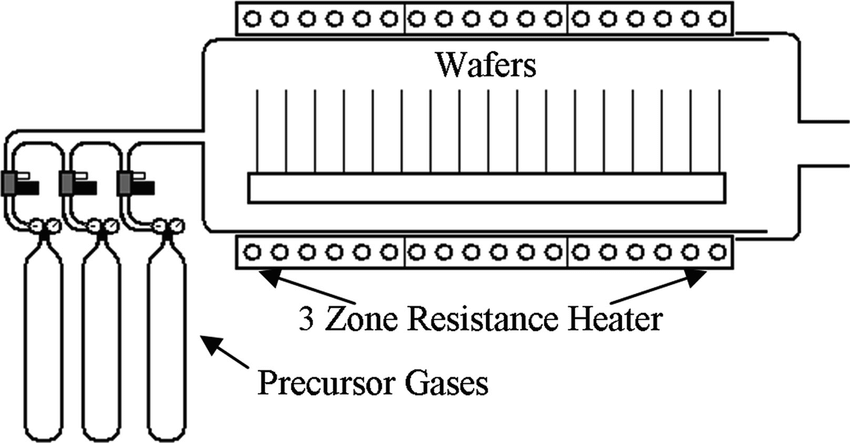

2.3.2. LPCVD (Low pressure CVD)

- 내열 소재의 화로 (Furnace) 안을 진공상태로 만든 뒤 wafer를 일렬로 세로로 세워두고 target gas와 산화제를 넣고 고온을 가해 CVD를 수행하는 방법입니다. (i.e. )

- 세워진 wafer들 중 양쪽 가장자리의 wafer는 'standup wafers' 또는 'dummy wafers'라고 불립니다. 이 wafer들은 안쪽의 wafer들에 균일하게 반응이 일어나서 높은 uniformity를 얻을 수 있게 만들기 위해 희생하는 역할을 합니다.

- 진공 상태에서 진행하므로 targer material 분자가 다른 분자와 충돌하지 않고 자유롭게 이동할 수 있기 때문에 mean free path가 길어져서 높은 step coverage를 얻을 수 있습니다.

- 또한 batch process가 가능해서 대량생산 및 빠른생산이 가능하다는 장점을 가지고 있습니다.

2.3.3. PECVD (Plasma Enhanced CVD)

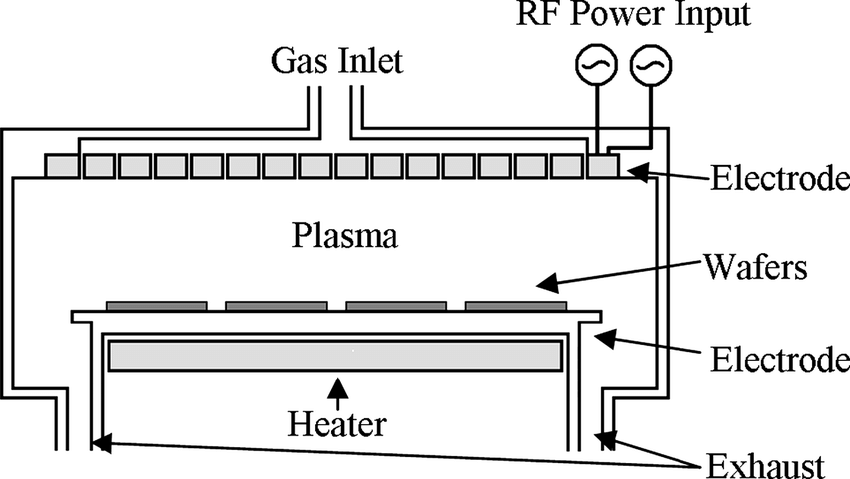

- PECVD는 진공상태의 chamber에 위아래로 높은 교류전압 (주파수: 약 13.56MHz)을 걸어서 플라즈마를 형성한 뒤 반응시켜서 증착시키는 CVD 방법입니다.

- PECVD는 APCVD, LPCVD와는 달리 상대적으로 저온에서 이뤄집니다. 따라서 PECVD는 고온을 사용할 수 없는 back-end 공정에서 주로 사용합니다.

2.3.4. HDPCVD (High-Density Plasma CVD)

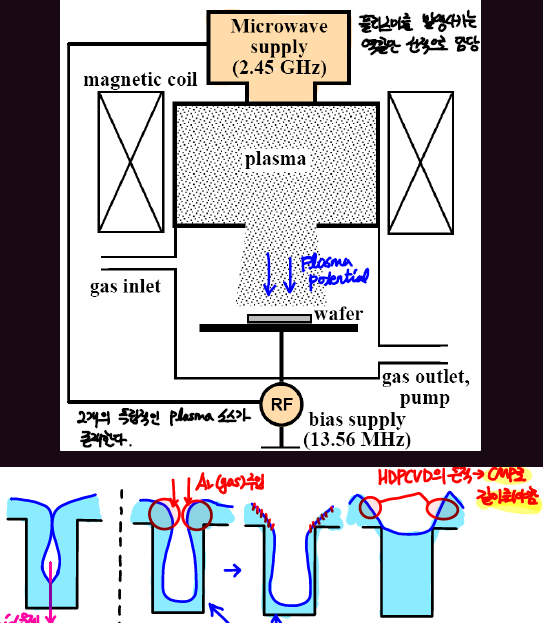

- 공정의 미세화와 더불어 높은 채움성으로도 미세선폭을 제대로 채울 수 없어서 void 등의 현상이 발생하자 기존의 HECVD보다 더 강한 플라즈마를 사용할 수 있는 CVD 방법이 필요해졌습니다.

- HDPCVD는 PECVD와 달리 bias를 걸어주기 위한 RF 전압과 플라즈마를 증폭시키는 역할을 하는 전압 두 개의 power source가 있습니다. 더 고밀도의 강한 플라즈마를 형성할 수 있게 되죠.

- HDPCVD는 void 문제를 해결하기 위해 짧은 시간동안 약간만 증착시킨 뒤 gas를 주입해서 void가 자주 발생하는 코너 부분을 sputtering 또는 미세하게 etching 한 뒤에 다시 증착을 하고 마지막으로 CMP로 매끄럽게 갈아줍니다.

- 흔히 HDPCVD가 채움성이 뛰어나다 또는 gap fill에 용이하다고 표현하지만 엄밀히 말하면 아닙니다.

왜냐하면 gap fill을 용이해진건 HDPCVD 덕분이 아니라 증착과 식각의 반복 덕분이기 때문입니다. 이 반복 공정은 생산속도를 떨어트립니다. 이 문제를 플라즈마의 밀도를 높여서 증착이 더 잘 일어나게 함으로써 해결한 것입니다. - 현재 HDPCVD는 를 back-end 공정에서 증착시킬 때 주로 사용합니다.

2.3.5. MOCVD (Metal-Organic CVD)

- MOCVD는 유기금속화합물 ()을 substrate 위에서 반응시켜서 epitexial을 성장 (Epitexial Growth)시키는 데 주로 사용하는 CVD 방법입니다.

2.4. ALD (Atomic Laver Deposition)

ALD에 대한 보다 상세한 내용은 SK하이닉스 뉴스룸: https://news.skhynix.co.kr/1793 을 참고하시면 더욱 좋습니다.

-

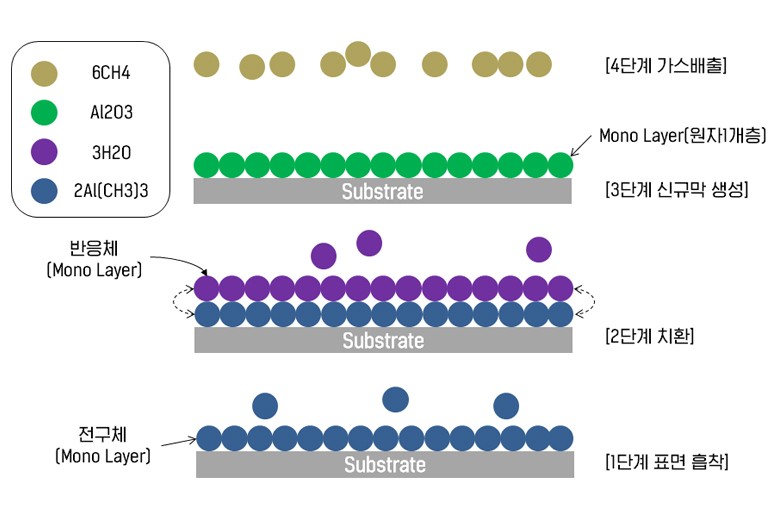

앞서 1절에서 언급했던대로 증착 공정이 마주한 세 가지 문제 중 dimension issue를 해결하기 위해 등장한 ALD는 3D-VNAND 구조의 oxide/metal을 증착하기 위해 사용하고 있습니다. TMI지만 우리나라에서 개발했습니다.

-

ALD의 원리는 비교적 간단합니다. PVD와 CVD는 target material을 증착시키기 위해 reactants gas를 주입 후 반응시켜서 증착시키는 원리였다면, ALD는 target material의 재료가 되는 source들을 한 층 한 층씩 증착 시킨 뒤 반응시켜서 target material을 표면에서 바로 만들어 증착시키는 방법을 사용합니다. 테트리스랑 비슷하네요.

-

ALD는 기존 PVD, CVD가 이뤄내지 못한 높은 접착성과 채움성 그리고 step coverage를 동시에 갖고 있어서 종래의 두 방법이 가진 단점을 거의 극복한 증착 방법이라고 이해하시면 됩니다.

-

물론 ALD는 원자 한 층 한 층 쌓아올리는 방법을 사용하므로 느립니다. 그러나 여기에 플라즈마까지 더한 PEALD를 사용하면 ALD의 낮은 속도를 높히고 굉장히 높은 aspect ratio를 가진 20nm 이하의 공정에서도 ALD보다 낮은 온도에서도 증착이 가능합니다.

- 이번 포스팅에서는 증착 공정이 필요한 이유와 당면한 세 가지 문제점들 그리고 여러 가지 증착 공정 방법에 대해서 알아봤습니다.

- 한 줄로 요약한다면, "공정 미세화가 진행되면서 채움성과 step coverage가 좋은 물질을 plasma를 이용해서 증착하는 방법이 대세가 되고 있다"가 되겠네요.

- 다음 포스팅에서는 이온 주입 공정에 대해서 배우겠습니다.

내용이 방대할 것으로 예상되니 준비 단단히 해두시는게 좋을 것 같습니다. 그럼 다음 포스팅에서 뵙겠습니다!