현대 반도체의 숙적 :: Short Channel Effects

현대 반도체의 발전 과정을 가장 눈에띄게 확인할 수 있는 수치는 바로 '크기(길이)'다. 반도체와 물리에 대해 전혀 모르는 일반 사용자도 '#㎚'라는 숫자는 작아질수록 매력적으로 느껴진다. 집적도가 높아질수록 단위면적당 컴퓨팅 파워는 증가하고 더 고성능의 무언가를 기대할 수 있기 때문이다. 하지만 현대 공정은 이미 오래전부터 소자의 크기를 줄이는 데 한계에 직면해있었다. 그 한계를 천문학적인 돈과 위대한 연구자를 갈아 넣어서 아주 조금씩 넘기고 있는게 현대 반도체 산업의 모습이라 말할 수 있다. 반도체 산업에서 일인분을 할 사람이라면 직군과 직무에 무관하게 '그 한계점'을 명확하게 정의할 수 있어야 한다고 생각한다. 본문에 앞서 이 글의 목적과 범위는 다음과 같다.

- 목적: 현대 반도체 공정이 마주한 Short Channel Effects가 필연적으로 생긴 이유와 그 종류를 이해하고 해결방법에 대해 파악한다.

- 범위: 본 문서의 예상 독자는 1) 컴퓨터공학 전공자, 2) 전자전기공학 저학년, 3) 비전공자 세 부류로 설정한다. 따라서 다루는 내용의 깊이는 얕되 이들이 최대한 잘 이해할 수 있도록 쉽게 설명하는데까지 범위를 설정한다.

- 참고 문서

- 반도체 공부하는 블로그: https://m.blog.naver.com/PostList.nhn?blogId=mirim920

- 물리학도의 세상 살이: https://blog.naver.com/richard2828/220776348036?viewType=pc

- SK hynix Newsroom: https://news.skhynix.co.kr/1805

- 삼성반도체이야기: https://www.samsungsemiconstory.com/

- 잇(IT)러닝: https://it-learning.tistory.com/category/%EB%B0%98%EB%8F%84%EC%B2%B4/%EC%A0%84%EC%9E%90%EC%86%8C%EC%9E%90

좋은 자료를 제공해주신 모든 분께 감사드립니다.

1. MOS Transistor의 구조와 작동원리

-

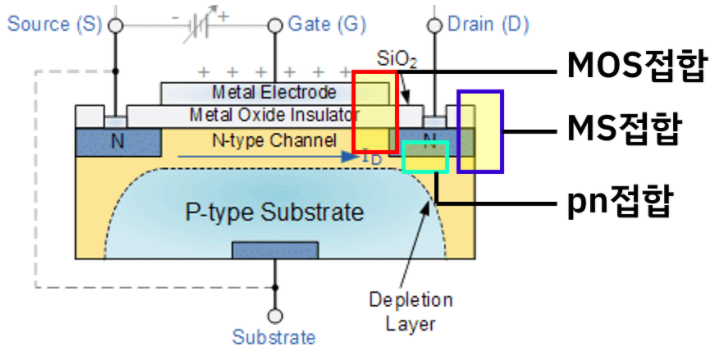

상단의 그림은 기판이 p-type으로 doping된 MOSFET의 구조를 보이고 있다.

-

MOSFET에는 세 가지 접합이 있다.

- MOS접합: Metal - Oxide (절연체) - Silicon의 줄임말로 gate 단자의 접합 형태를 나타낸다.

- MS접합: Metal-Silicon의 줄임말로 source와 drain 단자의 접합 형태를 나타낸다.

- pn접합: Source와 drain은 body(기판)와 다른 type으로 강하게 doping되는데 이 두 부위 사이의 접합을 나타낸다.

-

각 접합은 이형의 물질끼리 친화력이 좋아 서로 잘 달라붙을 수 있고 계면에서 전하결함이 일어나지않으며 전자의 이동을 방해하는 요소 없이 전류가 잘 통하는 상황이 가장 이상적이다.

-

그러나 이상적인 상황은 현실에는 존재하지 않는다. 이유를 설명하자면 다음과 같다.

-

각 물질은 고유한 특징 (물성)으로 전자가 평균적으로 가질 수 있는 에너지를 의미하는 페르미 준위 (Fermi energy, )를 갖는다.

-

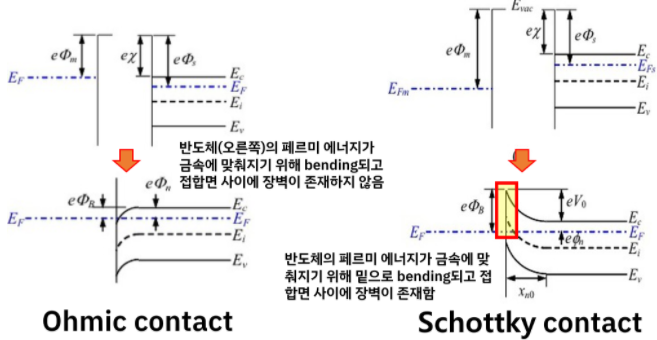

MS접합을 예로 들어보면, 에 차이가 있는 금속(Metal)과 반도체(Semiconductor)가 결합이 되기 위해서는 가 같아져야하기 때문에 어느 한 쪽의 물질 (보통 반도체)에서 alignment를 위해 에너지에 구부러짐 (energy bending)이 발생한다.

-

이때 bending의 형태에 따라 오믹컨택 (Ohmic contact)과 쇼트키컨택 (Schottky contact)로 나뉜다.

-

금속의 가 반도체의 보다 높다면 반도체의 energy band는 위로 휘게 된다. 따라서 두 이형의 물질 사이에 전자의 이동을 방해하는 요소는 존재하지 않으므로 가해주는 전압에 비례해서 전류가 흐르는 옴의 법칙이 성립하게 된다. 이를 오믹컨택 (Ohmic contact)이라 한다.

-

금속의 가 반도체의 보다 낮다면 반도체의 energy band는 아래로 휘게 된다. 따라서 두 이형의 물질 사이에 전자의 이동을 방해하는 에너지 장벽이 생기게 되어 더 이상 옴의 법칙이 성립하지 않게 된다. 이를 쇼트키컨택 (Schottky contact)이라 한다.

Q. 그럼 오믹컨택을 유도하는게 당연히 좋겠네요?

A. 반도체 산업에서 사용할 수 있는 반도체의 종류는 한계가 있고 주어진 반도체에 적합한 에너지 준위를 가지면서 동시에 현대 기술로 식각 (etching)도 가능한 금속물질을 찾기 힘들기 때문에 쇼트키컨택은 불가피하며 우리는 전압-전류의 비선형성을 해결하기 위해 노력해야 합니다.

-

-

MOS 트랜지스터는 각 접합을 대표하는 source - gate - drain 세 부분에 전압을 인가함으로써 동작하게 된다. 구체적인 동작 과정은 다음과 같다.

- 현재 p-type으로 doping된 body와 연결된 gate에 양(+)전압을 인가해주기 시작한다.

- 자석을 떠올리면 (+)극은 (-)극에 끌리게 된다. Body에 미약하게나마 있던 전자들이 gate쪽 (위쪽)으로 끌어당겨지게 되어 쌓인다.

- 계면 쪽 body에 전자가 쌓이며 상대적으로 n-type으로 바뀌게 되며 이 상태를 inversion이라고 부른다. 이 영역이 이미 고농도로 n-type doping된 source와 drain 사이를 연결해주게 된다. 이를 'channel'이라고 부른다.

- Channel이 형성될 때의 gate 전압()을 문턱전압 (Threshold voltage, )이라고 부른다. 이때 drain쪽으로 약간의 전압 ()을 인가해주면 source에 있는 전자들이 drain으로 이동하게 되어 drain에서 source로 향하는 전류가 흐르게 된다.

-

Channel을 통해 흐르는 전류()는 에 비례해서 흐르게 된다.

-

2. Subthreshold Current

- 앞서 우리는 MOSFET의 source와 drain 사이에서 전류가 흐르기 위해서는 문턱전압 이상의 가 필요하다고 배웠다.

- 그러나 사실 문턱전압을 인가하지 않아도 미세한 전류가 흐르는데 이를 subthreshold current (또는 off-current)라고 하며 누설전류의 일종으로 취급한다.

- 우리는 소자를 "ON"하려고 하지 않았어도 의도치않은 전압으로 인해 미세하게 전류가 흐르면서 누설된다. 이것이 우리가 핸드폰을 가만히 놔둬도 시간이 지나면 혼자서 방전이 되는 이유다.

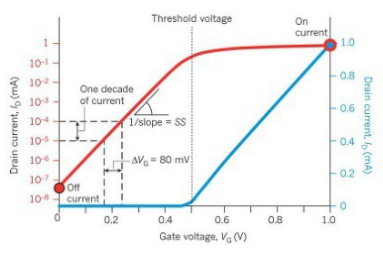

- 인가해주는 gate 전압과 흐르는 전류 사이의 그래프를 로그스케일로 그려보면 기울기(slope)를 얻을 수 있는데 slope의 역수를 swing이라 부르며 SS라고 표현한다.

- Slope가 크다면 인가해주는 전압에 예민하게 반응할 것이다. 문턱전압보다 낮은 전압에서는 subthreshold current가 매우 낮을 것을 기대할 수 있다. 따라서 SS는 낮은 것이 좋다.

3. Short Channel Effects와 원인

3.1. 더 예민해진 Velocity Saturation

- 가 너무 높다면 body에 depletion layer (공핍층, 절연층)가 생성되며 drain 쪽 channel 통로가 좁아지게 된다. 가 성립한다면 통로가 좁아지다 못해 아예 drain 영역에 닿지 않게 된다. 이를 pinch-off 상태라고 부르며 더 이상 전류가 에 비례해서 증가하지 않고 일정하게 유지되고 이를 전류의 saturation 영역이라 부른다.

- 여기까지만 보면 문제점을 알아차리기 힘들지만 pinch-off 상태가 야기하는 문제는 심각하다.

- Pinch-off 상태에서는 에 의해 전기장이 생성되는데 이 전기장이 channel을 이동하는 전자의 이동도 (mobility)에 악영향 (surface scattering, lattice viberation)을 미쳐서 전자의 속도에 한계가 생기게 된다. 이를 velocity saturation이라 부른다.

- 더 큰 문제는 집적도가 높아지면서 channel의 길이가 짧아지다보니 전기장의 세기는 반비례로 강해져서 약간의 전압만 가해도 바로 saturation 영역으로 들어가버린다는 점이다.

- "이게 뭐 대수인가?" 싶겠지만 작은 에도 saturation 영역으로 쉽게 들어가진다는 것은 아주 작은 전압에도 예상치 못한 전류가 흐르게 된다는 것이다. 즉, 소자가 너무 예민해져버린다. 따라서 의도치않은 약간의 전압에도 subthreshold current가 생성되어 누설전류량이 많아진다.

3.2. 어려워지는 alignment와 강해지는 기생저항(Parasitic Resistance)

- 반도체 공정에선 alignment는 그야말로 헌법과 같다. 하나의 IC는 정말 여러 소자 (금속 & 반도체)가 수십 층 씩 쌓아올려지면서 만들어지는데, 그 중 하나의 층이 어긋나기라도 한다면 그 소자는 쓰레기가 돼버린다. 어긋난 층이 다른 곳에 신호를 전달해버리면 예기치 못한 동작을 유발할테니 잠재적 시한폭탄을 어떻게 상품으로 팔겠는가?

- 살리사이드(SALICIDE) 공정을 통해 Gate에 증착되는 금속이 만일 source와 drain 영역에 겹치게 되면 불가피하게 기생저항이 생긴다.

- 이 저항은 우리가 원하는 전류보다 더 작은 전류를 얻게 만들고 주파수 특성에도 악영향을 줘서 RC delay가 증가하는 등 소자의 성능을 떨어트리는 원인이 된다. 특히 기생저항은 channel의 길이가 짧아지면서 전류량을 크게 떨어트릴 정도로 상대적으로 강력해진다.

3.3. 온도에 더 예민해지는 소자

- Channel이 짧아질수록 소자는 고온에 더 취약해진다.

- 동일 전압에 대해 온도가 높아지면 전자의 이동도가 떨어지므로 slope가 낮아진다. 즉, SS성분이 안좋아지므로 미세 전압에도 subthreshold current가 발생할 여지가 높아진다.

3.4. Roll-off

- Roll-off 현상이란, MOSFET의 pn접합의 계면에서 불가피하게 depletion layer가 생성되는데 short channel이 되어 영향력이 커지면서 가 낮아지게 되는 현상을 말한다.

- 가 낮아지는 이유는 다음과 같다.

- 이상의 gate 전압을 인가했을 때 inversion 영역이 생기고 channel이 형성됨을 알고있다.

- pn 접합에 의해 불가피하게 생성되는 depletion layer는 inversion 영역의 재료인데 short channel이 되면서 를 인가하기도 전에 필요한 재료가 점점 상대적으로 많아지는 효과가 생긴다.

- 따라서 같은 inversion 영역을 만들기 위해 들여야 하는 수고 (전압)가 줄어들기 때문에 가 낮아지는 효과가 생기는 것이다.

Q. 가 낮아지면 소자를 구동하기 위한 전력소모가 줄어들게 될테니 좋은 현상이 아닌가요?

A. 네, 일반적으로는 맞습니다. 하지만 그 장점보다 short channel은 근본적으로 subthreshold current와 같은 누설전류를 유발하는 단점이 더 심각하게 다뤄집니다. 그러므로 이 현상을 생기지 않도록 후술할 body effect를 통해 를 높히는 것이 더 낫습니다.

3.5. DIBL (Drain-Induced Barrier Lowering)

- DIBL이란, 에 의한 saturation 영역에서 로 인해 만들어지는 depletion layer가 channel에 까지 영향을 미쳐서 channel 전체의 depletion 영역이 커지게 되는 현상을 말한다.

- Depletion 영역이 커지면 그만큼 inversion이 일어나기 용이해지므로 (+ source와 channel 사이의 전위 장벽이 낮아지므로) 가 낮아지는 효과를 가져온다.

3.6. Punch Through

- 앞서 살펴본 DIBL이 심화되어 (가 더 높아져서) drain의 depletion 영역이 source의 depletion 영역과 거의 맞닿게 되면 전자가 channel을 통해 흐르는 것이 아니라 depletion 영역을 통해 이동할 수 있게되어 누설전류가 발생하게 되는데 이를 punch through 현상이라고 부른다.

3.7. GIDL (Gate-Induced Drain Leakage)

- 앞서 살펴본 DIBL, Punch Through와 비슷하게 GIDL도 에 의해 발생하는 현상이다.

- 만일 gate와 drain이 겹치는 구간이 있고 가 강하게 인가된다면 drain의 depletion 영역이 gate쪽으로 넘어가면서 gate로부터 전자가 tunneling이 되며 drain으로 이동하면서 누설전류가 발생한다.

3.8. Hot Carrier Effect

- Hot Carrier Effect란, 길이에 반비례하다는 특성을 지닌 전기장의 크기가 short channel에 의해 폭발적으로 증가하면서 전자의 속도도 함께 증가해서 결합 구조에 손상을 입히고 source와 drain 영역에 쌓이게 되어 소자 신뢰도에 악영향을 미치는 현상을 말한다.

4. 해결방법

- 앞서 3절에서 우리는 channel의 길이가 짧아지면서 맞이한 8가지 문제점에 대해서 다뤄봤다. Short channel effect의 원인은 결과적으로 2가지로 요약할 수 있다.

- 불가피한 존재들의 상대적 영향력 증가 → Saturation, 기생저항, 온도, 등

- 가 야기하는 문제 → DIBL, Punch Through, GIDL

4.1. Body effect

- Body effect는 를 제어하기 위해 의도적으로 body의 doping 농도를 높게 해주는 방법이다.

- Short channel effect로 인해 낮아지는 와 그로인해 생기는 subthreshold current 문제를 막기 위해 doping 농도를 높혀서 depletion 영역을 만들기 위해 제거해야 하는 carrier의 양을 늘려버려 를 높혀주는 방법이다.

- 하지만 너무 높게 올려버리면 반대로 소자를 "ON"하는 것이 너무 힘들어지고 ON일 때 흐르는 전류도 너무 적어지기 때문에 source와 drain은 고농도로, body는 상대적으로 저농도로 doping하는 방법을 사용한다.

4.2. Halo structure

- 높은 로 인해 제멋대로 확장되는 depletion 영역이 만드는 여러 문제를 막기 위한 방법으로 source와 drain에 울타리 역할을 할 초고농도의 doping 영역을 만들어서 확장을 막는 방법이다.

4.3. LDD structure

- Halo 구조와 유사하지만 완전 반대 방법으로 hot carrier effect를 막기위해 source와 drain 옆에 감속을 위한 저농도의 doping 영역을 만들어서 전자의 속도를 의도적으로 줄이는 방법이다.

4.4. High-K 방법과 HKMG

- roll-off와 DIBL 같은 문제를 해결하기 위해 상단의 body effect를 사용해버리면 결국 가 높아지므로 전력 소모 측면에서의 이득을 포기하게 된다.

- 따라서 누설전류와 낮은 두 마리 토끼를 모두 잡기 위해서는 공식에 따라 산화막 (oxide)의 capacitance를 높혀서 gate의 영향력을 상대적으로 더 증가시키고 channel에 전하가 더 쉽게 모이게 해야 한다.

- Oxide는 절연체이므로 capacitance를 높히기 위해서는 두께를 감소시켜야 한다.

- 하지만 oxide의 두께가 너무 낮아지면 tunneling이 발생해서 전자가 산화막을 뚫고 멋대로 전류가 흘러버리기 때문에 누설 전류가 발생하게 된다. 따라서 우리는 가능한 산화막의 두께는 최소한으로 유지하면서 동시에 capacitance를 증가시켜야 한다.

- Capacitance의 공식을 보면 이므로 유전상수 가 높은 물질을 사용하면 된다는 것을 알 수 있다. 따라서 기존의 oxide로 사용하면 대신에 높은 유전상수를 갖는 , 등을 사용하게 됐다.

- 하지만 를 대체하기 위해 사용했던 산화막들의 문제는 바로 poly-Si와의 상성이었다. Poly-Si와 결합한 산화막은 제멋대로 반응을 일으키며 를 만들어냈고 따라서 캐패시터가 직렬로 연결된 것과 같은 현상 (캐패시터는 직렬로 연결되면 오히려 capacitance가 감소함)이 발생해서 오히려 capacitance가 감소하게 되는, 의도했던 것과 정반대의 결과가 나오게 됐다.

- 결과적으로 poly-Si도 더 이상 사용할 수 없었기 때문에 최근 공정에서는 다시 금속을 사용하게 되는 결론에 도달했다. 따라서 기존의 Metal - Poly-Si - SiO2 - Si 구조는 Metal - High-K - 아주얇은 SiO2 - Si로 바뀌게 됐으며 이를 HKMG (High-K Metal Gate)라고 부른다.

- HKMG로 인해 누설전류를 감소시킬 수 있으면서 capacitance는 증가했기 때문에 소자의 특성을 개선할 수 있다. 하지만 gate로 금속을 사용하면서 기존에 금속→Poly-Si로 바꿨던 원인들 중 하나였던 제어가 다시 복잡해졌다는 단점이 있다.

4.5. 3가지 구조 :: FDSOI, FinFET, GAA

4.5.1. FDSOI (Fully Depleted Sillicon On Insulator)

- HKMG로도 누설전류를 완전히 막을 수는 없었기 때문에 "하...그럼 아예 누설될 공간 자체를 없애버리자"라는 아이디어에서 FDSOI 구조가 나오게 됐다.

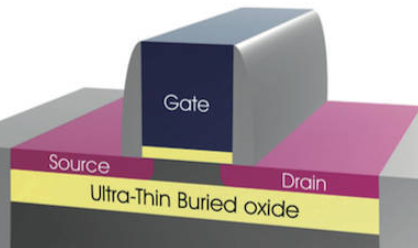

- 상단의 그림을 보면 body가 극단적으로 짧고 얇아져서 channel의 길이만큼만 있고 원래 body가 있던 곳에는 같은 절연체를 둬서 전류가 누설될 공간 자체를 허용하지 않는다.

- 그러나 공정 과정이 복잡하고 돈이 많이 들기 때문에 후술할 FinFET, GAA에 밀려서 단일로는 잘 사용하지 않는 방법이고 FinFET과 GAA에 응용되서 사용된다.

4.5.2. FinFET

- 누설전류는 결국 우리가 인가하는 의 영향력을 높혀서 최대한 예상 가능한 범위 내에서 전류를 제어하는 방법으로 막을 수 있다.

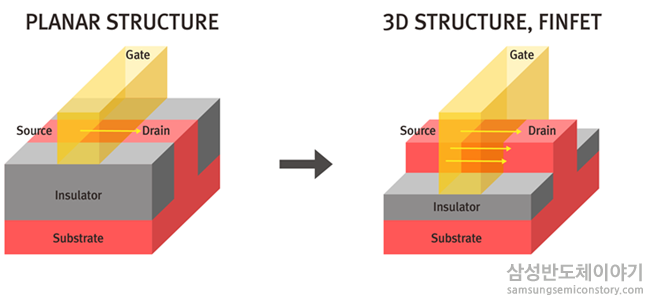

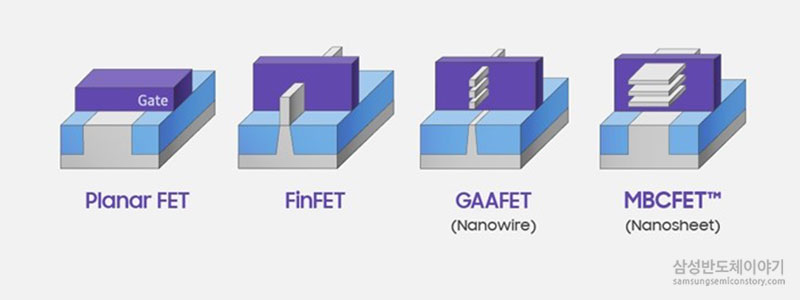

- Gate의 영향력을 높혀서 subthreshold current와 같은 누설전류를 최대한 막기 위해서는 gate와 channel 사이의 접점이 커져야하고 기존의 한 면만 만났던 MOSFET 구조에서 3면이 만나는 FinFET 3D 구조를 적용하게 됐다.

- 삼성은 16년 말에 이미 FinFET 공정을 업계 최초로 14nm 이하에 적용 및 양산했다.

4.5.3. GAA (Gate-All-Around)

- 5nm 이하의 미세 공정이 등장하며 3개 면으로도 gate의 영향력이 만족스럽지 않아 면을 하나 더 추가해 4개 면에서 channel을 둘러싸는 이 구조가 GAA이다.

- 최근에 3nm 공정에서 GAA공정을 사용한 삼성과 TSMC가 치열한 경쟁을 하고있는데 최근 21년 1월 1일 디지타임스의 보고서에 따르면 TSMC와 삼성 모두 3nm에 도달하는 데 문제가 있어 두 파운드리 모두 당초 예정에 비해 다소 뒤처지게 되는 것으로 알려졌다.

5. 정리

- 우리는 본 문서를 통해 MOSFET의 접합구조와 동작원리에 대해 다뤘고 집적도가 높아지면서 마주한 8가지 문제점과 5가지 해결법에 대해서 배웠다.

- 각 문제점과 해결법은 물리반도체적으로 훨씬 더 깊고 자세하게 팔 수 있지만 나를 포함한 예상독자들에겐 현상과 원인 그리고 해결방법을 명확하게만 알고 있어도 충분하다고 생각한다.

- Short channel effect로 인해 파생되는 문제점을 한 문장으로 요약하면 "누설전류가 발생하며 문턱전압 제어가 힘들어진다."다.

- Short channel effect 문제점을 해결하기 위한 방법을 한 문장으로 요약하면 "SS 성분을 좋게 만들기 위해 를 의도적으로 높히거나 Q=CV에 따라 capacitance를 증가시키기 위해 노력한다" 이다.

Velocity Saturation이 Pinch off 랑 상관이 있나요?