앞으로 해당 블로그에서 Verilog환경은 크게 2가지를 사용할 것입니다.

- Vscode - editor용도

- Modelsim - Compile & Testbench Simulation용도

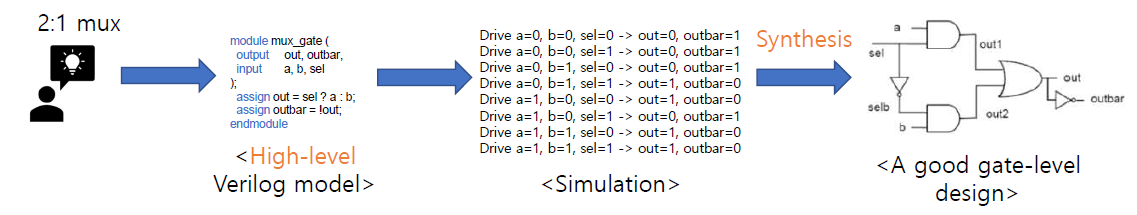

Verilog로 우리가 할 수 있는 일은 다음과 같습니다.

1) 설계하려고 하는 HW의 spec을 결정하고 이를 Verilog로 기술(묘사)한다.

2) Verilog로 기술한 module이 제대로 동작하는지 확인하기 위해서 Simulation을 진행한다.

3) 해당 module을 합성해서 cell-level netlist로 뽑아낸다.

본인이 작성한 Verilog코드가 합성(Synthesis)되었을 때 정상적으로 동작하는지를 검증(Verification)하기 위해서 Testbench Simulation을 진행한다고 하였는데 이를 위해서 작성자는 Intel의 Modelsim이라는 IDE(통합개발환경)을 이용할 것입니다.

낯설 수 있는데 C언어 배우실 때 많이들 사용하시는 Visual Studio 같은거라 생각하시면됩니다.

하지만 해당 IDE의 무료버전은 Simulation까지만 할 수 있습니다. 즉 Synthesis과정이 불가능합니다. 만약 본인이 조금 더 자세히 공부하고 싶다면 라이센스를 가지고 있는 대학교 랩실의 학부연구생으로 들어가거나, 아니면 FPGA용도로 synthesis를 진행해볼 수 있는 Xilinx사의 Vivado를 이용해보길 바랍니다.

(Vivado도 무료로 다운받을 수 있습니다, 설치법은 구글링)

Xilinx 사이트 : https://www.xilinx.com/

Modelsim

그럼 Modelsim을 다운로드 받는 법을 설명하도록 하겠습니다. 저는 다운로드를 꽤 예전에 하였기 때문에 최근 다운로드 하는 방법이 바뀌어서 '공대생 놀이터'님의 영상을 참고하였습니다. 해당 영상 : https://www.youtube.com/watch?v=_EDExFfHmqE

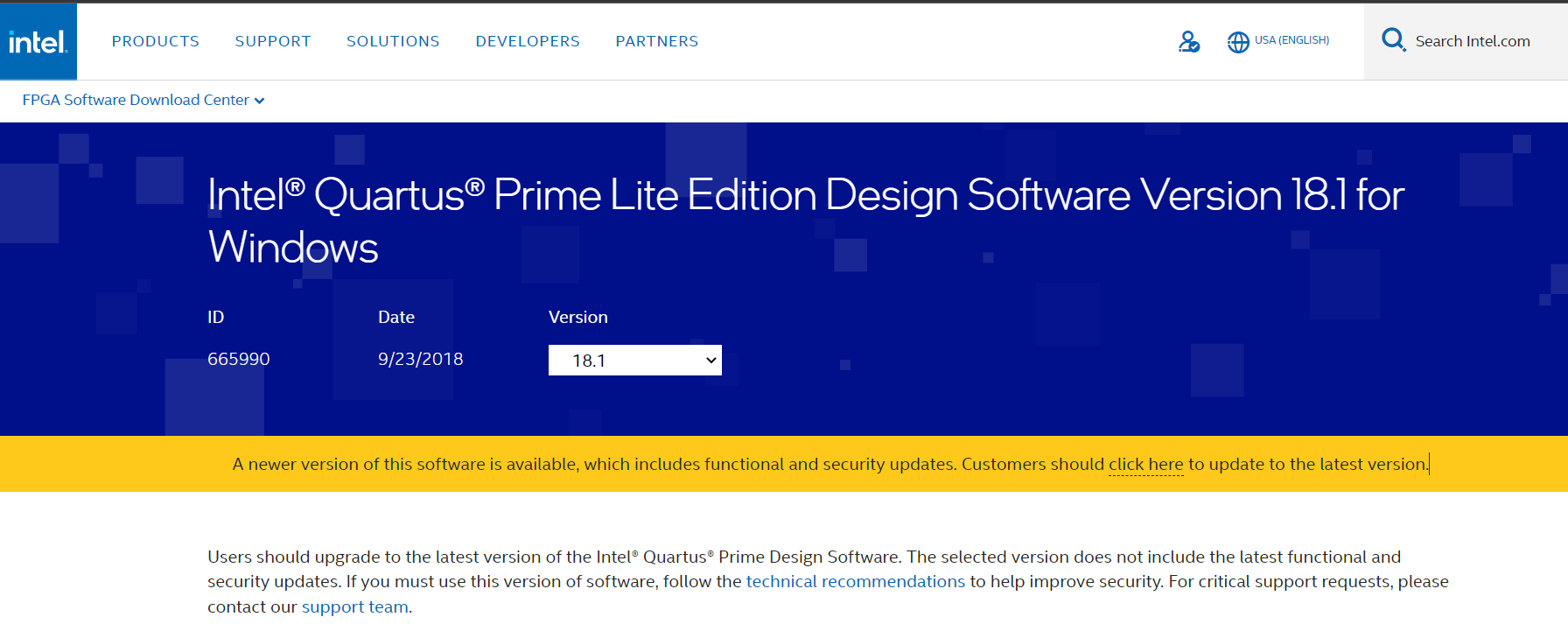

Intel FPGA download center : https://www.intel.com/content/www/us/en/software-kit/665990/intel-quartus-prime-lite-edition-design-software-version-18-1-for-windows.html

먼저 위의 링크를 통해서 intel download center에 접속해줍니다.

다음으로 아래로 내리면 download라는 구간이 있는데 여기서 multiple download가 아니라 individual files로 가서 위의 includes starter edition을 다운로드 해줍니다. 여기서 size가 1.1GB인지 확인해주세요. 이후에는 다른 프로그램 다운로드 받으시는 것처럼 진행해주시면 됩니다.

이제 modelsim으로 Verilog코드를 compile, simulation할 수 있습니다. 파일검색기에 modelsim을 치시면 나올 겁니다(버전은 다르겠죠?).

그런데 modelsim의 editor는 시각적으로 보기가 불편합니다(물론 그냥 써도 상관없습니다). 따라서 에디터 용도로 vscode를 다운로드 받아줍시다. vscode 사이트 : https://code.visualstudio.com/

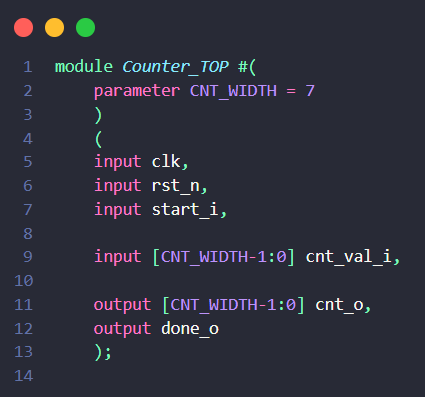

다음으로 Verilog코드의 식별자(identifier, C언어로 치면 int, for와 같이 특정 기능이 있는 용어들)을 highlight(색깔 바뀌는거)해주기 위해서 extension을 다운로드 해줄겁니다. extension은 다른 개발자들이 vscode에서 추가적인 기능들을 만들어 놓은 open source라고 생각하시면 됩니다.

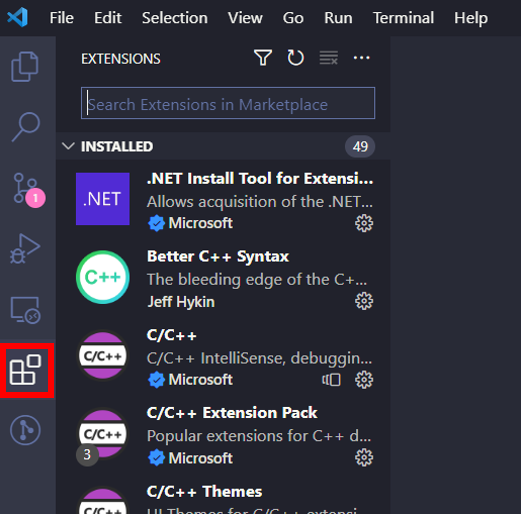

위의 그림처럼 vscode창에서 왼쪽에 사각형 몇 개가 있는(붉은색) extension을 눌러줍니다. 그리고 검색창에 Verilog를 검색해주세요.

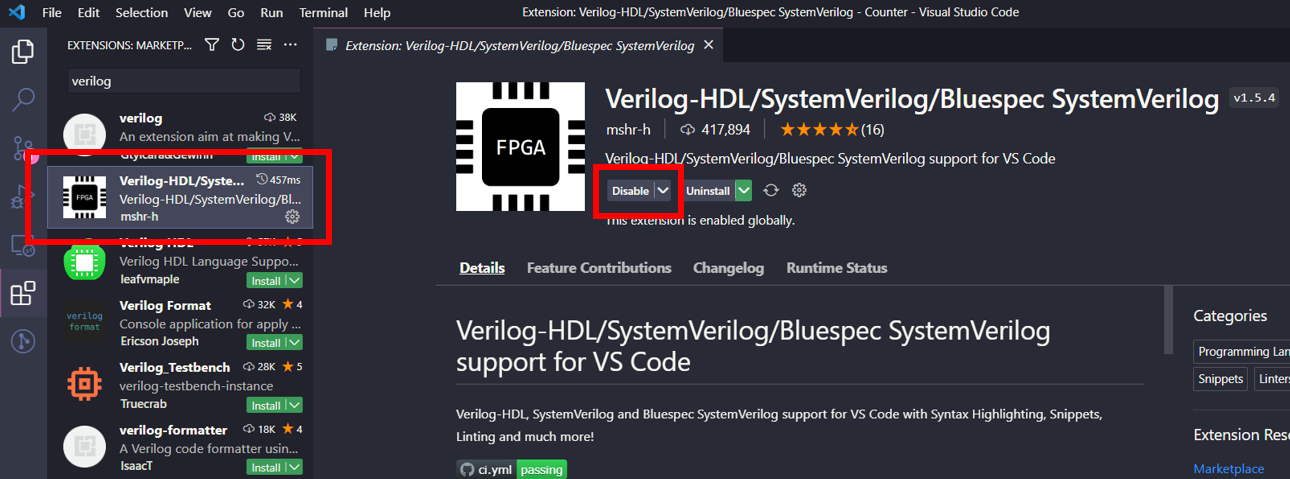

그럼 다음과 같이 verilog와 관련된 extension들이 뜨는데 Verilog-HDL/SystemVerilog/...을 install해주면 됩니다(여러분은 disable부분에 install이라고 되어있을 겁니다).

이렇게 modelsim과 vscode 셋팅이 끝났으면 이제 Verilog를 공부할 준비가 끝난겁니다. 다음 글에서 Synthesis 및 수업 계획에 대해 말씀드린 이후부터 문법에 대해 다루도록 하겠습니다.

REF.

-

Verilog modeling for synthesis of ASIC designs for native speakers of VHDL

(ELEC 4200, By Victor P. Nelson) -

Digital System Design Introduction to Verilog

(By Jungrae Kim of Semiconductor Systems Engineering in Sungkyunkwan University)