Rule

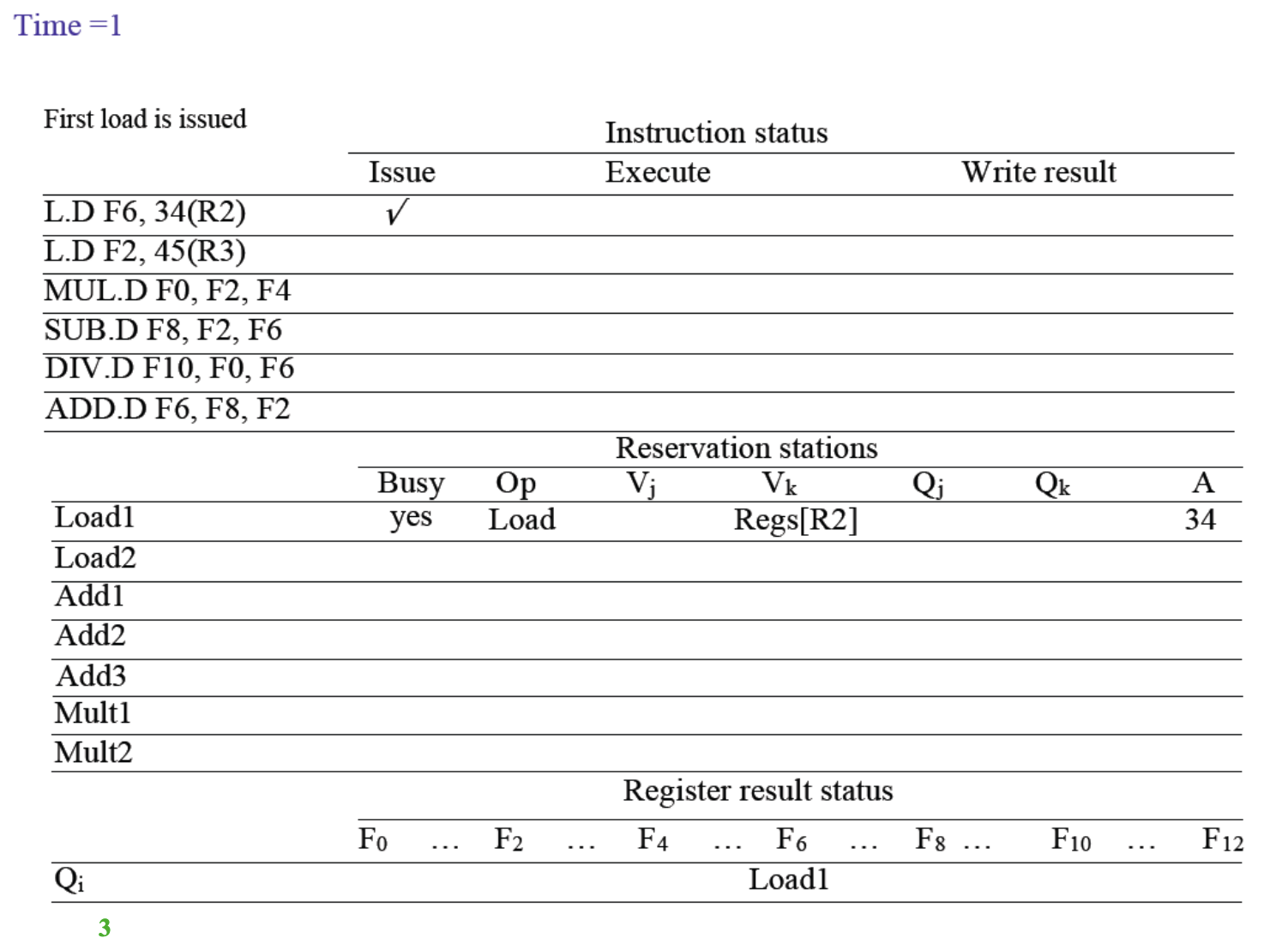

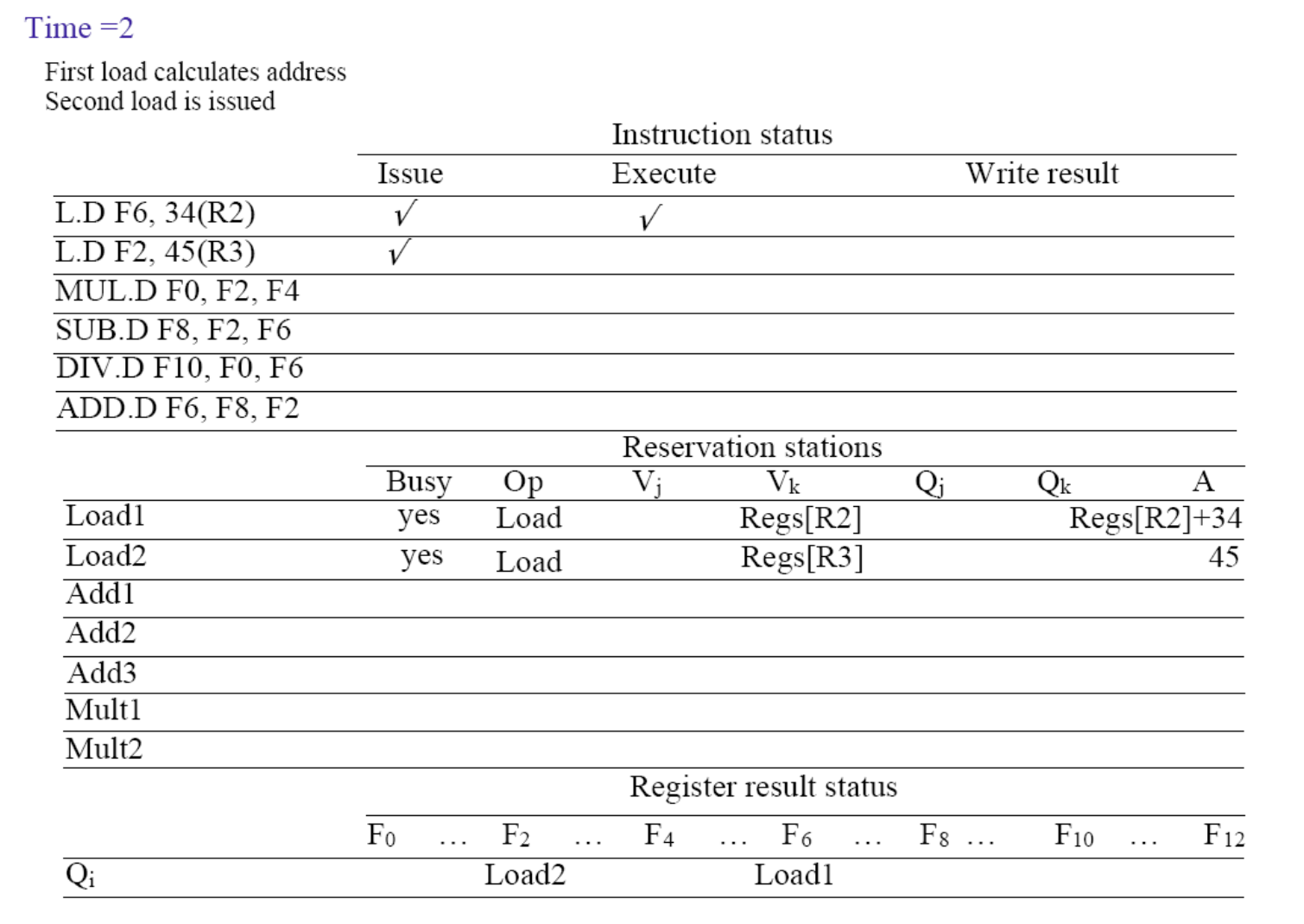

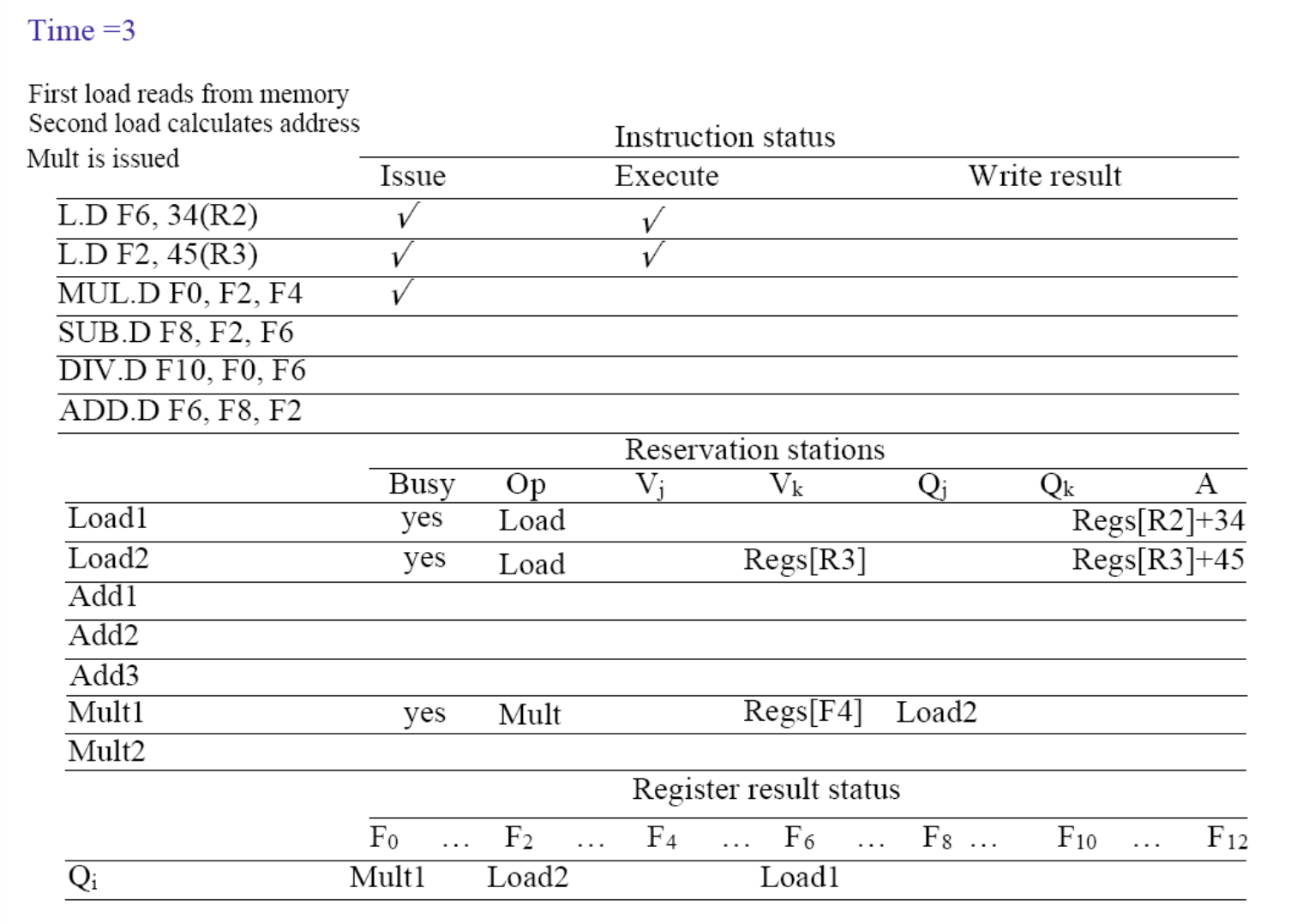

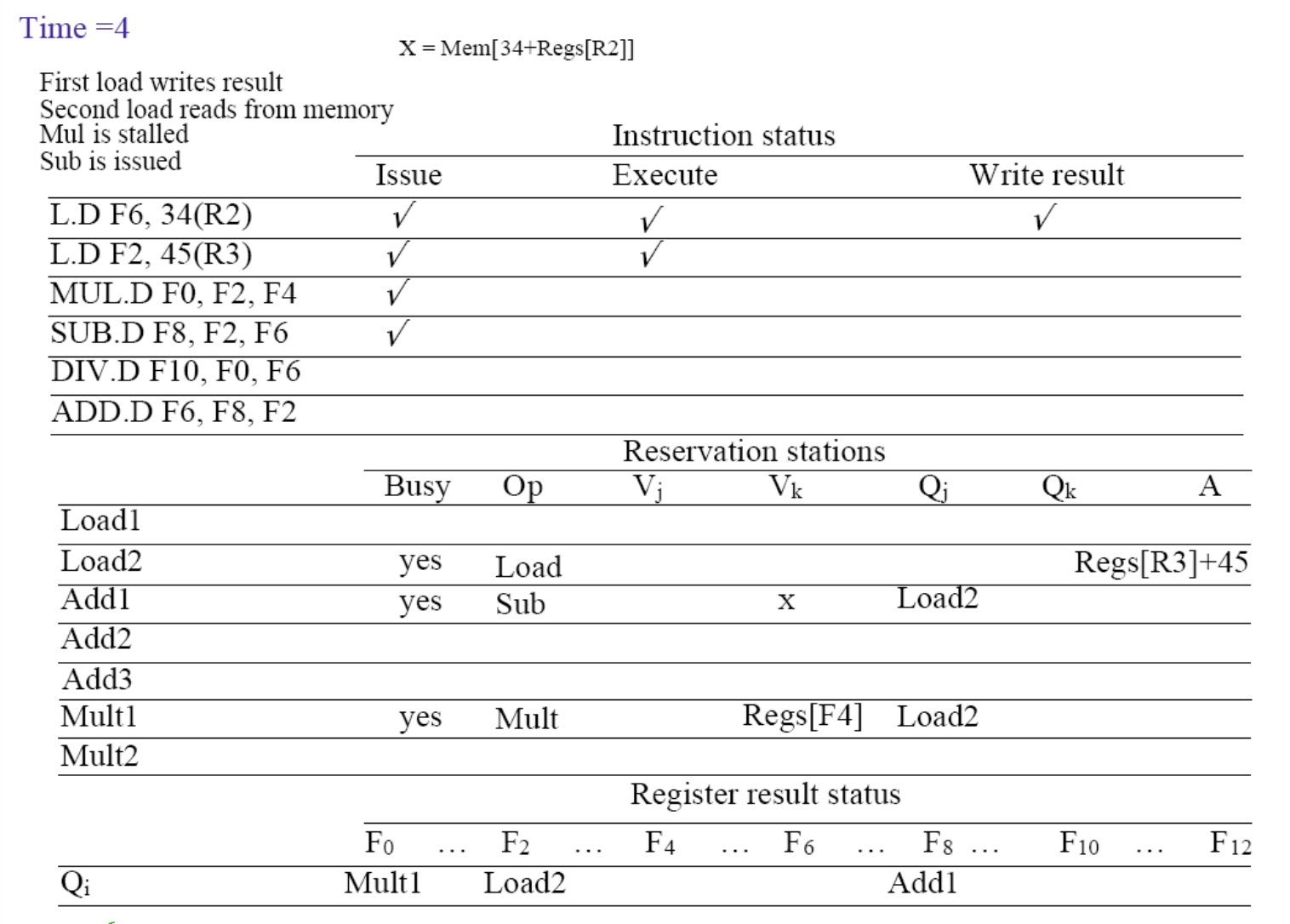

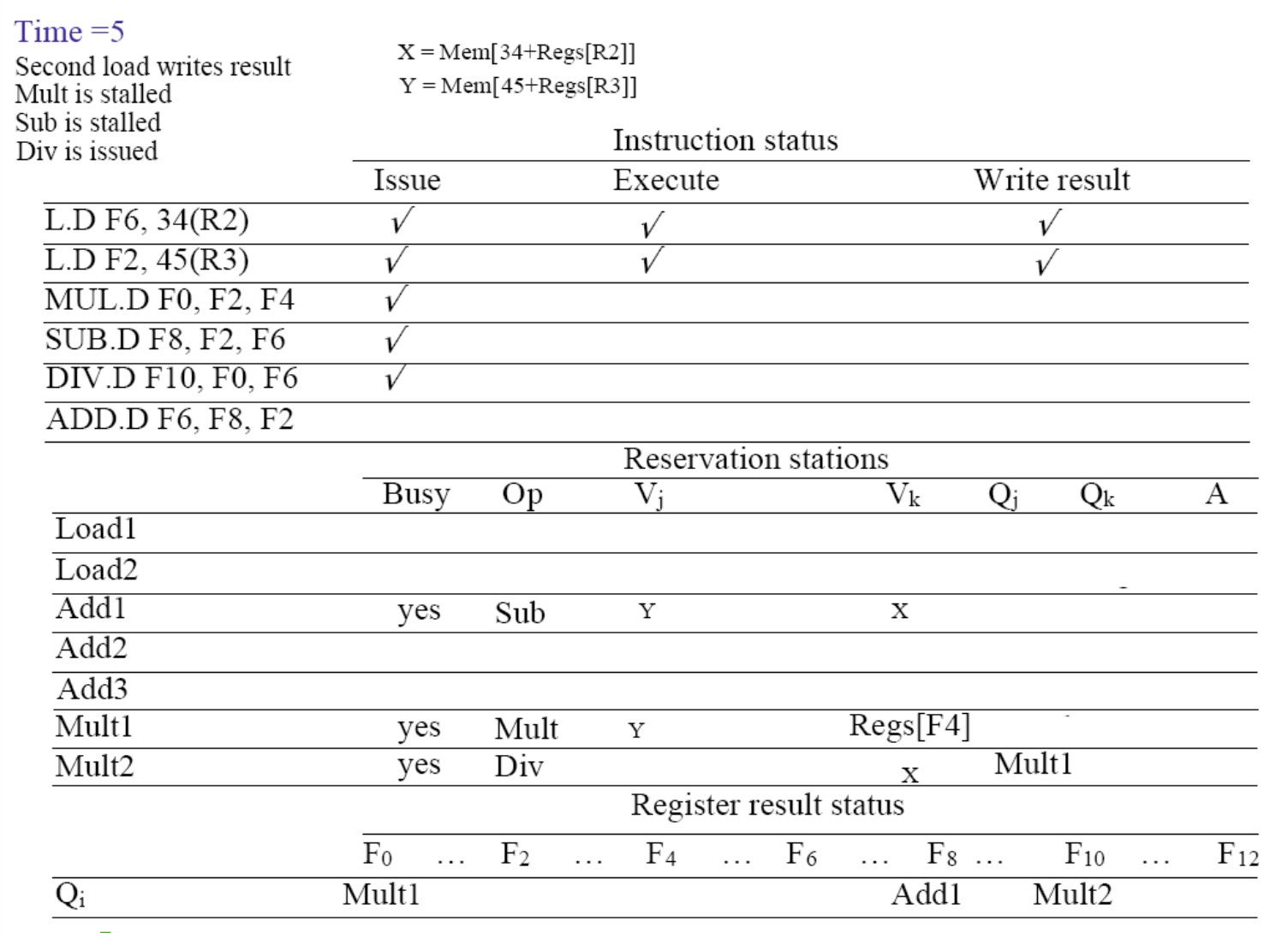

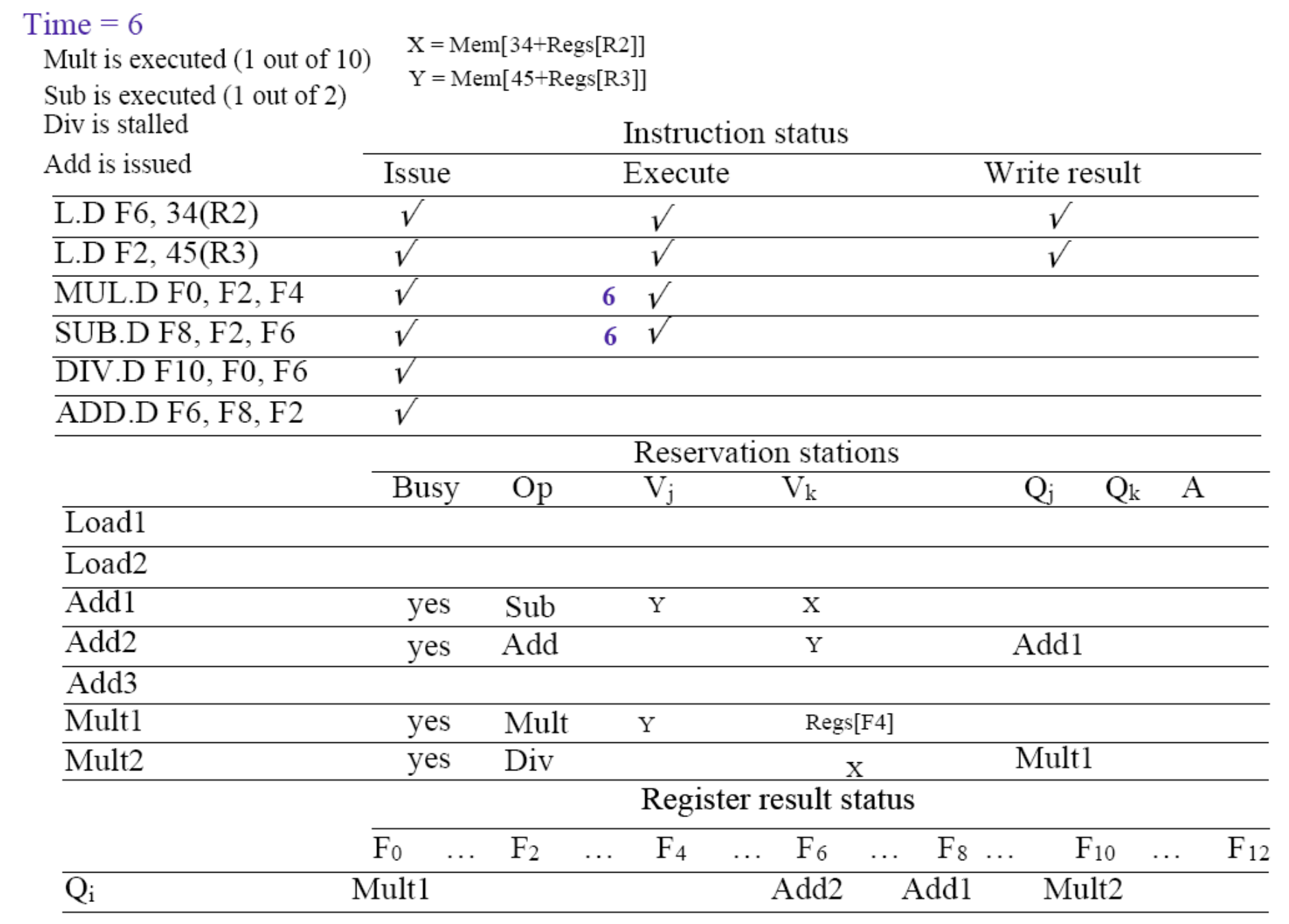

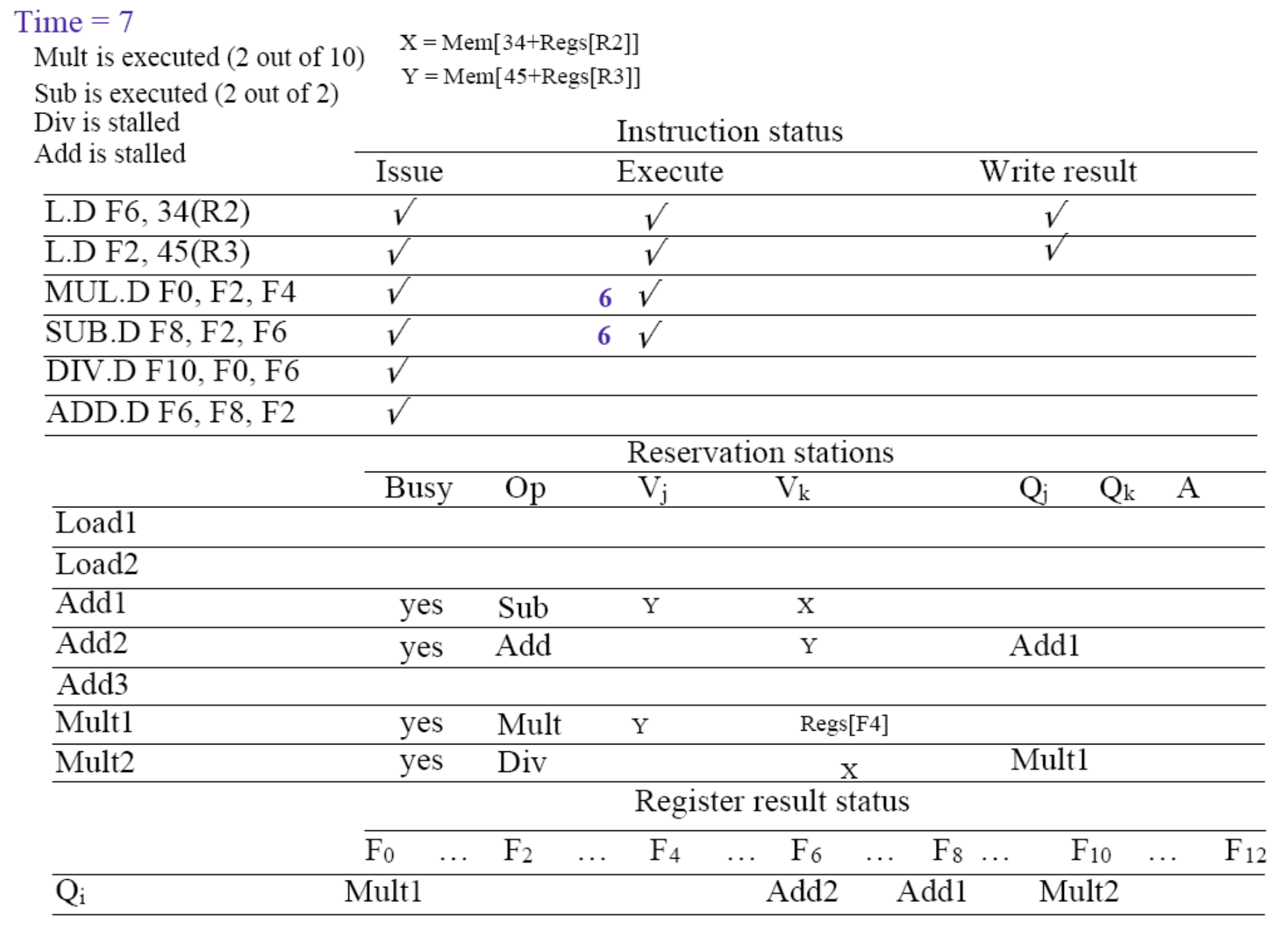

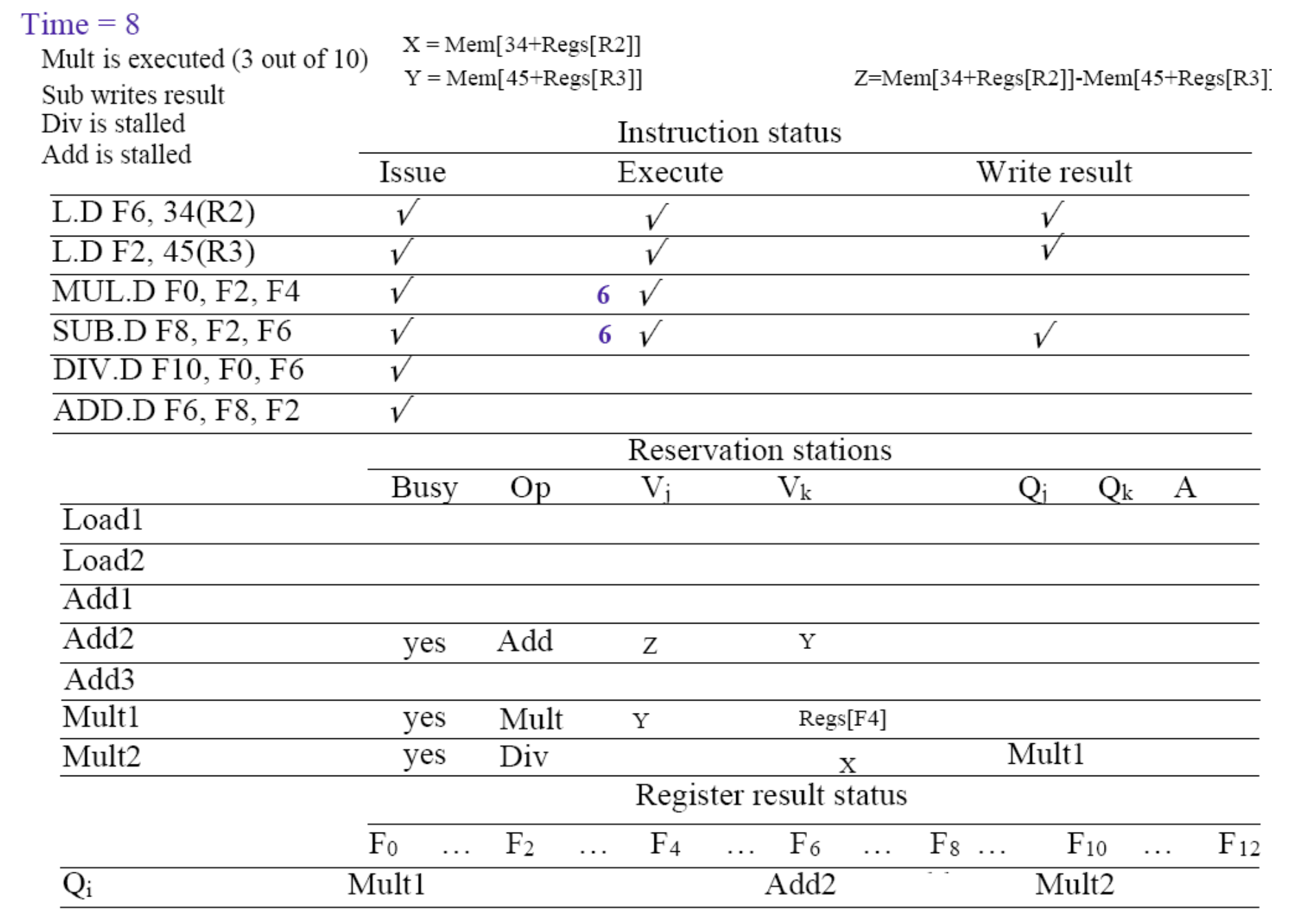

- issue 조건: reservation station이 비어있으면 됨

- Load has 2 step: it takes 2 cycle

- Qj, Qk 둘다 비고, Vj, Vk가 다 차야 Execute 가능

- Mul = 10 cycles

Add, Sub = 2 cycles

Div = 40 cycles

issue 조건: reservation station이 비어있으면 됨

reservation station: load2 비어있어서 time 2에 LD issue 가능

reservation station: Mult1 비어있어서 time 3에 Mul issue 가능

Load has 2 step: it takes 2 cycle 그래서 Excute 2사이클 이후에 Write 할 수 있다.

so begining of cycle 3 no data

mul (Qj) is not empty, can not execute

Qj, Qk 둘다 비고, Vj, Vk가 다 차야 Execute 가능

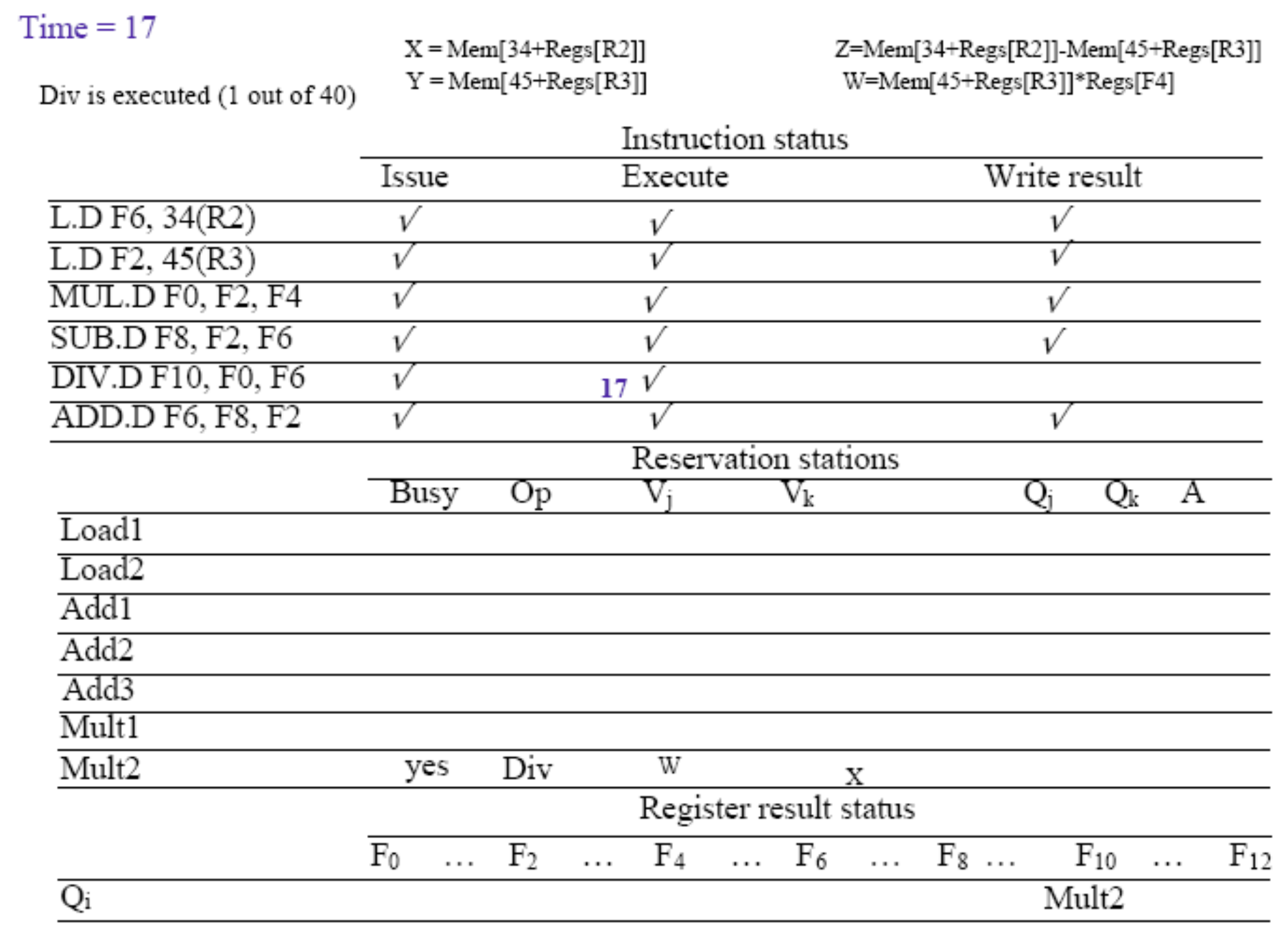

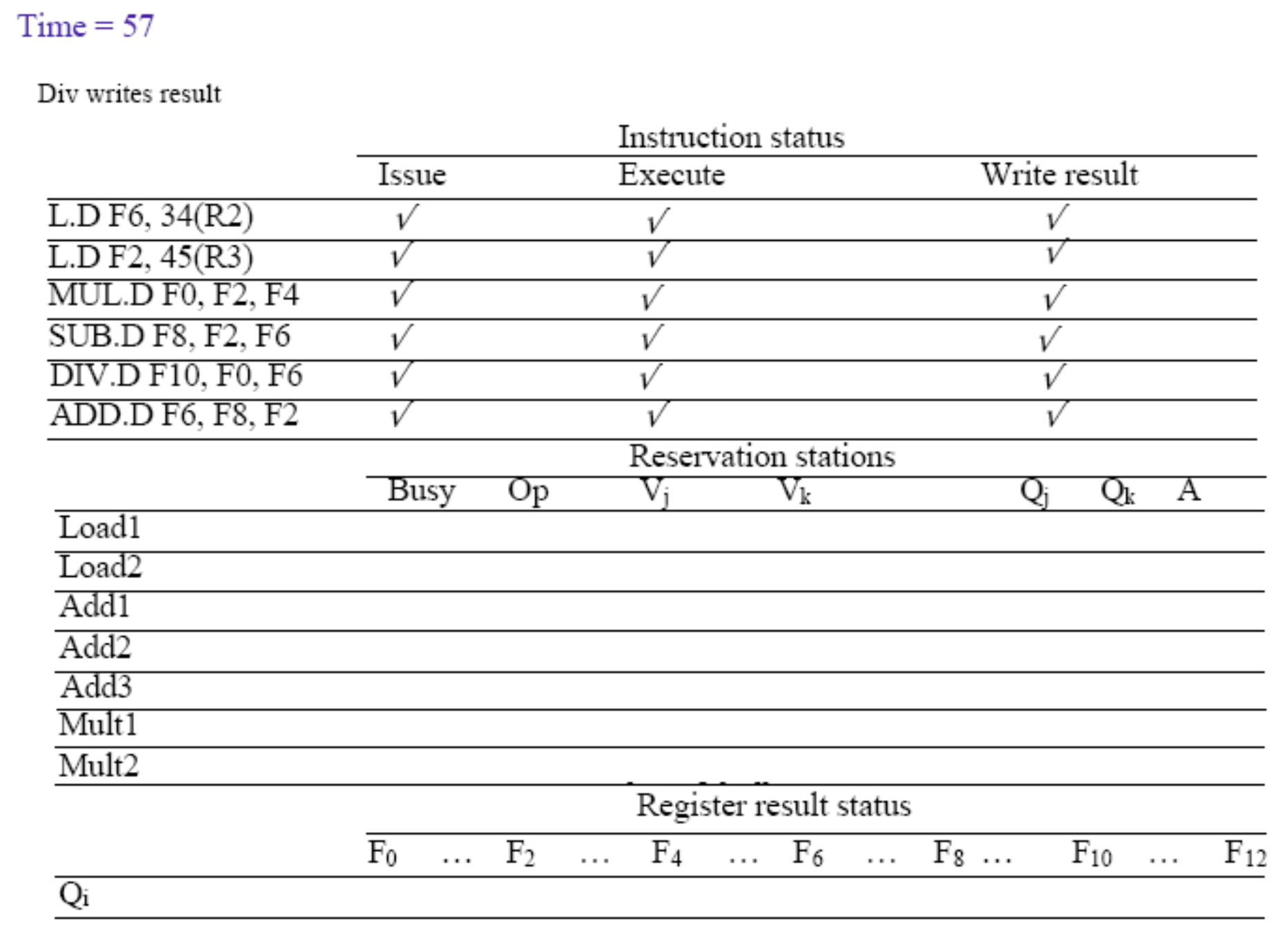

Mul = 10 cycles

Add, Sub = 2 cycles

Div = 40 cycles

Elimination of WAR Hazards

WAR 해결: 앞사람이 Issue 단계에서 재료(Value or Tag)를 자기 RS로 미리 피신시키기 때문에, 뒷사람이 레지스터를 덮어써도 안전하다.

1. L.D F6, 0(R2) // F6에 값 쓰기

2. DIV.D F2, F4, F6 // F6의 값 읽기 (DIVD)

3. ADD.D F6, F8, F10 // F6에 새 값 덮어쓰기 (ADDD)2번(DIVD)이 F6을 읽어야 하는데, 3번(ADDD)이 눈치 없이 F6에 새로운 값을 덮어쓰려고 하는 상황이 바로 전형적인 WAR (Anti-dependence) 해저드입니다.

DIVD 명령어가 Issue 단계에서 Reservation Station(RS)에 들어가는 순간, 더 이상 뒤따라오는 ADDD 명령어의 영향을 받지 않고 완전히 독립된다는 뜻입니다.

해석: DIVD가 RS에 들어갈 때(Issue), 만약 1번 L.D가 이미 계산을 끝냈다면, 물리적인 레지스터 F6를 쳐다보는 게 아니라 그 실제 값(Value) 자체를 자기 RS의 Vk 칸에 복사해서 챙겨버립니다. 3. "If the LD had not yet completed, the 2nd operand would then refer to its R.S., but still not to F6!"

해석: 만약 1번 L.D가 아직 계산 중이라면, 물리적 레지스터 F6을 기다리는 게 아니라 L.D가 들어있는 RS 이름표(Tag, 예: Load1)를 자기 RS의 Qk 칸에 적어두고 기다립니다. (즉, 어느 경우든 물리적 레지스터 공간인 F6에 의존하지 않게 됩니다.)

Elimination of WAW Hazards

WAW 해결 : 뒷사람이 Issue 단계에서 레지스터 장부(Qi)의 이름표를 새치기해버리고 overwrite한다.

tomasulo algorithm은 기본적으로 renaming 기법인데

이미 F0를 Mult로 renaming했는데 아래 다른 명령어에 또 F0가 나올때 어떻게 대처해야할지를 설명한다.

MUL F0, F2, F4 => mult1, load2, Regs[F4]

SUB.D F0, F2, F6 => add1, load2, Regs[F6]

if

SUB.D F0, F2, F0 => add1, load2, mult1

//source register는 이전 renaming인 Mult1으로 한다결론: 목적지 레지스터는 Overwrite 새로운 걸로 덮어쓰고, source register는 이전 renaming을 사용한다.

renaming:

- Mul F0 -> Mult1 become Sub F0-> add1

- SUB.D F0, F2, F0 => add1, load2, mult1

- source F0는 mult1 그대로 유지

Tomasulo's algorithm: renaimg every destination register

Vx(if (RegisterStat [x]. Qi=r) {Regs[x] + result;

그래서 위에 코드에 if 가 있는 것 이다.