클럭 (Clock)

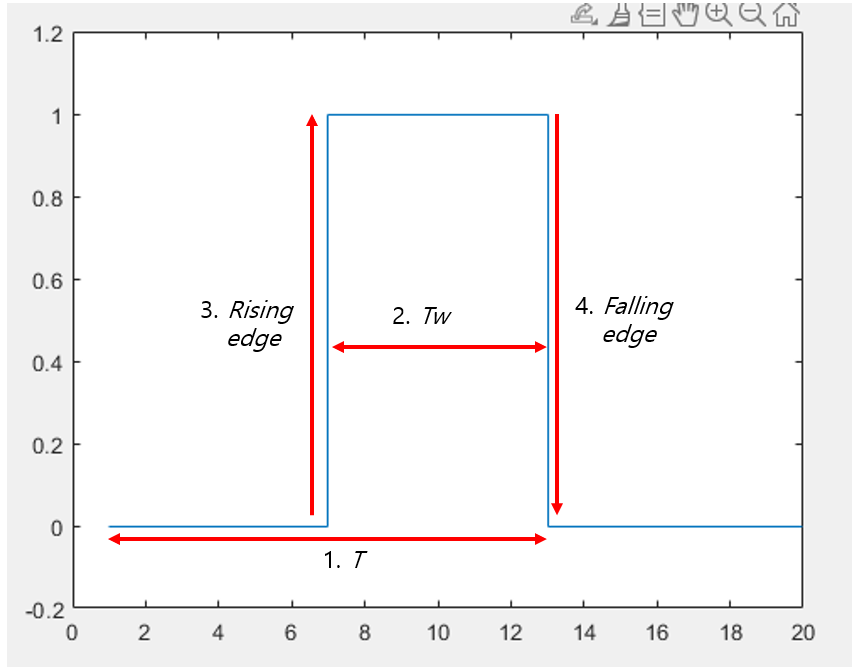

동작 타이밍을 맞추기 위해 사용하는 주기적인 신호 (펄스)

클럭 신호의 형태 :

- 클럭은 보통 직사각형 파형(펄스파)의 형태를 가지며, High(1)와 Low(0)의 상태를 일정 간격으로 반복

모든 연산과 데이터 이동은 클럭 신호에 맞춰 수행됨.

"틱(tick)" 또는 "클럭 싸이클" 이라고도 함

클럭의 동작 방식

-

동기식 시스템 (Synchronous)

모든 동작이 클럭의 상승엣지나 하강엣지에 동기화되어 발생합니다.

예: CPU, 메모리, 레지스터 등의 작동 -

비동기식 시스템 (Asynchronous)

클럭 없이 동작하며, 신호의 변화에 따라 동작함

반응은 빠르지만 설계 복잡도가 높음

클럭과 논리 회로

-

플립플롭 (Flip-Flop)

클럭을 이용해 입력 값을 저장하는 기본 소자

클럭의 엣지에서만 데이터가 바뀜 → 기억 기능 -

레지스터

여러 개의 플립플롭으로 구성된 저장 장치

클럭이 들어와야 값이 저장됨 -

클럭 도메인

복잡한 시스템에서는 서로 다른 주파수를 가진 클럭 영역이 있을 수 있음

→ 이를 클럭 도메인(clock domain) 이라 함

도메인 간 데이터 전달 시 메타스테이블 문제 발생 가능

→ 해결 위해 동기화 회로 필요

클럭 관련 회로 설계 개념

| 개념 | 설명 |

|---|---|

| 클럭 분할기 | 고속 클럭을 더 느린 클럭으로 나눔 |

| PLL (Phase Locked Loop) | 외부 클럭 신호를 기준으로 내부 클럭 생성 |

| 클럭 게이팅 | 사용하지 않을 때 클럭 차단 (전력 절감) |

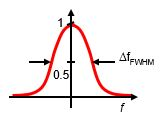

반치전폭 (FWHM - Full Width at Half Maximum)

- 주파수 응답 등의 스펙트럼 상에서 첨두값(Peak)의 1/2 이 되는 위치에서의 스펙트럼 폭

이는 해상도/분해능, 스펙트럼선폭 등을 나타낼 때 많이 쓰임

클럭 노이즈

클럭 지터 (Clock Jitter)

지터는 클럭 신호의 이상적인 타이밍에서 얼마나 흔들리거나 변동되는지를 나타내는 값

-

클럭의 싸이클이 원래 10ns 간격 기준

어떤 싸이클은 9.8ns, 어떤 싸이클은 10.2ns가 되는 식의 시간 불안정성 -

원인

전원 노이즈

전자기 간섭(EMI)

발진기 성능 불안정

온도, 전압 변화 등

주기 지터 (Cycle-to-Cycle) : 두 인접 클럭 간격의 변화

누적 지터 (Accumulated Jitter) : 클럭이 계속 쌓이면서 누적되는 오차

클럭 드리프트 (Clock Drift)

드리프트는 오랜 시간에 걸쳐 클럭 주기가 점점 느려지거나 빨라지는 현상

지터가 미세한 흔들림이라면, 드리프트는 클럭 속도가 점점 변하는 경향성

-

원인

온도 변화

크리스탈 발진기의 물리적 특성

Aging (부품 노화) -

예시

시스템 A와 시스템 B가 각각 1초에 1,000,000 클럭이라고 하더라도

A는 1초에 1,000,050 클럭,

B는 1초에 999,950 클럭을 생성할 수도 있음

→ 장시간 동기화를 유지하기 어려움 (네트워크, 통신 등에서 중요)

클럭 트리 (Clock Tree)

클럭 트리는 하나의 클럭 소스에서 시작해 시스템 전체에 클럭을 분배하기 위한 트리 형태의 회로 구조

시스템의 모든 회로가 동시에 동작하기 위해선 정확한 타이밍 분배가 필요

클럭 신호가 멀리 퍼질수록 전파 지연(delay)이 발생

트리 구조를 통해 균일한 분배와 지터 최소화를 구현

| 구성요소 | 설명 |

|---|---|

| 클럭 소스 (PLL 등) | 주 클럭 생성기 |

| 버퍼 | 신호 강도 증가 및 지연 조절 |

| 분기 회로 | 클럭을 여러 노드로 나누는 구조 |

| 인버터/게이팅 | 필요에 따라 방향 제어 및 전력 최적화 |

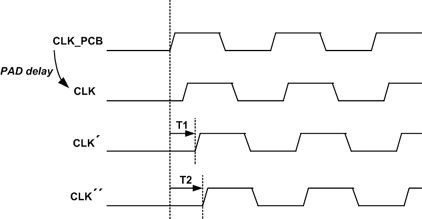

Clock Skew (클럭 스큐)

같은 클럭 트리에서 파생된 클럭이 각 회로에 서로 다른 시간에 도착하는 현상

스큐가 심하면 setup/hold 위반 발생 가능

- 해결 방법:

트리 밸런싱

동일한 길이의 경로

Delay buffer 사용

| 개념 | 설명 |

|---|---|

| 지터 | 싸이클 간 미세한 시간 불안정성 |

| 드리프트 | 장기적으로 누적되는 속도 변화 |

| 클럭 트리 | 클럭을 균일하게 분배하기 위한 회로 구조 |

| 스큐 | 클럭 도달 시간 차이 (문제의 원인) |

클럭 타이밍 요소

| 용어 | 정의 | 회로적 의미 | 영향 |

|---|---|---|---|

| 클럭 스큐 (Clock Skew) | 같은 클럭이 여러 플립플롭에 도달하는 시간차 | 타이밍 마진 감소 또는 데이터 오류 | |

| 슬랙 (Slack) | 제한 시간 대비 실제 경로 지연 여유 | 음수일 경우 타이밍 위반 | |

| 슬루율 (Slew Rate) | 신호가 상승/하강하는 속도 | 너무 느리면 지연 증가, 너무 빠르면 신호 노이즈 | |

| 셋업 타임 (Setup Time) | 클럭 엣지 전에 데이터가 안정되어야 하는 시간 | 플립플롭 요구 조건 | 부족하면 데이터 오류 발생 |

| 홀드 타임 (Hold Time) | 클럭 엣지 후에도 데이터가 유지되어야 하는 시간 | 플립플롭 요구 조건 | 부족하면 잘못된 데이터 수용 |

| 클럭 지터 (Jitter) | 클럭 엣지의 시간적 불확실성 | 전원 노이즈, 온도, 공정 변동 원인 | 타이밍 신뢰도 저하 |

| 경로 지연 (Path Delay) | 신호가 한 플립플롭에서 다음으로 이동하는 데 걸리는 시간 | 조합 논리 지연 + 배선 지연 | 클럭 주기 설정에 직접 영향 |

| 최소/최대 지연 (Min/Max Delay) | 경로상의 가능한 최단/최장 지연 시간 | Min: 홀드 체크 / Max: 셋업 체크 | 타이밍 여유 확보 필요 |

| 트랜지션 타임 (Transition Time) | 신호가 10% → 90% 또는 그 반대로 변화하는 데 걸리는 시간 | Slew와 유사 | 타이밍/파워/EMI에 영향 |

클럭 생성기 (Generator)

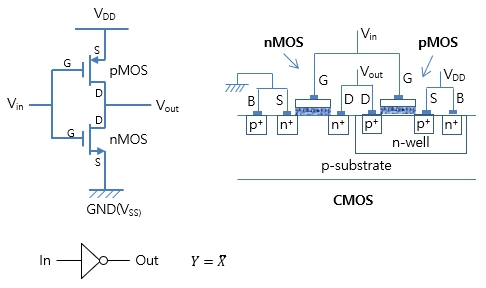

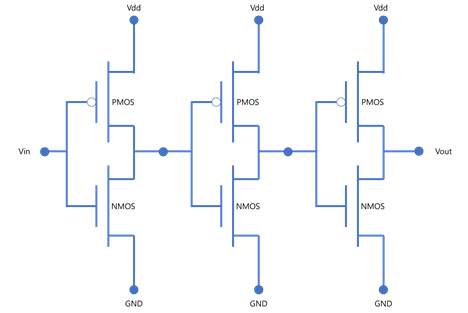

CMOS 인버터

(Complementary MOS)

- 하나만 켜짐. VDD-GND Path 항상 끊어져 Static power 낮아짐

- noise margin 큼. 항상 VDD-GND 연결 -> 0 or 1

- operating 속도 빠름

CMOS 인버터 회로

-

NMOS

Pull down network, Gate +전압 인가시 ON

NMOS: 하부에 위치, 게이트가 ‘1’이면 도통

Low level : 그대로

High level : VDD-VTH -

PMOS

Pull up network, Gate -전압 인가시 ON

PMOS: 상부에 위치, 게이트가 ‘0’이면 도통

Low level : VTH

High level : 그대로

입력(Vin) : 두 트랜지스터의 게이트에 동시에 연결

출력(Vout) : 두 트랜지스터의 드레인을 연결한 지점에서 출력

동작 원리

| 입력 | PMOS 상태 | NMOS 상태 | 출력 |

|---|---|---|---|

| 0 (Low) | ON (도통) | OFF | VDD (High) |

| 1 (High) | OFF | ON (도통) | GND (Low) |

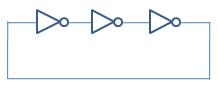

링 오실레이터(Ring Oscillator)

- 홀수 개의 인버터(Inverter)를 고리처럼 연결해 만든 디지털 오실레이터 회로.

외부의 클럭 없이도 자체적으로 발진(oscillation)하는 특성으로 주파수 생성 등에 사용

구성 요소

- 홀수 개의 인버터 (개, 5개, 7개…)

※ 짝수개 인버터면 각 노드 반전되지 않고 고정됨

폐루프 연결: 마지막 인버터의 출력이 다시 첫 번째 인버터의 입력으로 연결

동작 원리

- 인버터 1에 신호가 들어가면 0 → 1 → 0…으로 계속 반전

각 인버터는 약간의 전파 지연(delay time)을 갖고 있어, 전체 루프에서 반전 신호가 왕복하면서 주기적인 파형을 생성

결과적으로 출력은 사각파(Square Wave) 형태

진동 주기 및 주파수

-

진동 주기 T = 2N×Td

N : 인버터 개수

Td : 지연시간

주파수 f = 1 / 2NTd -

클럭 주파수 변경

- 인버터 개수 조절

- 커패시터 삽입 (충방전 시간)

- 공급전압 변경

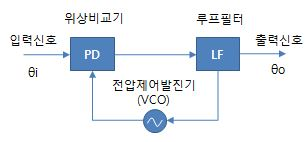

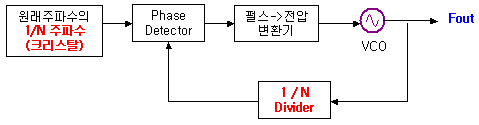

PLL

PLL (Phase-Locked Loop, 위상 고정 루프) 는 입력 신호와 위상 또는 주파수가 같은 신호를 생성하는 회로

입력 신호에 동기화된 출력 주파수를 얻기 위해 위상 비교 → 보정 → 피드백 과정을 반복

http://www.rfdh.com/bas_rf/begin/pll.php3

| 블록 | 기능 |

|---|---|

| 위상 비교기 (Phase Detector, PD) | 입력 신호와 피드백 신호의 위상 차이 검출 |

| 루프 필터 (Loop Filter) | PD의 출력(에러 전압)을 평균화해 DC 제어 전압 생성 |

| VCO (Voltage Controlled Oscillator) | 입력 전압에 따라 주파수가 변하는 발진기 |

| 분주기 (Divider, ÷N) | 출력 신호를 N으로 나누어 PD에 다시 전달 |

동작 원리

- 입력 신호 Vin과 출력의 피드백 신호 간 위상 차이 → PD에서 감지

위상차를 에러 전압 Ve로 변환 → 루프 필터를 통해 안정된 제어 전압 생성

제어 전압이 VCO의 주파수를 조정

출력이 입력 신호와 동일한 위상/주파수를 가질 때까지 반복 → "Locked" 상태

출력 주파수 fout = N×fin

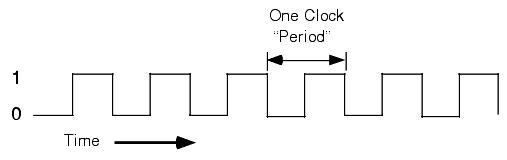

PWM

-

PWM 이란 Pulse Width Modulation 의 약자

정보에 따라 펄스의 폭을 변화시켜 전달하는 방식.

일정한 주기 내에서 Duty비를 변화 시켜서 평균 전압을 제어하는 방법 -

신호의 크기가 크면 펄스 폭을 크게 하고 신호의 크기가 작으면 펄스 폭을 작게 하여 정보를 전달.

펄스 폭의 크기에 따라 평균 전력 변화

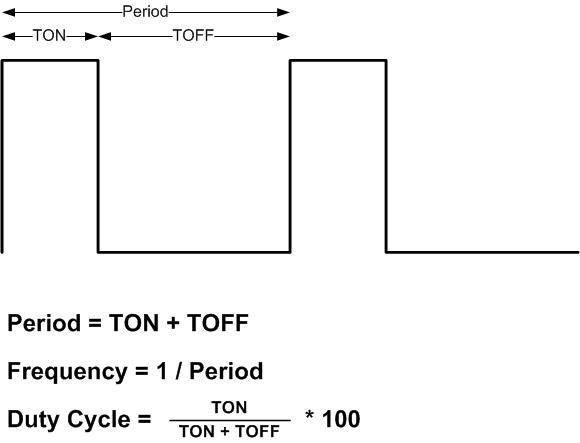

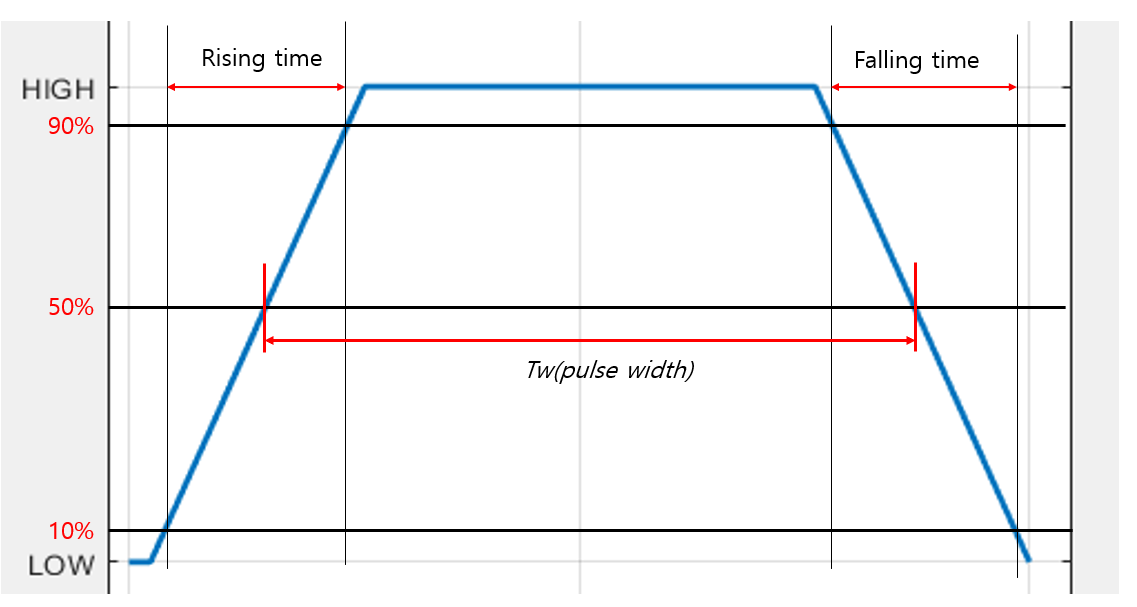

PWM Parameter

- 일정한 주기에서, 출력이 필요로 하는 만큼의 전력을 스위치 ON하여 입력으로부터 공급.

필요한 출력전력에 따라 ON / OFF의 비율, 듀티 사이클 (duty cycle) 변화

-

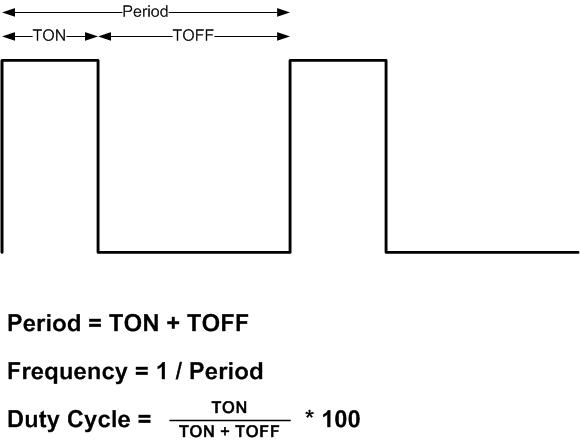

T (주기) : 1번 진동한 시간(같은 모양이 다시 나타날 때까지의 시간) 주파수(f)와는 역수 관계

-

Ton, Tw (펄스폭) : 펄스의 x축 폭(width)이다 (PWM 제어에서 펄스폭 제어하는 방식이다)

-

Rising edge (상승 에지) : 0에서 1로 변할 때를 의미합니다

-

falling edge (하강 에지) : 1에서 0으로 변할 때를 의미합니다

Rising time(상승 시간) : LOW에서 HIGH로가는 시간.

10% 지점에서 90% 지점의 시간을 나타냄

Falling time(하강 시간) : HIGH에서 LOW로 가는 시간.

90% 지점에서 10% 지점의 시간을 나타냄

- 주파수 (Frequency) : PWM 신호가 반복되는 속도 (예: 10kHz)

듀티 사이클 (Duty Cycle) : High 시간 비율 (예: 30%, 70% 등)

주기 (Period) : 하나의 PWM 사이클 전체 시간 (주파수의 역수)

Rise/Fall Edge : 신호가 LOW→HIGH 또는 HIGH→LOW로 바뀌는 순간

트리거

-

트리거 또는 트리거 신호 (Trigger)

상태 변화를 촉발하는 기동 신호

트리거링 (Triggering) : 상태에 변화를 주는 것 -

트리거링 기법 구분

레벨 트리거링 (Level Triggering), 레벨 감응 (Level-sensitive)

High(1) 또는 Low(0) 구간에서만 입력 데이터를 받아들임

신호가 특정 수준(레벨)에 도달했을 때만 동작이 수행됨 (래치 등) -

에지 트리거링 (Edge Triggering), 에지 감응 (Edge-sensitive)

클럭 천이 순간에 만 입력 데이터를 받아들임

신호가 변하는 순간에만 민감하게 반응 -

종류)

Positive Edge Triggered,

Negative Edge Triggered,

Dual Edge Triggered, 대부분의 플립플롭 등

숏 펄스 트리거링 (Short pulse Triggering) :

매우 짧은 클럭 펄스에 만 입력 데이터를 받아들임

요약 정리

| 항목 | 설명 |

|---|---|

| 클럭 | 회로 동작을 동기화하는 신호 |

| 주기 (T) | 한 싸이클이 걸리는 시간 |

| 주파수 (f) | 1초 동안 반복되는 클럭의 횟수 (f = 1/T) |

| 상승엣지 | 0에서 1로 전환되는 순간 |

| 하강엣지 | 1에서 0으로 전환되는 순간 |

| 클럭 도메인 | 다른 주파수 영역의 클럭 구간 |

| 성능 영향 | 클럭이 빠를수록 일반적으로 더 많은 연산 가능 |

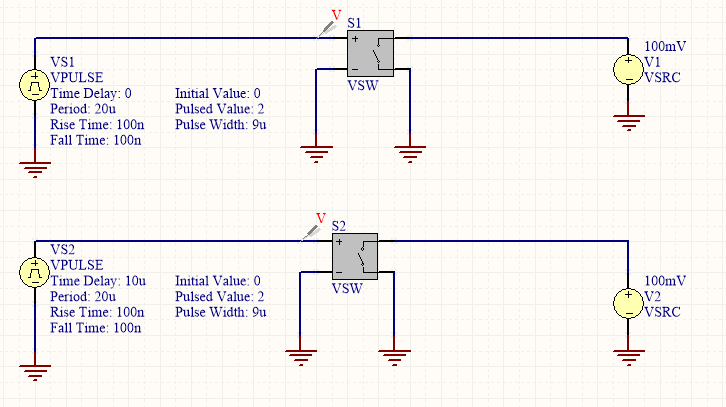

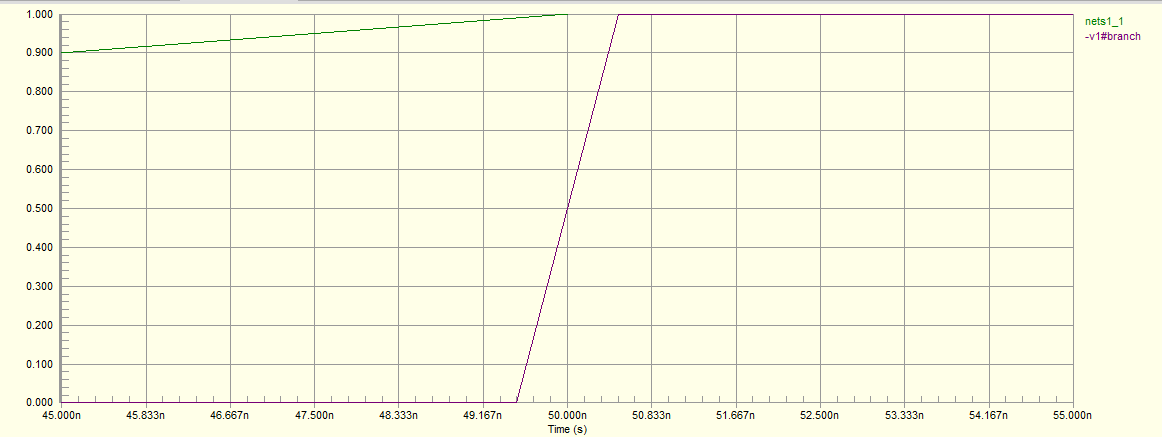

PWM 스위칭 주기 측정

회로

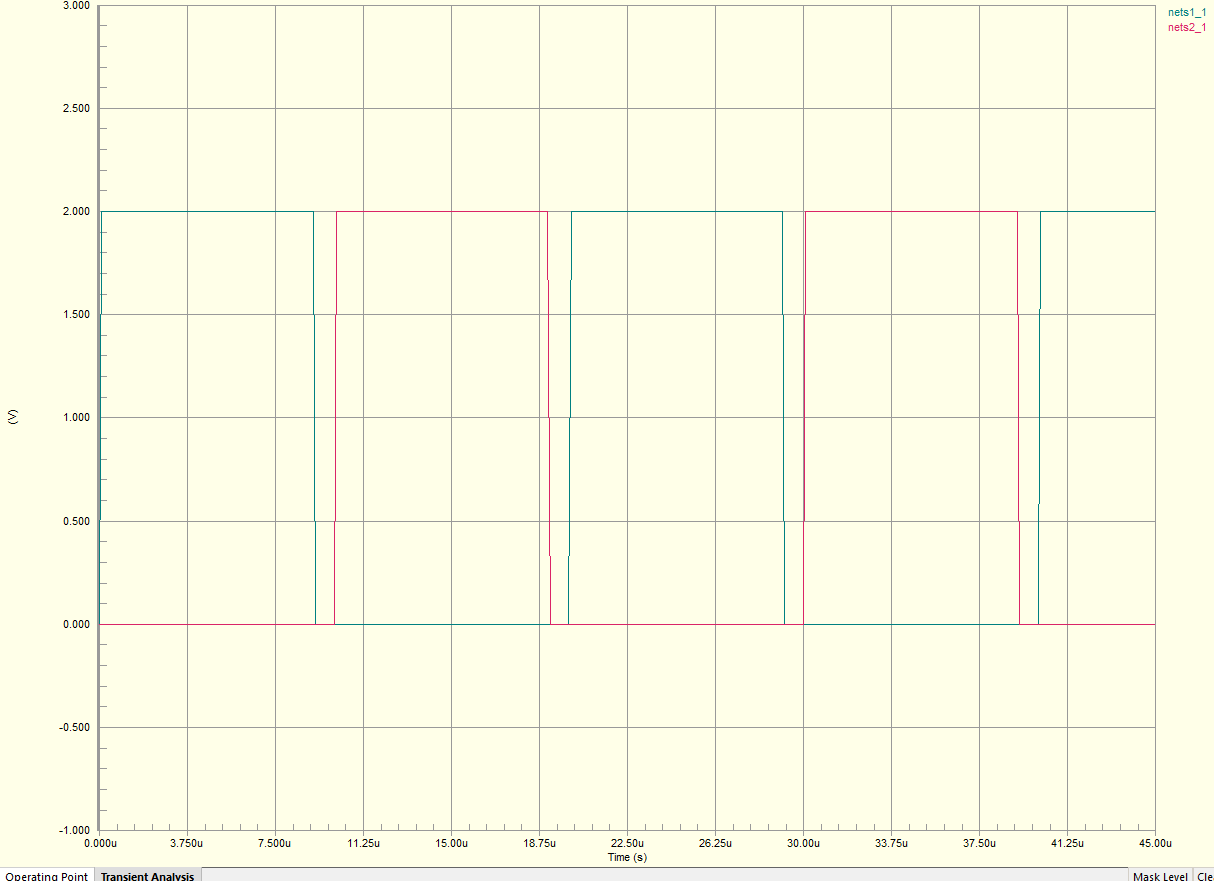

파형

Theory

스위칭 순서

SW1 ON SW2 OFF [0.45]

SW2 OFF SW2 OFF [0.05]

SW2 OFF SW2 ON [0.45]

SW2 OFF SW2 OFF [0.05]

펄스 계산

주기 20u * 0.45 = 9u (45%)

타임 딜레이

20u * 0.1 / 2 = 1u -> 9u + 1u = 10u

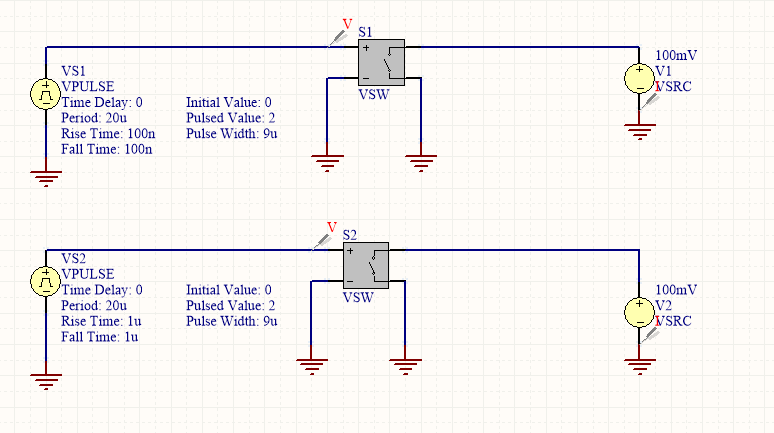

PWM 스위칭 정도 측정

회로

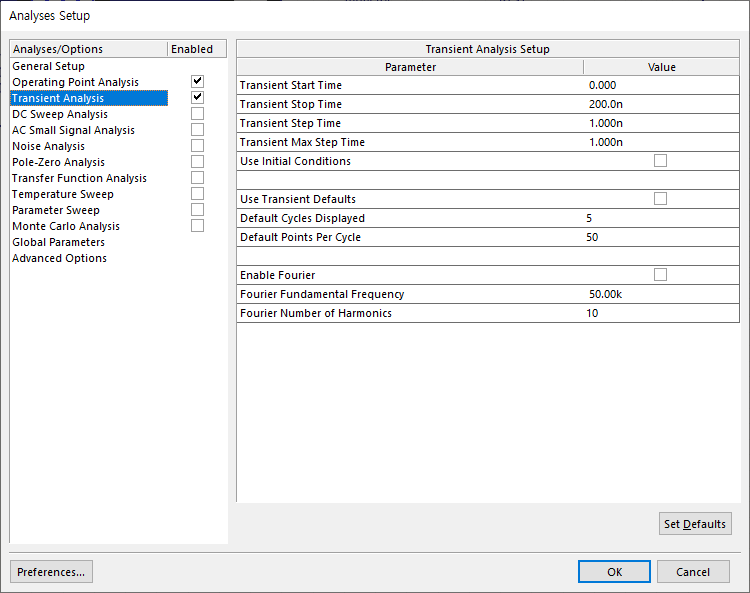

Setup(Step time)

파형

펄스전압과, VSRC의 전류 (본래는 스위치단이나 측정안됨) 비교

주의사항으로 스위치 내부저항 0.1 (100m) 이므로 높은 부하저항 X

데드 타임 (Dead Time)

PWM(Pulse Width Modulation) 스위칭에서 데드 타임(Dead Time)은 전력 변환기 등에서 두 개의 스위칭 소자가 동시에 도통(Conduction)하는 것을 방지하기 위해 설정하는 짧은 시간 간격

스위칭 신호의 상하단 또는 좌우 스위치가 동시에 켜지지 않도록 하기 위해 삽입하는 짧은 시간 지연

Upper switch가 OFF된 직후 → Lower switch가 ON되기 전까지의 시간

반대로도 마찬가지

데드 타임(Dead Time)의 필요성

- PWM 스위칭 회로에서는 보통 상하단에 두 개의 스위칭 소자(예: MOSFET, IGBT)가 사용.

상단 스위치와 하단 스위치가 동시에 켜질 경우, 전원과 접지 사이에 단락(Short Circuit)이 발생. - 이를 방지하기 위해 한 스위치가 꺼진 후 다른 스위치가 켜질 때까지의 지연 시간을 데드 타임으로 설정

- 쇼트 방지 (Shoot-Through)

상하 스위치가 동시에 켜지면 공급 전압이 직접 단락되어 MOSFET/IGBT 파손

스위치 지연 특성 보상

실제 소자는 꺼지기까지 시간이 걸리므로, 제어신호보다 늦게 꺼짐

동작 안정성 확보

고속 스위칭에서도 안전하게 구동 가능

설정 방법

Turn-off delay time (toff) 소자가 완전히 꺼지는데 걸리는 시간

Rise/Fall time 전류가 증가/감소하는 데 걸리는 시간

➜ 일반적으로 toff + 여유 margin = Dead Time

예: MOSFET toff = 50ns → Dead Time = 150ns 정도

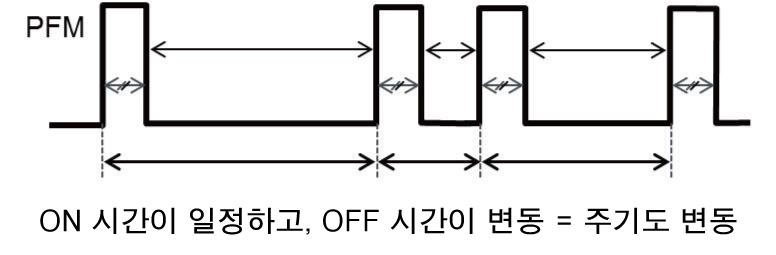

PFM 제어

(Pulse Frequency Modulation, 펄스 주파수 변조)

펄스의 폭(Duty)은 거의 일정하거나 고정,

대신 펄스가 발생하는 간격(주파수)를 조절하여 에너지를 제어하는 방식

- 필요할 때만 펄스를 발생 (비연속 모드)

부하가 적을수록 펄스 간 간격이 길어짐

평균 출력 전압은 펄스 빈도로 조절됨

-

PFM은 고정 ON 시간 타입과 고정 OFF 시간 타입 존재.

고정 ON 시간 타입은, ON 시간은 일정하고 OFF 시간이 변함.

(다시 ON되기까지의 시간이 변동 ) -

부하가 커지면, 시간 내의 ON 횟수를 늘려 부하에 대응.

중부하 시에는 주파수가 높아지고, 경부하 시에는 주파수가 낮아진다.

장점

경부하에서 매우 높은 효율 (대기 전력 소모 최소)

스위칭 손실이 매우 낮음

단점

제어 응답이 느리고 불연속적

출력 리플이 커질 수 있음

EMI(전자파 간섭) 스펙트럼이 넓음 → 민감 회로에 부적합

주파수가 변하므로 스위칭에 관련된 노이즈가 일정하지 않아 노이즈 제거가 어려워짐.

| 항목 | PWM | PFM |

|---|---|---|

| 제어 변수 | Duty Cycle (폭) | Frequency (빈도) |

| 스위칭 주기 | 일정 | 가변 |

| 효율 (경부하) | 낮음 | 매우 높음 |

| 응답 속도 | 빠름 | 느림 |

| 출력 리플 | 작음 | 큼 |

| EMI 제어 | 쉬움 | 어렵고 넓음 |

| 사용 예 | 고정 부하, 정밀 제어 | 저전력, 대기 전력 최소화 |

PWM: 일정한 주파수, 펄스 폭 조절 → 정밀 제어에 유리

PFM: 일정한 펄스 폭, 펄스 발생 빈도 조절 → 저전력에 유리

Ref

https://techweb.rohm.co.kr/product/power-ic/dcdc/897/

https://ebldc.com/?p=48

https://jungreeyoung.tistory.com/entry/%EC%A0%95%EB%B6%80%EB%85%BC%EB%A6%AC%ED%8E%84%EC%8A%A4%ED%8C%8C%ED%98%95%EC%A3%BC%EA%B8%B0%EC%A3%BC%ED%8C%8C%EC%88%98%EB%93%80%ED%8B%B0%EC%82%AC%EC%9D%B4%ED%81%B4

http://www.ktword.co.kr/test/view/view.php?m_temp1=4752&id=1433