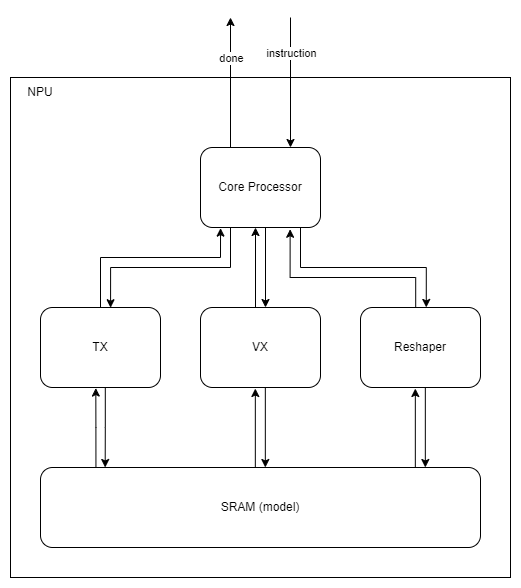

초안 기준 TOP level Architecture는 이와 같다.

TX는 Tensor eXecuter의 약자로 convolution이나 matric multiplication과 같은 연산을 수행한다.

VX는 Vector eXecuter의 약자로 TX에서 수행하지 못하거나 수행하기 비효율적인 연산들, matrix addition이나 maxpooling 등을 수행한다.

Reshaper는 sram에 저장된 tensor 데이터의 layout이나 모양 등을 변경하거나 복잡한 padding을 붙이는 일을 수행한다.

DDMA는 원래 들어가야하지만 위의 그림에는 빠져있는데 그 이유는 DDMA에 대한 공부가 많이 부족해서 일단 초안에는 넣지 않았고 추후에 추가할 예정이다.

SRAM은 초안에서는 간단한 model을 대신 넣을 예정이다.

초안에서 core processor는 아마 매우 간단한 구조가 될 것 같다. 이쪽도 공부가 많이 부족해서 아직 어떻게 설계할지 감이 잘 안잡힌다.

TOP 레벨에서의 clock과 각 IP의 clock은 분리할 예정이다.

SRMA과 각 IP의 clock도 같은 주파수를 사용해도 async fifo를 중간에 넣어서 분리할 예정이다.

일단 TX와 Reshaper는 이미 관련한 설계경험이 있어서 비교적 설계가 수월할 것 같은데 VX와 core processor 쪽은 모르는 부분이 많아서 좀 어려울 것 같다.