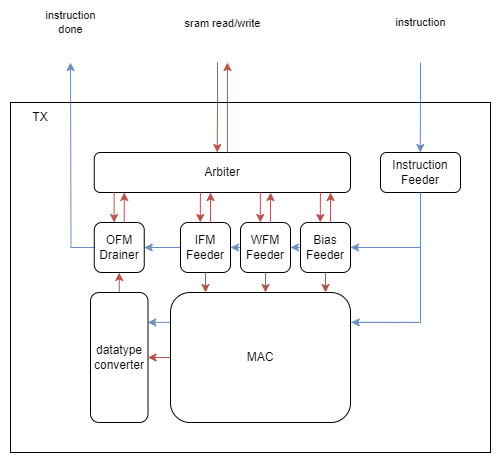

초안 기준 TX의 Architecture는 이와 같다.

IFM, WFM, Bias Feeder에서 instruciton에 따라 sram에서 필요한 데이터를 가져오면 MAC에서 이를 계산한 후 datatype converter를 통해 필요한 형식으로 변환한 후 OFM Drainer로 SRAM에 데이터를 저장한다.

Quantization type은 초안 단계에서는 Layerwise Quantization 까지만 지원할 예정이다.

이후 다른 Quantization type을 지원하기 위해선 Quantization Feeder가 추가되어야한다.

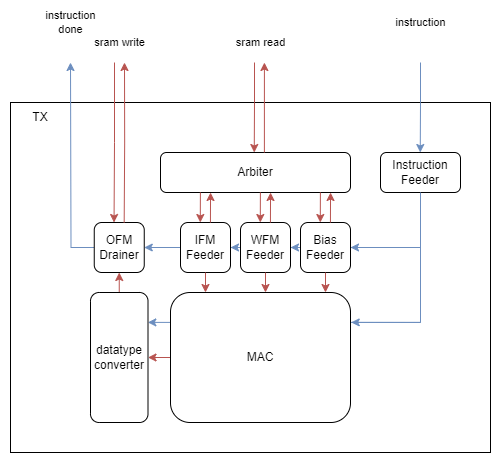

SRAM read port는 추후 quatization feeder까지 추가할 걸 고려해서 3개,

SRAM write port는 1개로 구성할 계획이다.

현재 TX 설계에서 가장 어려울 것으로 예상하는건 SRAM address generator의 설계다.

해당 모듈은 각 Feeder와 Drainer 뿐만 아니라 다른 IP에서도 공용으로 쓰일 예정인데 사실 v1에서도 해보려다가 너무 어려울 것 같아서 포기했던 모듈이다.

제대로 하려면 이거 하나 설계하는데도 한세월이라서 초안 버전에서는 가장 기초적인 기능만 들어간 정도로 설계할 예정이다.