2.13 SysTick

The SysTick timers in the Cortex-M processors support external reference " clock." Thechnically the reference "clock" in not a clock signal, as it is sampled by D-flip flops inside the SysTick at the processor's clock speed.

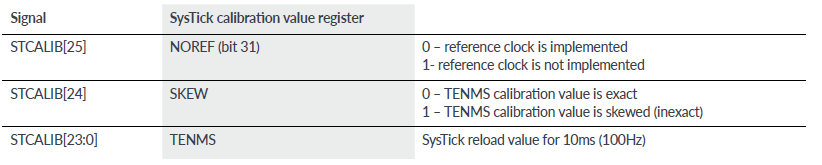

The SysTick interface also provides a calibration input, which is fed to the SysTick calibration value.

Ther support for SysTick reference clock and calibration value are optional.

-If no reference clock is provided, STCALIB[25] needs to tie high.

-If TENMS is not used, STCALIB[23:0] should be tied low, and STCALIB[24] needs to tied high.

- In CMSIS-CORE, an alternate way for software to determine system clock speed is provided that uses a software approach : the SystemCore Clock variable should provide the clock frequency information, and that is initialized and updated by the software whe nthe clock settings are updated.

2.14 Debug integration

Debug intergation typically involves several interfaces :

Interface for debug connection(JTAG or Serial Wire Debug) - for conncecting a debugger to ther hardware target to carry out halting, stepping, restart, resume, setting breakpoints/watchpoints, access to memories and peripherals. Debug connection is also used for downloading code and flash memory.

Interface for trace data(conncecting ATB from the processor and ETM to trace port) - enables the debugger to obtain real-time trace information, either using trace port protocol which contains multiple data bits(usually 4-bit) and a clock signal or using a single pin trace output protocol for trace with lower bandwidth(e.g., instrumentation trace, event trace).

The trace interface is optional and is not available on Cortex-M1, Cortex-M0 and Cortex-M0+ processors.

Coresight timestamp generation - CoreSight timestamp feature integrates timming information into the trace package. Real-time trace operation can take advantage of this to allow the debugger to restructure timming information. To allow this to work, some Cortex-M processors and ETM have a time stamp interface. typically, a simple counter is used to generate the time stamp value.

Debug authentication control - Cortex-M processors provide hardware interface signals to allow other harware blcoks in the system to control wheter debug and trace operations are allowed. Typically, devug authentication is controlled by security management IP blocks based on certificate-based authentication methods. For Armv8-M processor systems, there are separate debug authentication signals to define debug access permissions for Secure and Non-secure environments.

Debug system clock and reset generation, and power management - depending on which processor is used, the debug system can have its own clock and reset signals, and in some designs, debug logic can be powered down or clock gated if not being used.

2.15 Power nanagement features

Cortex-M processors(except Cortex-M1 which is designed for FPGA) support a range of low-power features.

Sleep modes - architecturally, the processor can have sleep and deep sleep, but these sleep modes could be extended with additional system-specific registers to have addition granularity of sleep characteristics. Ther processors have sleep mode status output signals so that system designers can use these signals to control clock gating and other power management hardware.

Sleep hold interface - in the case where a system designer utilizes sleep mode signals to turn off hardware resource (e.g., program ROM), the wake-up process can take a while(e.g., program ROM), the wake-up process can take a while(e.g., hundreds to thousands of clock cycles). In such cases, it is essential to be able to hold off the processor's program excution, and sleep hold interface is designed exactly for his purpose. To use this feature, the system designer needs to design a simple Finite State Machine to handle th handshaking with the sleep hold interface.

->Sleep hold interface는 인터럽트와 비슷한 방식으로 동작합니다. 시스템 설계자는 Sleep hold 인터페이스의 출력을 모니터링하고, Sleep hold 인터페이스가 활성화되면 특정 상태로 전환하여 프로세서를 일시 중지시킵니다. 프로세서가 일시 중지된 동안, 리소스를 깨우기 위한 외부 이벤트를 모니터링하고, 이벤트가 발생하면 Sleep hold 인터페이스를 해제하여 프로세서가 다시 실행될 수 있도록 합니다.

Wakeup Interrupt Controller(WIC) - explained in this chapter earlier, the WIC is an optional feature that allows interrupts or other wakeup events to be detected when the processor is in a powered-down state, retention state, or if the clock to the processor is gate off. The system desiner can sutomize the example WIC design if needed

Debug power management - the debug interface modules provides handshaking signals to indicate whether there is a debugger connection, which allows system designers to implement power management for the debug system of the processors if needed. For example, in Cortex-M0 .... and Cortex-M35P processors, there is a sperate debug power domain that can be powered down if there is no debug connection.

System designers are also likely to intergrate additional power management features for memory blocks, clock generation and distribution systems, and some of the peripherals.

2.16 Top-level pin assignment and pin multiplexing

One of the tasks that chip designers need to do is to define the top-level signals of the devies. Often, Many of the pins on the chips carry multiple functions . For example, a pin might be configuratble to work as as GPIO pin, a communication interface pin, or a debug/trace pin. You can find examples of pin multiplexing in Cortex-M3 DesignStart Eval.

Apart from the debug and trace signals, normally there is no need to expose other interfaces of the Cortex-M processors directly to the top-level of the devices.For external interrupt generation, usually, that is handled by GPIO blocks so that external hardware can trigger interrupts via GPIO. in some caes, chip designers can also implement a signal path to allow off-chip hardware to generate and event pulse to the Cortex-M processor so that it can wake up from WFE instruction; however this is not essnetial for many system.

When designing top-level pins, several areas related to the Cortex-M processors should be considered:

- In most cases, the debug interface pins(JTAG or Serial Wire Debug) need to be accessible at the device's top-level by default. For Cortex-M3, Cortex-M4 and Cortex-M33 processors, the debug interface module supports dynamic protocol switching, so it is possible to expose just two pins of the SWD debug by defulat. If there is a need to switch over to JTAG, then you can program a device-specific pin multiplexer(mux) control register to expose the other pins for JTAG, and then apply a switchover sequence to start JTAG operations.

-The SWD interface requires a tristate pin for the data connection(SWDIO), which is enabled when SWDIEN is high.

-If the debug interface is multiplexed with other peripheral I/O pins, the peripheral I/O operations can cause a debug connection to be disconnected.

-

The debug and trace interface provides a range of status signals to allow some of the signals to be multiplexed with functional pins. it is also possible to use device vendor needs to provide the details of the setup sequence for various debug tools to allow them to work correctly with the device.

-

When creating systems using Armv8-M provessors with Trust Zone, the debug conmection might contain Secure information, and therefore the pin multiplexing logic needs to prevent Non-Secure software from seeing activities in the debug connection.

2.17 Miscellaneous Signals

Cortex-M processors provide variable status signals that can be used by system designers. For example, in Figure 2.12 , we show that the LOCKUP status could be used to generate system resets automatically. The availability of other status signals depends on the processor you use.

Newer Cortex-M processors support a CPUWAIT signal. This is used to delay the start-up of the processor after releasing from reset. In most single-core systems, this pin can be tied low. In multi-core Soc designs when the Cortex-M subsystem is running a program in SRAM, the CPUWAIT signal can be used to delay the boot-up so that s different bus master can trasfer program image into the SRAM. After the program image is loaded, the CPUWAIT signal can be released, and the Cortex-M processor can start excuting the program.

-> SRMA에 boot data 올때 까지 대기 신호