3.1 What is AMBA?

3.1.1 Introduction to Advanced Microcontroller Bus Architecture

Almost all the AMBA specifications have the follwing characterisic:

Synchronous operations - use only clock rising edge for flip-flops, friendly to common synthesis flow;

No on-chip bi-directional signals - avoiding the need for tri-state buffers.

The most common AMBA Bus Protocols used in microcontrollers in include:

AHB(Advanced High-performance Bus) - a lightweight pipelined bus protocol used in the majority of the Arm Cortex-M processors.

APB(Advanced Peripheral Bus) - a simple bus protocol for connecting general simple peripherals with low data bandwidth requirements.

AXI(Advanced eXtensible Interface) - a high-performance bus protocol for efficient, high-performance processors includeing the Cortex-M7 processor, Cortex-R processors and the majority of the Arm Cortex-A Processors. The AXI Protocol :

- Provides multiple data channels running concurrently at high clock frequency.

- Allows new transfers to be isseud and take place even with previous transfers still outstanding.

- Supports unaligned data and procides data security based on TrustZone technology.

3.2.1 Various version of AHB

AMBA 2 AHB - first release. This Specification release uses a pair of handshaking signals ( Bus Request and Bus Granted ) for arbitration between bultiple bus masters.

Multi-layer AHB designs - The AMBA Design Kit product from Arm introduced an AHB interconnect component called AHB Bus Matrix. This enables conurrent bus transfers in multi-master systems for higher bandwidth, avoids the need for the Bus Request and Bus Granted signals, and was unofficially called

- 버스 요청과 Grant 를 없앴다? -> AHB Lite 만 해당인가?

In the AMBA 3 Specification, AHB Lite became the official name. It removed Bus Request and Bus Granted signals and simplified several other aspects of the AHB protocol. it is used on many Arm processor systems.

In the AMBA 5 specification, AHB has been updated to support TrustZone for Armv8-M and add official support for exclusive access sideband signals. It also intruduced several improvements including additional cache attribute supoort and clarifications.

3.2.2 AHB signals

An AHB system operates with a clock signal called HCLK. This signal is common to all bus masters, bus slaves, and the bus infrastructure blocks in a bus segment. All registers on the AHB trigger at rising edges of HCLK. There is also an active-low reset signal called HRESETn. Sehn this signal is low, it resets the AHB system immediately(asysnchronous reset). This allows a system to be reset even if the clock is stopped.

For correct operation, the HRESETn signal itself should be synchronized to HCLK so that race conditions can be avoided. Otherwise, if the HRESETn de-asserts about the same time as HCLK rising edge, you might find that parts of the registers are still reset at the clock edge and some are not.

| Signals | Direction | Descriptions |

|---|---|---|

| HCLK | Clock source ->all AHB blocks | Common clock signal |

| HRESETn | Reset source -> all AHB blocks | Common active-low reset signal |

| HSEL | Address decoder -> Slave | Device Select |

| HADDR[31:0] | Master->Slave | Address bus |

| HTRANS[1:0] | Master->Slave | Transfer Control |

| HWRITE | Master->Slave | Write Control(1=write,0=read) |

| HSIZE[2:0] | Master->Slave | Transfer Size Control |

| HBRUST[2:0] | Matser->Slave | Transfer Burst Type Control |

| HPROT[3:0]/[6:0] | Master->Slave | Transfer Protection Control. 4 bits in AHB Lite, extended to 7bits in AHB5 |

| HMASTER[3:0] | Bus Component->Bus Slave | Indicates Current Bus Master identity |

| HWDATA[31:0] | Master -> Slave | Write data (typically 32-bit, but it can be 64bit wide on 64bit systems) |

| HRDATA | Master <- Slave | Read Data(Typically 32-bit, but it can be 64-bit wide on 64-bit systems) |

| HRESP[1:0]/HRESP | Master <- Slave | Slave response |

| HREADY(HREADYOUT) | Master <- Slave(HREADYOUT), Bus Componet -> Ohter Slaves(HREADY) | Slave Ready(transfer Completed).The HREADY signal goes two ways. The currently selected slave drives the HREADY to bus master as well as all otehr AHB Slaves. As a result, an AHB slave has HREADY input and HREADYOUT output. |

->HTRANS 신호는 아래와 같이 3가지 유형으로 구분됩니다.

HTRANS[1:0] = 0b00: Non-sequential transfer (비순차 전송)

HTRANS[1:0] = 0b01: Sequential transfer (순차 전송)

HTRANS[1:0] = 0b10: Wrap transfer (Wrap 전송)

| Signals | Direction | Descriptions |

|---|---|---|

| HCNONSEC | Master->Slave | Security attribute of the transfer(TrustZone Support) |

| HEXCL | Master->Slave | Indicates the transfer is Exclusive access |

| HEXOKAY | Master<-Slave | Exclusive access success response |

| HAUSER | Master->Slave | Optional user sideband for address phase signals(the actual definition ofthis signal is system-specific) |

| HWUSER | Master->Slave | Optional user sideband for data phase signals |

| HRUSER | Master->Slave | Optional user sideband for data phase signals |

For Older AHB system

| Signals | Direction | Descriptions |

|---|---|---|

| HBUSREQ | Master->Arbiter | Bus Access request |

| HGRANT | Master<-Arbiter | Bus Granted |

| HLOCK | Master->Arbiter | Lock Transfer Control |

| HMASTER | Arbiter<-Slave | Transfer Lock Control, In newer AHB systems Arbiter is not used and HMASTLOCK is generated by the bus master of bus interconnect |

3.2.3 Basic Operations

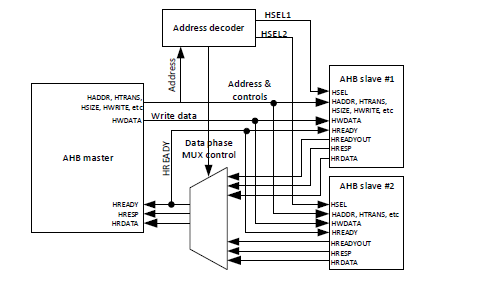

-> Address Decoder 가 HSEL 을 통해 AHB Slave를 정해주고,

-> HRDATA, HRESP, HREADY는 Address Decoder 에서 나온 Mux Control 신호를 통해 선택된다.

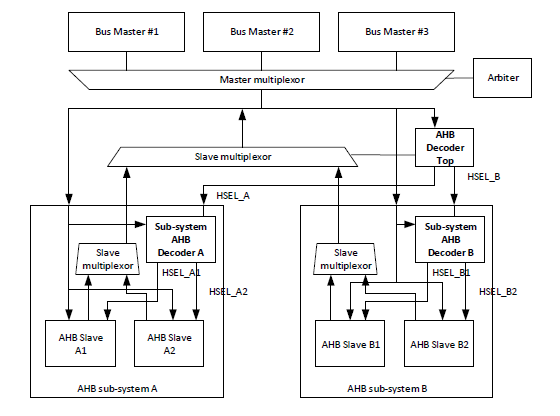

The connections between AHB masters and AHB Slaves based on the AMBA 5 Specification can be viewd in the following diagram: Multiple bus masters share the same bus using a master multiplexer,controll by a bus arbiter. The return data and responses from bus slaves are also multiplexed using a slave multiplexer and feedback to the bus masters.

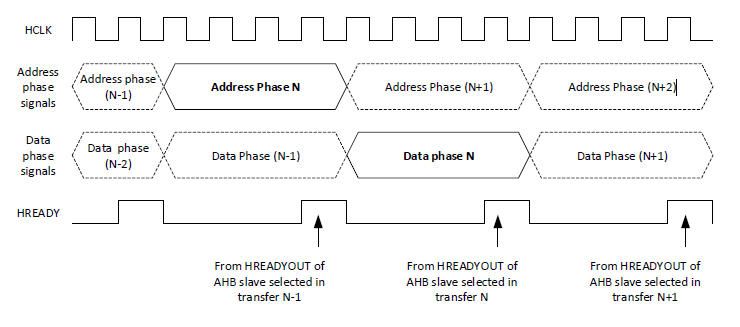

The signals are grouped into "address phase" signals and "data phase" signals.

The address phase signals include:

HADDR, HTRANS, HSEL, HWRITE, HSIZE.

Optional:HPROT, HBURST, HMASTLOCK, HEXCL, HAUSER.

The data phase signals include:

HWDATA, HRDATA, HRESP, HREADY(and HREADYOUT)

Optional : HEXOKAY, HWUSER, HRUSER.

Each Transfer is composed of an address phase and data phase. The transfer are pipelined. The address phase of a transfer

Figure 3.2: Splitting of a transfer into address phase and data phase.

Each phase is terminated by the assertion of HREADYOUT(HREADY) from the currently activated AHB slave in the data phase. The HREADYOUT from the AHB slaves are multiplexed by the slave multiplexer, forming the system-wide HREADY signal.

The Multiplexed by the slave Multiplexer, forming the system-wide HREADY signal. The multiplexer is operting at the data phase of each transfer. Control of the multiplexer can be generated from the AHB decoder, or the HSEL signals and the HREADY signal.

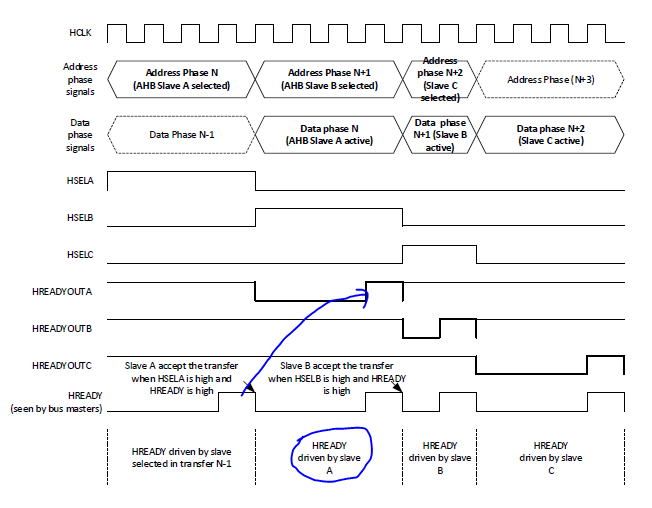

If an AHB slave is not currently selected, its HREADYOUT should be high to indicate it is ready. However, it can only accept a transfer from the bus master when the previous transfer is completed,

indicated by a high level in the system-wide HREADY. For example, if transfer N selects AHB slave A, transfer N+1 selects AHB slave B, and transfer N+2 selects AHB slave C, the waveform can be like

-> HREADY TRANSACTION 하나가 끝나면 그 때 HREADY를 올릴수 있다.

3.2.4 Minimal AHB systems

In a minimal AHB system with a single bus master and bus slaves, we would expect to find the following components:

| Components | Description |

|---|---|

| Address Decoder | Based on HADDR input, generates HSEL signals to bus slaves and AHB slave multiplexer |

| AHB slave multiplexer | Connect multiple bus slaves to a single AHB segment |

| Default Slave | This is selected when the transfer address(HADDR) does not match the address range of other AHB slaves. This only happens when something has gone wrong(e.g., the software attempts to access an invalid memory location due to an error in C pointer processing). This bus slave only returns an ERROR response when accessed, write data is ignored by the default slave, and it returns 0 for read accesses. Default slave is optional - if the address space is fully-utilized by other bus slave, then there is no default slave. |

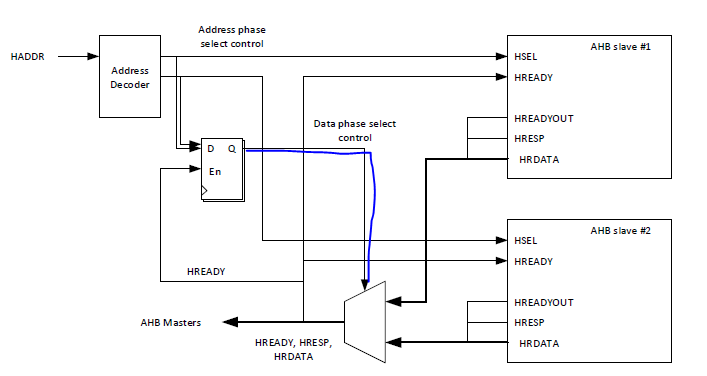

The desing of the address decoder is system-specific - each system has its memory map, and the chip designers need to create the address decoder for each bus slave accordingly. The HSEL signal is an address phase signal generated by decoing the HADDR signal.Since the HSEL generation process is combinatorial, the design of memory maps needs to avoid complex decoding of HADDR.Otherwsie, the synthesis timeing could be affeced.

-> memorymap을 이용하여

The design of AHB slave multiplexer can be much more generic and is available in various Arm AHB based system IP bindles. Since each AHB slave has their own read data output and resonse outputs,

-> 각각 AHB Slave 는 그들만의 read data output 과 response output 를가지고 있다.

an AHB slave multiplexor is needed to select the return data and response from the current active slave.

The slave multiplexer is controlled by a data phase version of the HSEL signal(delayed by one pipeline stage). This can be generated by registering the HSEL with system-wide HREADY as the enable signal, as shown in Figure 3.3. In most cases, the finctionality of delaying the HSEL is included within the AHB slave multiplexor, so the system integrator only needs to connect the address phase HSEL to the AHN Slave Multiplexor.

3.2.5 Handling of multiple bus masters

The connections between AHB masters and AHB slaves based on the AMBA 2 Specification can be viewed as the following diagram : multiple bus masters share the same bus using a master multiplexed using a slave multiplexer, and feedback to the bus masters.

A bus master must first assert a bus request (HBUSREQ) to the arbiter, then

After arbitration, the arbiter returns the bus granted signal (HGRANT) to one of the bus masters, then

The bus master can then generate transfers on the bus.

This arragement works for simple systems, but the maximum bus bandwidth is limited. When the AMBA Design kit(ADK) prodict was launched, a new approach called multi-layer AHB was used to support multiple bus masters.

The AHB Bus Matrix component in the ADK is an AHB interconnect component with multiple bus ports for connections to bus masters and multiple bus ports for connection to AHB slaves. Potentially, each bus port for bus slave connection could have multiple bus slaves connected to it by having addtional bus slave multiplexer.

To resolve the bus access conflict when multiple bus masters try to access to the same bus slave at the same time, each master port(the port that connects to AHB slaves) has an arbiter. if a transfer from a bus master is targeting a bus slave, which is accessing by a different bus master, the incomming trasfer is held in the input stage with a buffer. With his arragement, the HBUSREQ and HGRANT signals no longer needed.

The bus matrix design allows differnt bus masteres to access to differnt bus slaves at the same time, hence enhance the system bandwidth.

3.3 More details on the AHB protocol

3.3.1 Address phase signals

There are several essential transfer control signals in the address phase. There are HTRANS, HADDR, HWRITE, and HSIZE.

The HTRANS signal is used to indicate transfer types. Most AHB systems do not need to handle data transfers 100% of the time. When a bus master does not need to start another transfer immediately.it can issue an idle transfer. The HTRANS signal in the AHB is used to indicate if the current transfer is an active transfer or in idle state.

| HTRANS[1:0] | Description |

|---|---|

| 00 | IDLE(non-active) |

| 01 | BUSY(non-active) |

| 10 | Non-Sequential(active) |

| 11 | Sequential(active) |

Table 3.7 : HTRANS encoding.

When a data transfer is needed, the AHB master generates a Non-sequential(NSEQ) or a Sequential(SEQ) transfer. NSEQ is used in normal transfers or at the beginning of a burst transfer, and SEQ is used for the remaining part of a burst transfer, indicating that the transfer is a continuation of the previous one.

NSEQ 는 Busrt 모드의 첫번째 나머지 Transaction 은 SEQ

Bot IDLE and BUST are non-active transfers. It means that no real data transfer takes place. BUSY is only used when the bus master has started a burst transfer but is not ready to handle the next data transfer.

-> BUSY는 Busrt 모드가 실행됫고 다음 Transfer 을 실행할 준비가 안됫을대.

In this case, it issues the BUSY transfer between the burst transfers to keep the burst sequence going, and continues with the next sequentialtransfer when it is ready.

The HADDR signal is usually 32-bit and specifies the address of the transfer. HWRITE signal indicates that the transfer is a write transfer it is set to 1, or if it set to 0, then the transfer is a read operation.

The HSIZE signal is used to indicate the data size to be transferred. typically, the HSIZE signal is 3-bit wide, but in most AHB systems only the lowest two bits are used so that you might find some systems or AHB componets with HSIZE of only two bits.

HSIZE[2:0] Size of transfer

000 Byte

001 Half-word

010 Word

011 Double word (64-bit)

100 128-bit

101 256-bit

110 512-bit

111 1024-bit

When a bus master generates a transfer, the bus master should ensure that the data being transferred is aligned. In other words, a half-word transfer should only take place in event memory addresses, and a word transfer should only take place in addresses divisible by 4. The AHB interface does not support unaligned transfer; if a bus master needs to acess unaligned data, it should split the transfer into multiple aligned AHB transfer of smaller size.

The Cortex-M processors can generate read and wrtie transfers of byte, half-word, or word size. In some of the Cortex-M processors like the Cortex-M3 and Cortex-M4, instruction fetched are always in word size. For some others like the Cortex-M0+ and Cortex-M23 Processors, insruction address alignment.

Besides the crucial AHB control signals, there are also optional sideband signals in the AHB interface.

They are helpful for processor systems, for example, providing privilege level information and supporting burst transfers. However, they migh not be present in some AHB systems.

| signals | Descriptions |

|---|---|

| HPROT[3:0]/[6:0] | Protection information(AHB5 has 7bits of HRPOT, and previous versions of AHB has 4-bits) |

| HNONSEC | Security attribute(available in AHB5 only. This is needed for TrustZone security extension) |

| HBURST[2:0] | Busrst transfer information |

| HMASTLOCK | Indicate the transfer sequence is atomic, so bus owenership is locked until this signal is released |

| HMASTER[3:0] | Indicates which bus master issued the current transfer. |

| In some Cortex-M processors, this signal is used to indicate the transfer types(e.g., whether the transfer is generated by the debugger).The width of this signal can be customized to fit the system requirement. | |

| HEXCL | Exclusive access indication signal. This signal is introduced in AHB5 to support exclusive accesses in Arm Processors. The bus slave response to exclusive access with HEXOKAY, a data phase signal. |

| HAUSER[x-1:0] | This is a user-defined address phase signal introduced in AHB5. Potentially it could be used for the following: propagation of addtional information about the transfer; |

| parity bits for address phase control signals. |