3.2 Overview of AHB

In AMBA 2 AHB and AHB Lite, the HPROT signal contains 4bits, each of them has a different function:

| signal | Function | When equal 0 | When equal1 |

|---|---|---|---|

| HPROT[0] | Data/Opcode | Instruction fetch | Data Access |

| HPROT[1] | Privileged | Non-privileged(user) | Privileged |

| HPROT[2] | Bufferable | The transfer must complete before a new transfer is issued | Write transfer can be buffered |

| HPROT[3] | Cacheable | Data cannot be cached | Data can be cached |

When accessing to normal memories(not peripherals), the encoding of the HPROT[3:2] can be used to indicate cache types:

| HPROT[3:2] | |

|---|---|

| 2'b00 | Device(non-bufferable) |

| 2'b01 | Device(bufferable) |

| 2'b10 | Cacheable memory with Write Through |

| 2'b11 | Cacheable memory with Write Back |

In AMBA 5 AHB, the cache attribute information is extended, and as a result, the HPROT signal becomes:

| Signal | Function | When equal0 | When equal 1 |

|---|---|---|---|

| HPROT[0] | Data/Opcode | Instruction Fetch | Data Access |

| HPROT[1] | Privileged | Non-Privileged(user) | Privileged |

| HPROT[2] | Bufferable | The Transfer must complete before a new transfer is issued | Write transfer can be buffered |

| HPROT[3] | Modifiable | Data cannot be cached | Data can be cached |

| HPROT[4] | Lookup | The transfer is not cached | The transfer must be looked up in the cache |

| HPROT[5] | Allocate | No need for cache line allocation | Allocate cached line on cache miss |

| HPROT[6] | Sharable | data is not shared(no need to maintain dta coherency) or transfer is to a Device(Non-cacheable) | Bus interconnect needs to ensure data coherency |

The cache type indication with AMBA 5 AHB is shown below:

| HPROT[6] | HPROT[5] | HPROT[4] | HPROT[3] | HPROT[2] | Memory Type |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | Non bufferable Devices |

| 0 | 0 | 0 | 0 | 1 | Bufferable Device |

| 0 | 0 | 0 | 1 | 0 | Normal Non-cacheable, Non-shareable memory |

| 0 | 0or1 | 1 | 1 | 0 | Write Thorugh, Non-shareable memory |

| 0 | 0or1 | 1 | 1 | 1 | Write Back, Non-shareable memory |

| 1 | 0 | 0 | 1 | 0 | Normal Non-cacheable,shareable memory |

| 1 | 0or1 | 1 | 1 | 0 | Write Throught, shareable memory |

| 1 | 0or1 | 1 | 1 | 1 | Write Back, Shareable Memory |

The Cortex-M0 processor does not have a user access level, so HPROT[1] is always 1. Since Cortex-M0/M0+/M3/M4/M23/M33 processors do not support internal cache, the cacheability information is often not used.

-> Cortex-M0 는 HPROT[1] 가 항상 1 임. Privileged / Non-Privilged 개념이 없음.

Another address phase signal is HBURST, which indicates a burst transfer type. Burst transfer can often improve system performance if the memory device can access data quicker when the accesses are in sequential orders. If a burst transfer is used, the HBURST signal will indicate the burst transfer type. AHB supports several types of burst transfer:

-> 메모리 장치가 순차적인 순서로 액세스되는 경우 데이터에 빠르게 액세스할 수 있으므로 버스트 전송은 시스템 성능을 향상시킬 수 있습니다.

Single.(Not burst transfer.Each transfer is separated from each other.)

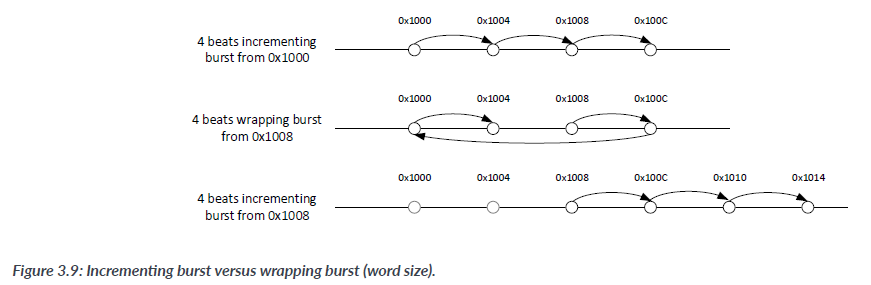

Incrementing burst transfer.(The address is incremented by the size of the transfer.)

Wrapping burst transfer. For each transfer, the address increments as in an incrementing burst except when the address reaches the block size boundary of the burst. In this case, the address wraps round to the beginning of the block size boundary. The block size of the burst can be determined from the number of beats times the size of each transfer.

Burst transfer sequence is composed of multiple "beats." Each beat is an AHB transfer with addresses linked to others inside the burst. Within a burst, the transfer size, direction, and control information of each transfer must be the same-. Both incrementing and wrapping bursts are supported for 4-beats, 8-beats, and 16-bates transfers. Incremental bursts can also be of unspecified length.

| HBRST[2:0] | Burst Type | Descriptions |

|---|---|---|

| 000 | single | Singl transfer(not burst) |

| 001 | INCR | Incremeting burst of unspecified length |

| 010 | WRAP4 | Wrapping burst with 4 beats |

...

Wrapping Burst is useful in cache controller designs. For example, when a processor requests to read word data in address 0x1008, a cache controller for cache line size of 4 words might want to fetch address 0x1000, 0x1004, 0x1008, and 1x100c in to the ache memory. In this case, it can use a 4-beats incrementing burst from address 0x1000, or a warpping burst from address 0x1008. If wrapping burst is used, the address wraps around in a block size boundary, which is four times word size, or four word. Therefore , the addres wraps around to 0x1000 after the transfer to 0x100C.

The wrapping burst transfers the same data as the incrementing burst, but it has the additional advantage that the data needed by the processor can be transferred first, hence, reducing the waiting time in the procesoor.

-> incr burst랑 비슷하지만 wrapping은 processor 가 원하는 데이터를 첫번째에 준다.

Wrapping burst is commoly used by cache memory line fill. it allows the processor core to access the required data as soon as possible while allowing the rest of the data in the cache line to be cached. Unlike wrapping busrt, an incremeting burst from address 0x1008 will not fetch the data in 0x1000 and 0x1004, so it is not suitable for caching because the data for the cache line is not complete.

Burst transfers can be carried out in different data sizes(e.g. byte, halfword, word, etc.). For each beat, the address calculation should be adjusted by the size of transfer data. There is a restriction in burst generation: An AHB busrt must not cross a 1K byte address boundary, a 10-bit counter will be sufficient for all possible burst transfers.

It prevents a burst from going across multiple AHB slaves. If a burst crosses a device memory boundary, the second device receiveing the burst will have a SEQ transfer as its first transfer, which violates the AHB protocol.

HMASTLOCK is used to indicate the bus ownership should be locked for an atomic acess sequence. When HMASTERLOCK is set, the bus infrastructure(e.g., arbiter) must not switch the bus ownership until the HMASTLOCK is released. This is commonly used for semaphore operations, where a memory location(lock flag) is used to indicate a resource is locked by ap process or processor.

-> HMASTLOCK 은 세마포어 같은것.

When a processor needs to lock a resource, it carries out a locked transfer sequence that reads the lock flag and then updates it. Since the read-modify-write transfers are locked(atomic), another bus master cannot change the lock flag between the two transfer, and hence this prevents race conditions.

Apart from the Cortex-M3 and Cortex-M4 processor, most of the Cortex-M processors do not use HMASTERLOCK signal. In Cortex M3 M4. HMASTERLCOK is used for atomic read-modify-write when a bit-band wrtie operation take place. For other Cortex-M processors, if the processor top-level does not have HMASTERLOCK and connects to a standard AHB component that has HMASTERLOCK. The unused signal can be tied to 0.

In a system with multiple bus masters, the arbiter or master multiplexer can output a signal called HMASTER. This is used as an ID Value for AHB slaves. In most cases, the AHB slave does not need to know which bus master is accessing it. However, in a few cases, a peripheral might need to have different behaviors when accessed by different bus masters. In the Cortex-M processors, often the HMASTER signal is used to indicate if the transfer is generated by software running on the processor or by debugger connected to the processor.