3.6 Overview of APB

3.6.1 Introduction to the APB bus system

APB is a simple bus mainly targeted for peripherals connections. It was introduced as part of the AMBA 2 specification, and the functinalities have been extended in AMBA 3 and AMBA 4 to allow wait states, error responses and additional transfer attributes(including TrustZone support). Most APB systems are 32-bit.

Although it is possible to directly connect a peripheral to the AHB, separating peripheral connections using APB has various advantages:

1.Many system-on-chip designs contain large numbers of peripherals. If they are connected to the AHB system bus, they could reduce the maximum frequency of the system due to high signal fan out and complex address decoding logic. Grouping peripheral connections in the APB can reduce the performance impact on the AHB.

-

A peripheral subsystem can run at a different clock frequency, or be powered down without affecting AHB.

-

APB interfaces use a simpler bus protocol, which simplifies the peripheral designs as well as reducing the verification effort.

4.Most Peripherals designed for traditional processor can be connected to APB easily as APB transfers are not pipelined.

An APB system operates with a clock signal called PCLK. This signal is common to bus master(usually an AHB to APB Bridge), bus slaves and the bus infrastructure blocks. All registers on the APB trigger at rising edges of PCLK. There is also an active-low reset signal called PRESETn. When this signal is low, it resets the APB system immediately (asynchronous reset). This allows a system to be reset even if the clock is stopped. Like the reset signal in AHB(HRESETn), the PRESETn signal itself should be synchronized to PCLK so that race condition

-> 클락이 멈춰잇을때도 reset 을 할수잇음.

In most simple systems with both AHB and APB, PCLK is from the same clock source as HCLK, and PRESETn is from the same reset source as HRESETn. However, there are also systems that use separate HCLK and PCLK frequencies. In that case, the AHB to APB bus bridge desin will need to be able to handle the data transfer across different clock frequencies or different clock domains.

-> different clock frequencies or different clock domains. 에 해당하는 방어로직을 설계해야한다?

3.6.2 APB signals and connection

For a typical APB system, you can find most of the following signals :

| Signals | Direction | Descriptions |

|---|---|---|

| PCLK | Clock source -> all APB Blocks | Common clock signal |

| PRESETn | Reset Source -> all APB Blocks | Common active-low reset signal |

| PSEL | Address decoder -> Slave | Device select |

| PADDR[n:0] | Master->Slave | Address bus(see text below regarding bus width) |

| PENABLE | Master->Slave | Transfer Control |

| PWRITE | Master->Slave | Write control(1=Write,0=Read) |

| PPROT[2:0] | Master->Slave | Transfer Protection control |

| PSTRB[n-1:0] | Matser->Slave | Byte Strobe for write operations |

| PWDATA[31:0] | Master->Slave | |

| PRDATA | ||

| PSLVERR | Master<-Slave | |

| PREADY | Master <- Slave | Slave ready |

=> 이 바이트 스트로브 신호는 데이터 버스의 대역폭을 효율적으로 활용하고, 비트별로 데이터를 선택적으로 쓸 수 있는 기능을 제공합니다.

Normally, the APB only occupies a small part of the memory space. As a result, the address bus of the APB system is normally less than 32-bit. There is no transfer size control on APB. All transfers are assumed to be 32-bit, and usually, the two LSB(bit 1 and bit 0) of the PADDR are not used because a word transfer on APB must be aligned.

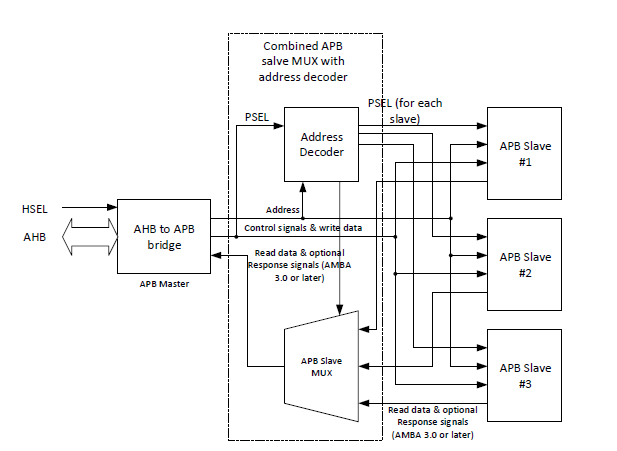

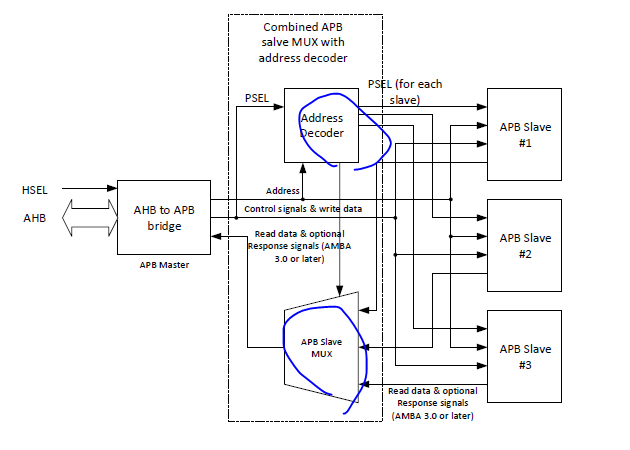

In most cases, an APB system has a bus bridge as the bus master that connects the APB to the main processor bus. In addition, and APB slave multiplexer and an address decoder are needed, which is sometimes a combined unit.

During a write transfer on APB, the actual write operation in the slave could happen either in the first clock cycle or in the second cycle.

This is implementation-defined. Therefore, the APB master must ensure that the write data is valid for both clock cycles. There can be any number of clock cycles between two transfer on APB

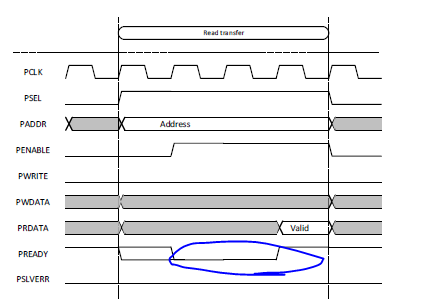

With AMBA 3, each APB slave can extend a transfer by de-asserting the PREADY output signal or feedback with an error response by the PSLVERR. For example, if an APB Slave needs 4 clock cycles to complete a read transfer(3 wait states), the read operation waveform will be like:

the end of the read transfer is indicated by the asertion of PREADY. The minimum number of cycles for the APB transfer is two cycles(same as AMBA 2), and the value of PREADY is ignored in the first cycle of the transfer so that even if its value is logic 1, the transfer still take at leat two cycles. In the previous example, the AHB slave responds with OKAY(indicated by logic zero on PSLVERR when). if an APB slave resonse with an error

When an error response is generated, the read data from the AHB slave might not contain any useful information and could be discarded. The value of PSLVERR is only valid when PREADY is high and not in the first cycle of the transfer. For example, if PSLVERR and PREADY are both high in the first cycle of the transfer, it is not considered as an error response as an APB transfer must be at least two clock cycles.

The waveform for APB writes in AMBA 3 are very similar. For write operations with an okay response, the waveform would be like :

3.6.3 Additional signals in APB protocol v2.0

The APB v2 in AMBA 4 added the PPROT and PSTRB siganl.

PPROT is similar to HPROT in AHB and is asserted througjout the whole transfer. However, it is only 3-bit wides.

| signal | function | when equeal0 | when equeal 1 |

|---|---|---|---|

| PPROT[0] | privileged | Non-Privileged(user) | Privileged |

| PPROT[1] | Non-secure | Secure access | Non-Secure access |

| PPROT[2] | Data | Data access | Instruction Access |

Please note, unlike AHB5, the TrustZone security attribute is part of PPROT instead of a separate signal.

AMBA 4 APBv2 also introduces byte strobe signals for write operations. For a 32bit APB,the PSTRB signal is 4bits - one bit per byte lane. it is alaso asserted for the whole transfer.

The PSTRB signal is active high and is used for write-operations only. During read operations, the PSTRB signal is ignored by the bus slave, and the whole 32-bit word is read.

3.6.4 Data values on APB

Most APB systems are 32-bit. Since the bus Protocol does not include transfer size, all transfers are assumed to be the maximu size(i.e.,32-bit) excep when PSTRB signals are used during write operations: even sometimes only a small part of the data bus is actually used(e.g.,when accessing a peripheral with 8-bit data port). The transfer address should also be aligned to word size boundaries)

during write transfers, an APB slave can sample and register the write data at any cycle within the transfer. it is common for APB slaves to sample the write data at the last cycle of the transfer.

-> 언제 write data 를 가져올지 정할수 있다.?

especially in APB devices for AMBA 2. However, it is also perfectly acceptable to sample the write dta at the first cycle of the write transfer becuase the APB master must provide valid write data to APB slaves in even in the first clock cycle.

->

요약하면, APB 슬레이브가 쓰기 데이터를 마지막 클럭 사이클에서 샘플링하는 것이 일반적입니다. 그러나 APB 마스터가 첫 번째 클럭 사이클부터 유효한 데이터를 제공해야 하므로 쓰기 전송의 첫 번째 클럭 사이클에서 쓰기 데이터를 샘플링하는 것도 완벽히 수용 가능합니다.

For read transfer, the APB master should only read the return read data value at the last cycle or (when PREADY is 1). if an APB slave returns an error response, the bus master should discard the read data.

3.6.5 Mixing different versions of APB components