Verilog

1.Verilog (Gate, Adder)

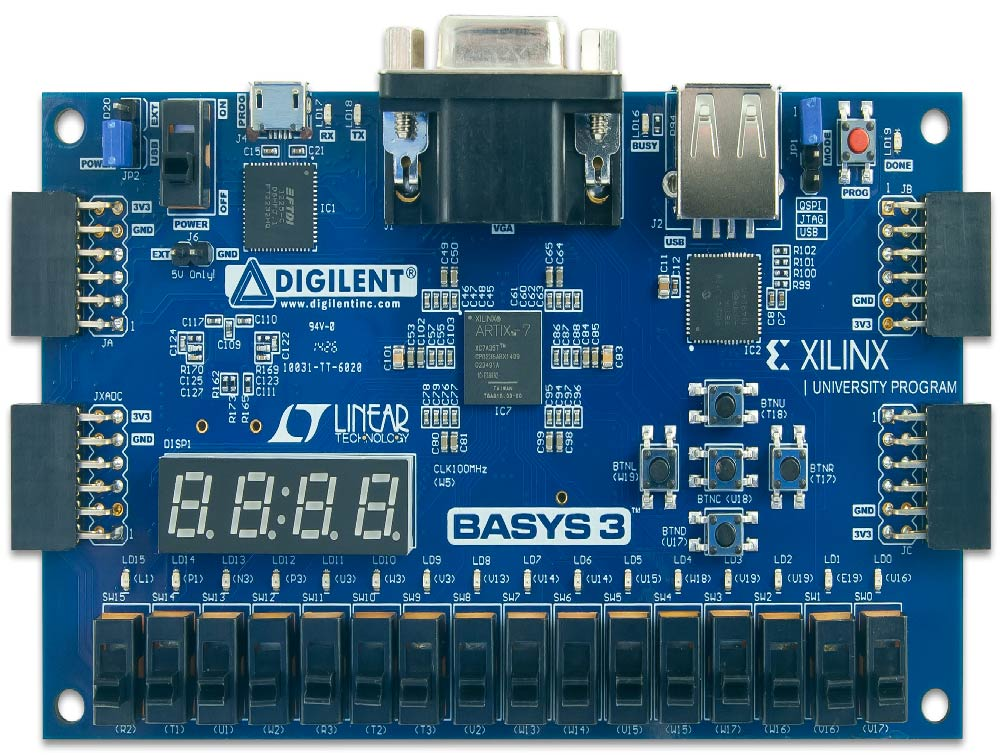

학습 및 개발을 진행하는 FPGA보드는 DIGILENT의 Basys3를 사용한다.Basys 3는 Xilinx의 ARTIX-7시리즈의 파트넘버 XC7A35T1CPG236C의 FPGA칩을 사용하고있다.Xilinx의 Vivado로 FPGA개발을 진행할 것이다.logic ga

2024년 5월 8일

2.Verilog (8bit Adder, FND display)

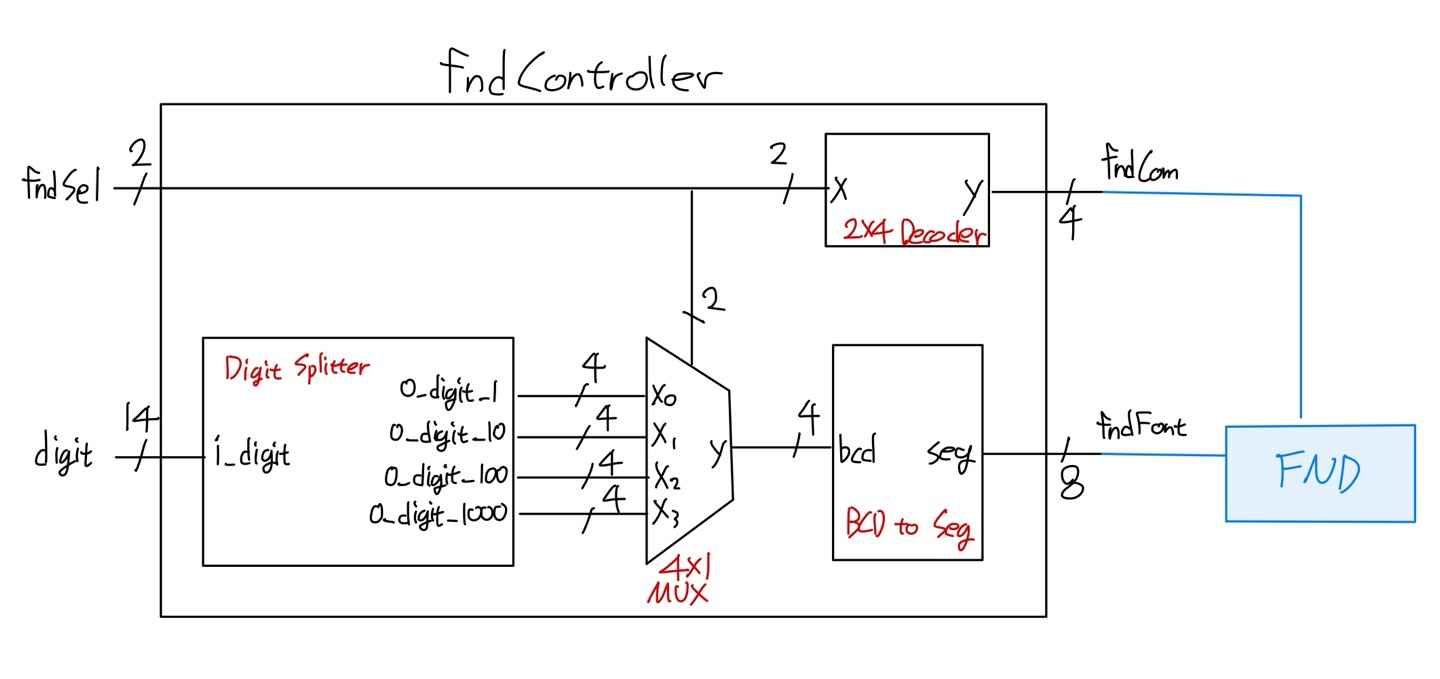

기존에 설계한 4bit Adder로 구조적모델링을 통해 8bit Adder를 설계한다. Adder 결과를 FND에 Display하기 위해서는 Adder출력을 FND에 맞게 변형하여 출력해야한다.FND는 LED로 숫자 혹은 문자를 표시하며 7-Segment라고도 부른다.

2024년 5월 11일

3.Verilog (Counter, Blocking/Non-Blocking)

4digit FND를 이용해 0부터 9999까지 Count하는 Counter를 설계할것이다.0.1초 간격 Count초기화 버튼always문으로 reset의 rising edge를 감시하면서 rising edge가 감지되면 count를 초기화한다.clk divider와

2024년 5월 12일

4.Verilog (LED On/Off, Counter)

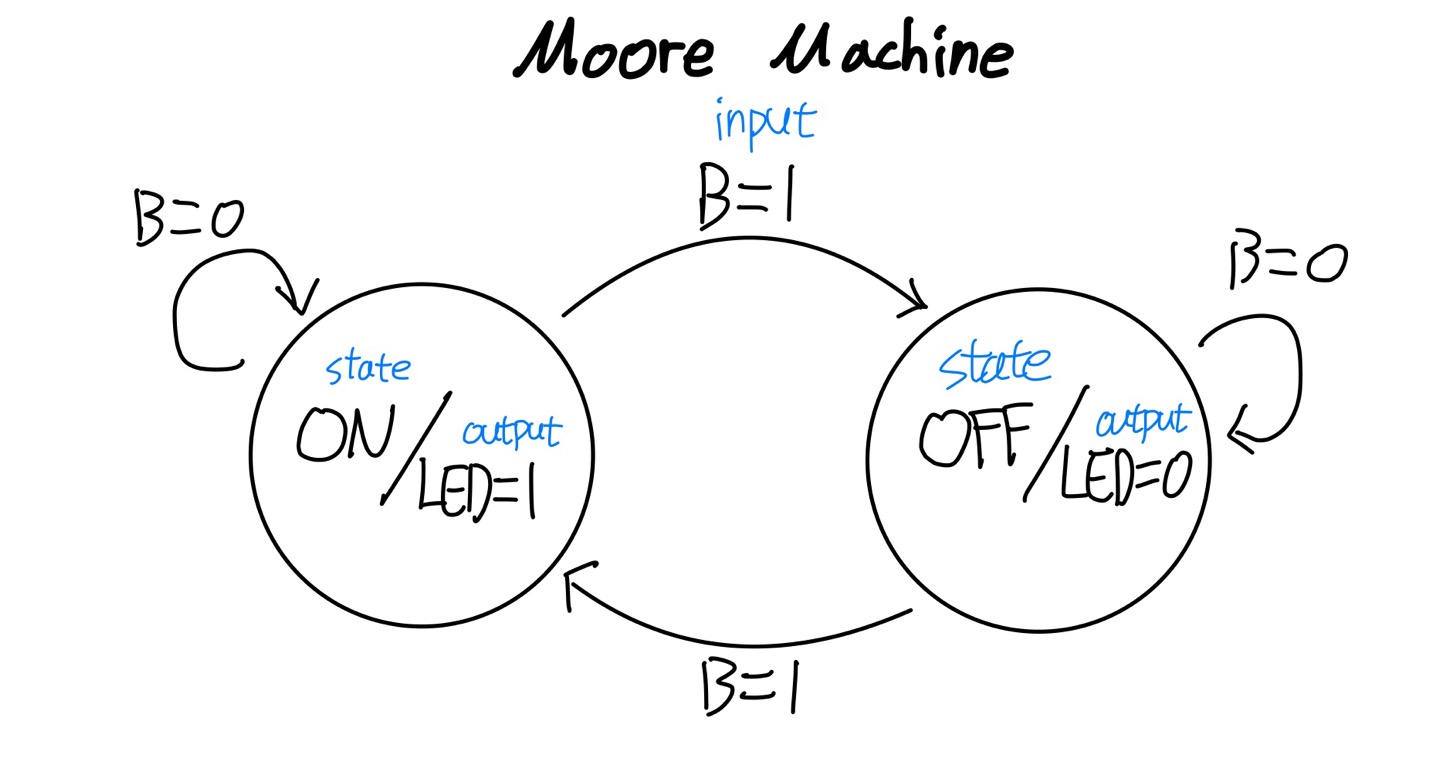

LED의 On/Off동작을 FSM을 이용해 코딩한다.

2024년 5월 15일

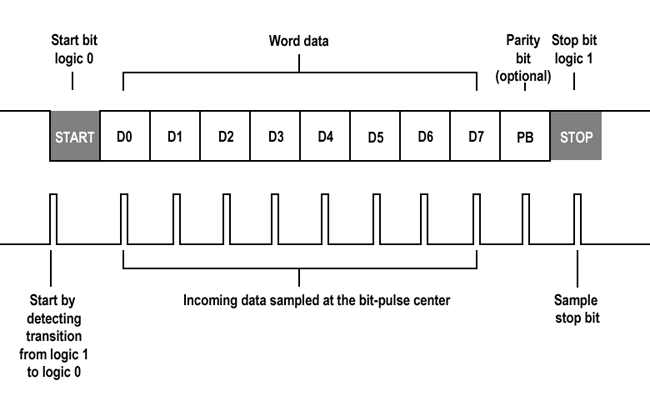

5.Verilog (UART)

UART(Universal asynchronous receiver/transmitter)는 병렬데이터를 직렬로 전환하여 전송하는 하드웨어다.

2024년 5월 18일

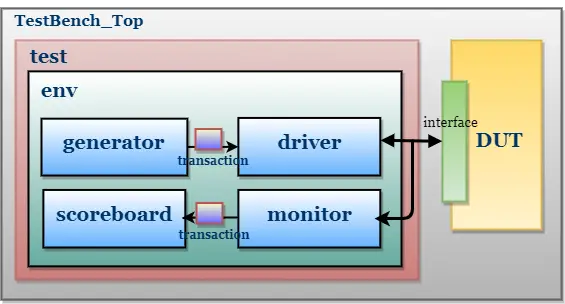

6.System Verilog(Testbench, Adder, Register, RAM)

System Verilog Testbench 구조test, env, generator, driver, scoreboard, monitor각각은 classinterface는 H/W신호들의 묶음을 나타낸다.System Verilog는 class개념을 지원한다.generat

2024년 5월 21일

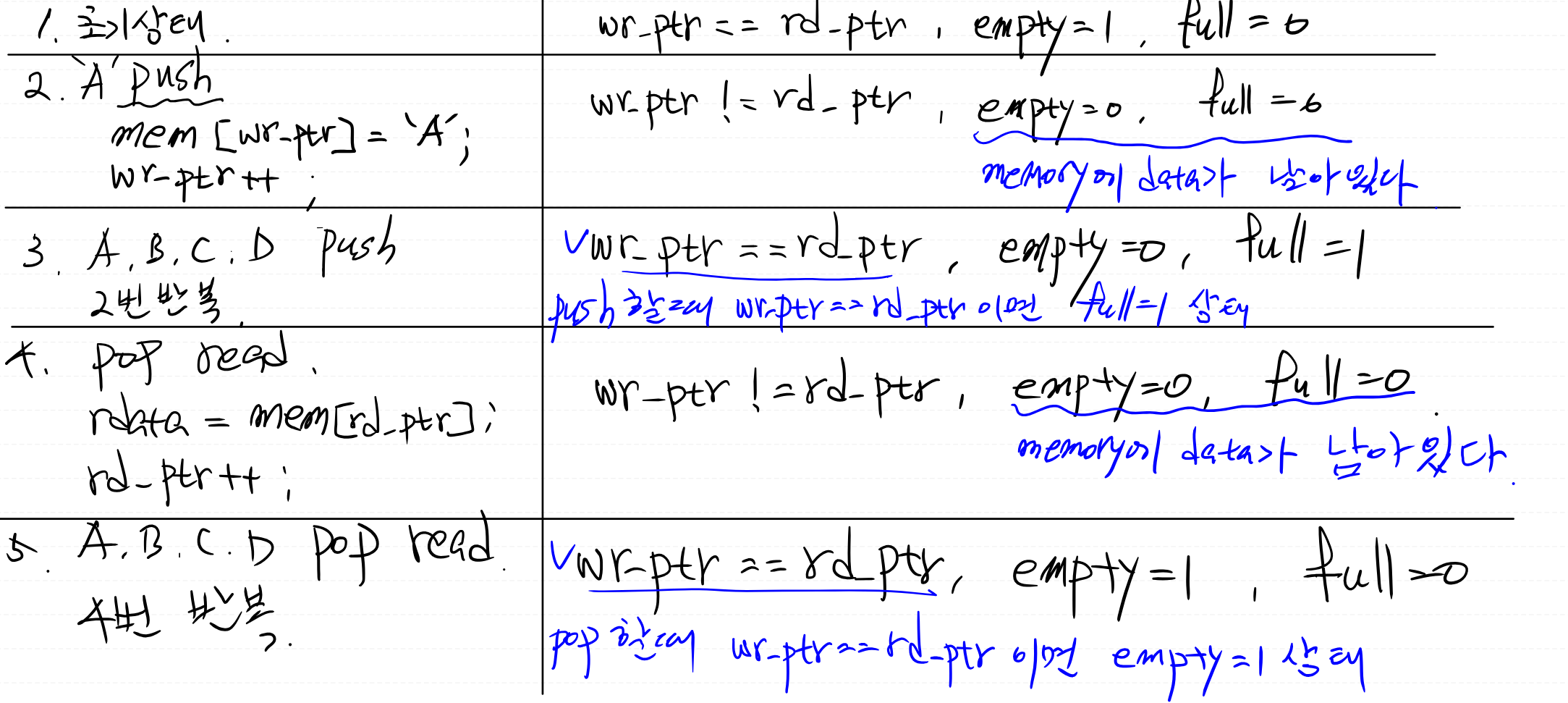

7.System Verilog(FIFO)

2024년 5월 23일

8.RTL 시스템반도체-Project

![](https:

2024년 6월 17일