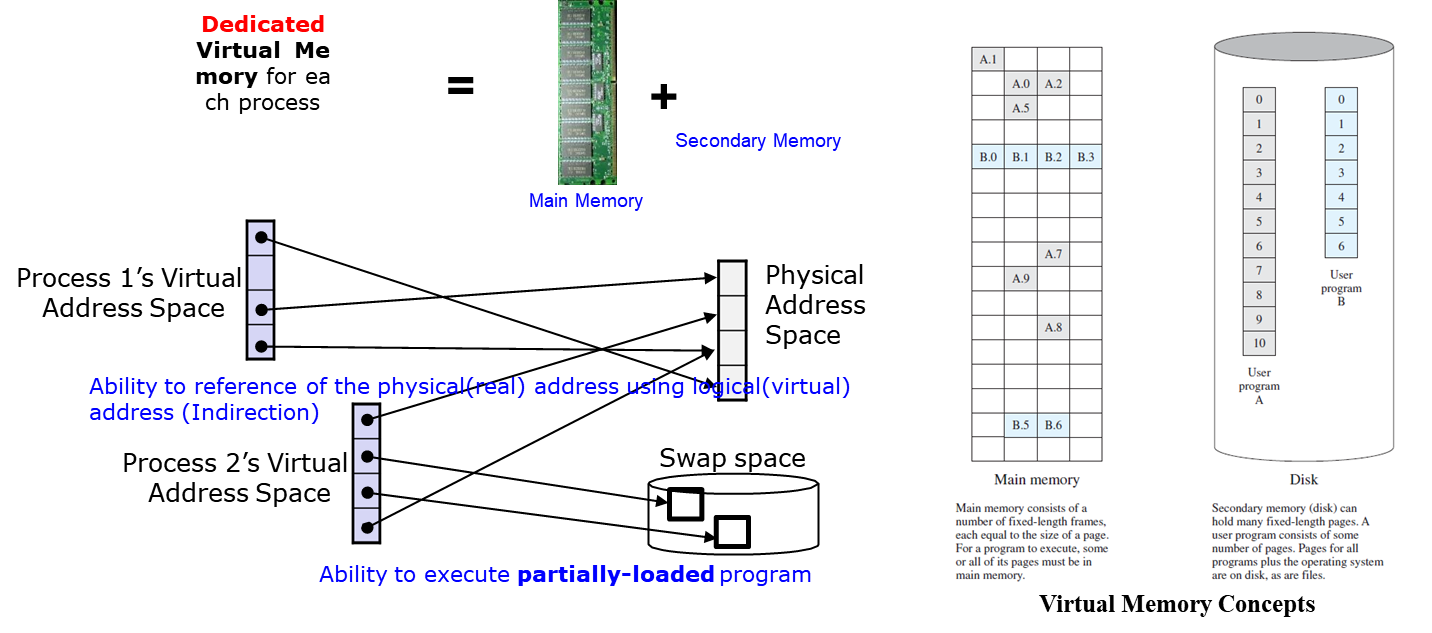

virtual memory는 프로세스를 실행하기 위해 필요한 부분만 발췌해 메모리에 할당하는 방법이다.

프로세스를 전체 할당했을 때보다 더 많은 프로세스를 할당하여 실행할 수 있음로 secondary memory를 main memory의 일부처럼 여겨지는 느낌을 받을 수 있다.

virtual memory는 분산 적재 + 부분 적재 전략을 이용한다.

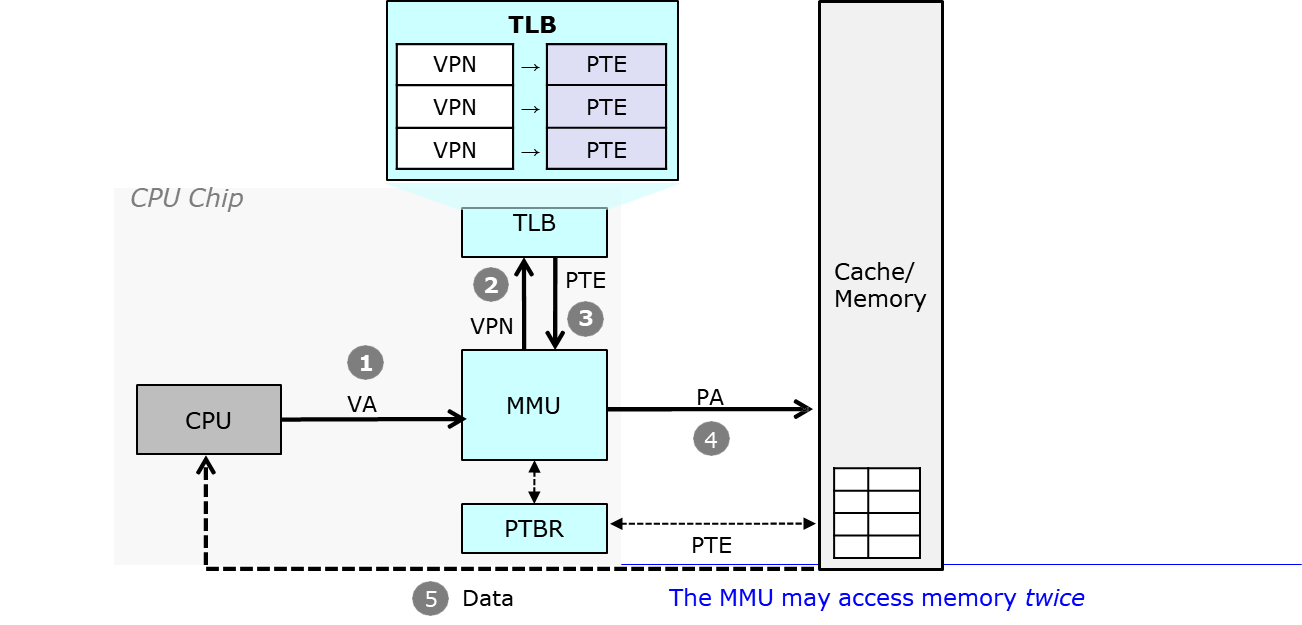

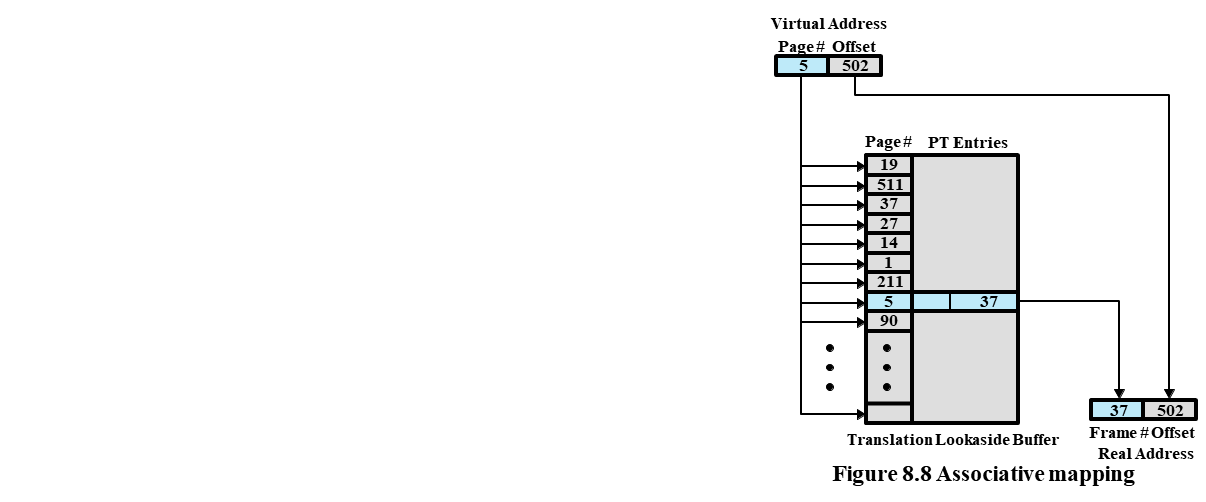

그리고 조각에 대한 위치 정보를 알기 위해 page table을 저장하는 TLB 하드웨어 캐시가 필요하다.

(테이블에 접근하기 위해 메모리에 또 접근하면 비효율적이다.)

위의 이미지에서 보면 분산 적재와 부분 적재 부분을 확인할 수 있다.

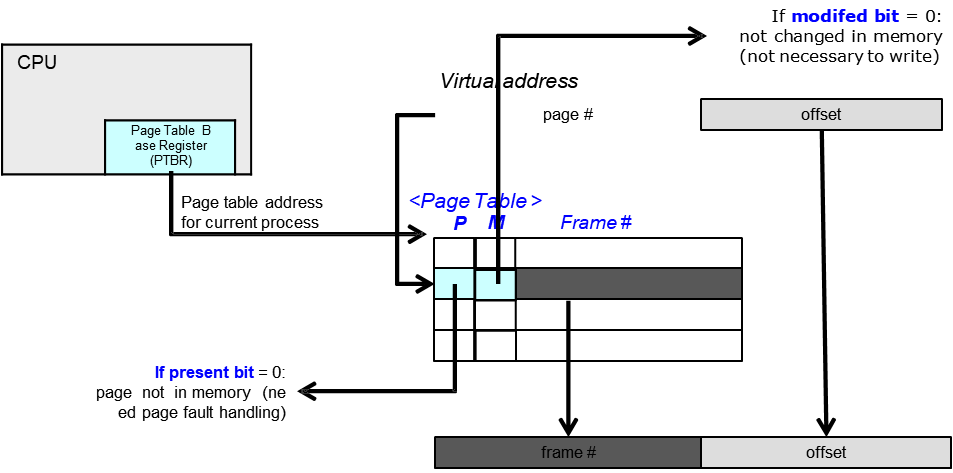

이를 위한 page table은 가상 주소에 매핑된 실제 주소 정보를 가지고 있으며 이 매핑 정보가 굉장히 커지는데, 이 문제를 어떻게 해결하는지 확인한다.

Benefits

가상 메모리의 장점은 다음과 같다.

- 더 많은 프로세스가 메모리에 할당될 수 있다.

각 프로세스는 메모리 공간을 적게 쓰고 많은 프로세스들이 병렬적으로 수행될 수 있다.- 실제 메모리보다 더 큰 프로세스를 실행할 수 있다. 그럼 가상 메모리 공간이 실제 메모리 공간보다 더 커진다.

애를 하나의 프로세스가 다 사용하는 illusion을 제공한다.- 가상 메모리를 통해 페이지를 보호할 수 있다.

페이지 번호는 프로세스마다 같아도 frame 번호는 다르기 때문에 프로그래머의 시각과 시스템의 시각은 다르다. 프레임 번호가 다르기 때문에 다른 프로세스로부터 보호할 수 있다(어느 프레임에 할당될지 모름). 또한 protection bit으로 다른 프로세스의 접근을 막을 수 있고 offset을 통해 page size를 넘어가면 예외처리를 할 수 있다. 이러한 방식으로 페이지를 보호할 수 있다.- 동적 라이브러를 페이지로 처리해서 다른 프로세스들과 공유할 수 있다.

- 부분적재로 사용되지 않는 page들을 할당하지 않기 때문에 불필요한 I/O를 줄일 수 있다.

Hardware support for VM

가상 메모리를 위한 하드웨어적 서포트를 알아보자.

- Page Table Base Register: 메모리에 존재하는 page table의 주소를 저장한다.

Page Table Length Register도 존재할 수 있다.- Page table entry: Present(Valid) bit: 페이지가 메모리에 있음을 표현하는 bit이다.

- Modified(Dirty) bit: 페이지가 수정됨을 알리는 bit이다.

- reference bit 등 다른 bit들도 존재한다.

page table은 프로세스마다 가지고 있는 자료구조이다.

page table의 크기는 얼마나 클 수 있을까?

32-bit 환경에서 page의 크기가 2^12 bytes라면 2^20 개의 entry가 존재할 수 있다.

그럼 테이블의 크기는 entry당 4byte를 저장하면 4 * 2^20가 되며 이는 4MB가 된다.

당연히 메인 메모리에 존재할 수 밖에 없다.

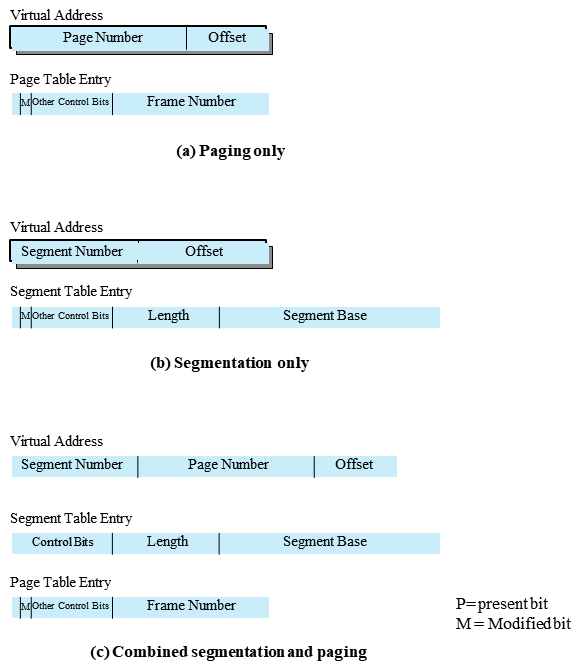

Segmentation은 call, stack과 같은 모듈 단위로 쪼개기 때문에 특정 조각의 protection과 sharing이 효율적이다. 그러나 외부 단편화가 발생할 수 있다.

paging은 마지막 page에 대한 내부 단편화가 발생할 수 있다. 그러나 외부 단편화는 발생하지 않는다.

이 두 개를 합친 방법은 테이블의 크기를 줄이기 위함이다.

TLB

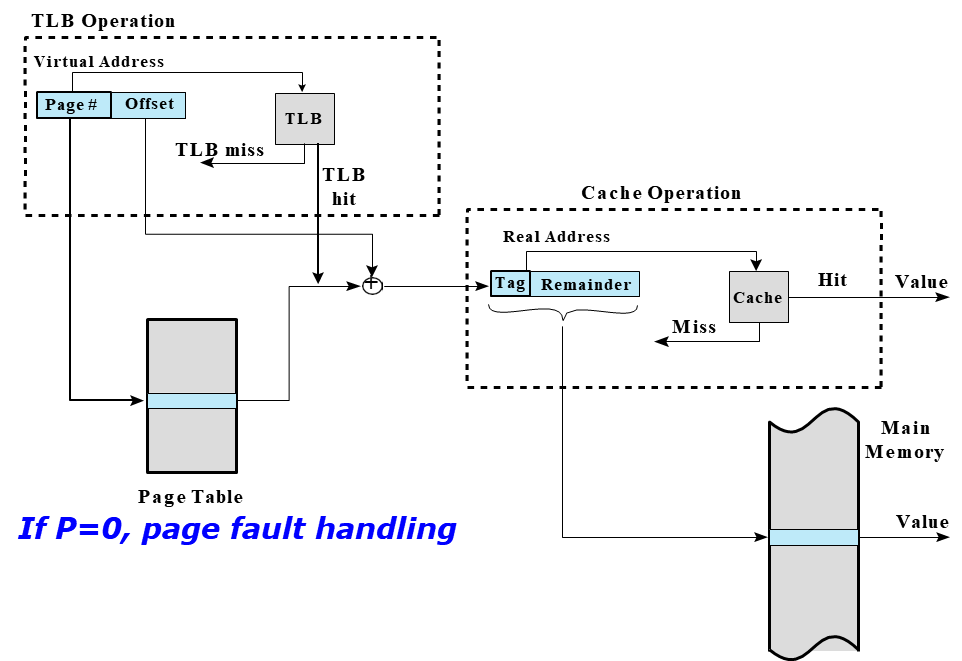

TLB는 page table entry를 저장하는 cache이다. 메모리에 존재하는 page table에서 entry를 찾기 이전에 TLB부터 scan한다.

여기에 존재하면 present bit을 확인할 필요가 없다.

만약 TLB에 존재하지 않는다면, table 접근, 실제 데이터 접근 총 두 번의 메모리 접근이 발생한다.

fully associative cache를 사용한 TLB는 page 번호만 알고 있다면 빠르게 cache에 접근할 수 있다. 추가적인 하드웨어(비교기)로 동시에 비교할 수 있다.

위와 같이 fully associative 방식으로 hit되면 frame 번호를 반환하고 아니면 page table을 참조해야한다.

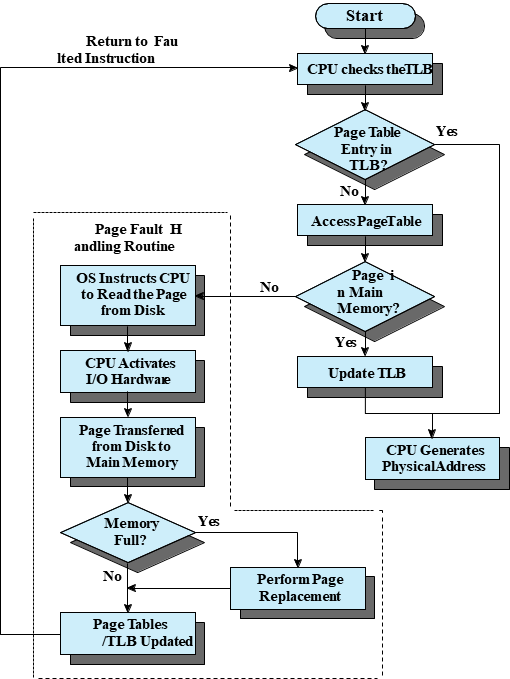

만약 table에서 present bit이 0이면 page fault까지 발생한다.

process switch 발생시 miss 오버헤드가 상당히 크다.

page fault가 발생하면 DMA에게 I/O 연산을 요청한다.

위의 과정에서 PTBR이 사용된다.