Vivado

Visual Studio Code로 Vivado Code 수정 설정 (+ Linter)

- 설정 순서 : Xvlog 환경변수 설정 - VSCode 설치 - VSCode Extencsion 설치 - Vivado TextEditor 설정

- Linter는 코드 작성 시 실수를 줄이고, 팀 내에서 일관성 있는 코드 스타일을 유지하는 데 매우 유용한 도구

1. Xvlog

Xvlog는 Vivado 설치하면 같이 설치되기에 따로 설치할 필요 X

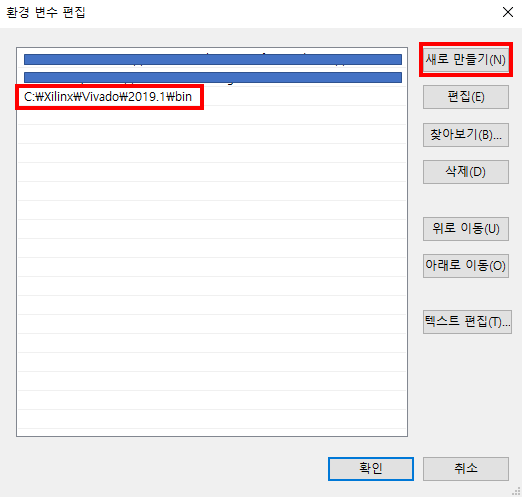

: 주로 설치된 경로 C:\Xilinx\Vivado\Vivado 설치 버전\bin

- 설치경로 복사하기 : C:\Xilinx\Vivado\2023.1\bin

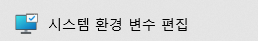

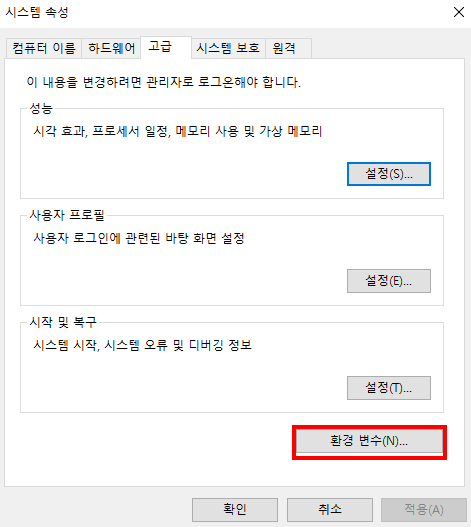

- Windows '시스템 환경 변수 편집' 들어가기

- 명령 프롬프트/powershell 관리자 권한X 로 xvlog -version입력시 제대로된 버전이 나오면 성공

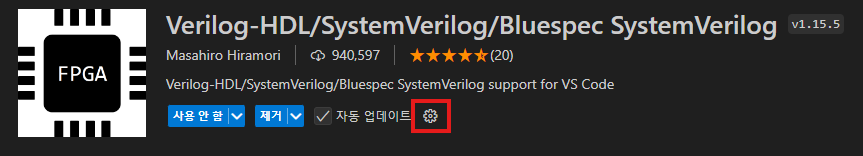

2. VS Code 설치, Verilog-HDL/SystemVerilog/Bluespec SystemVerilog 설치

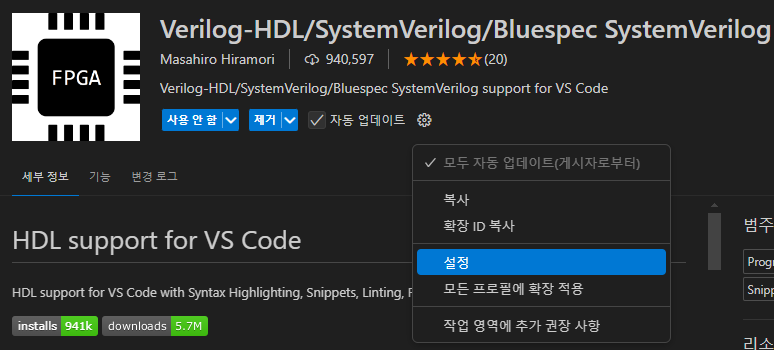

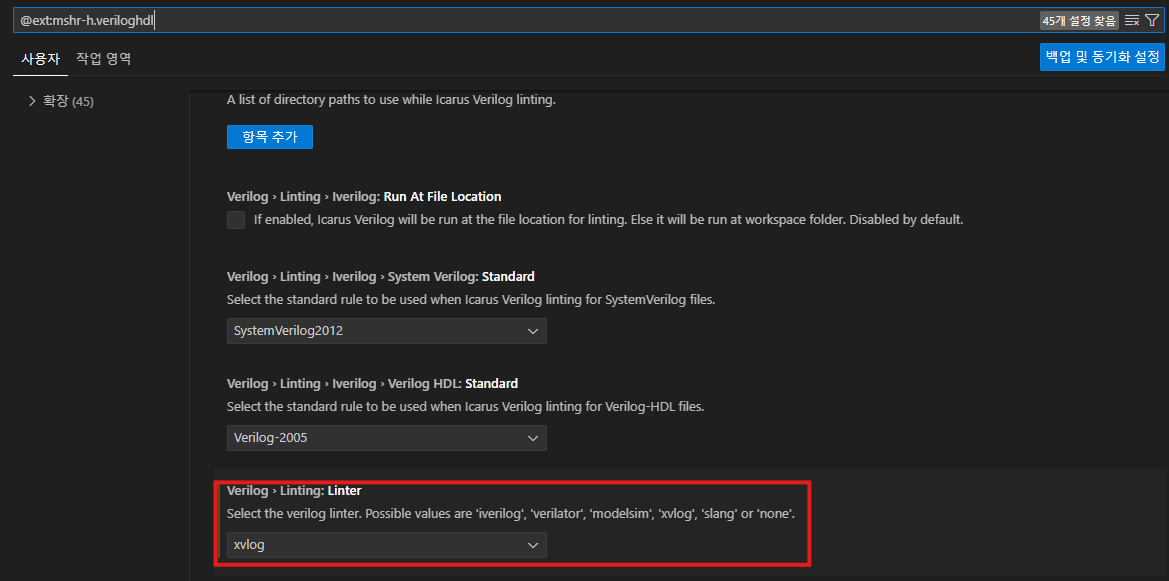

- 설치 후 빨간 네모 설정칸 클릭

- 여기까지 완료하면 VS Code 설정 성공

- VS Code 종료후 다시 키기

3. Vivado 설정

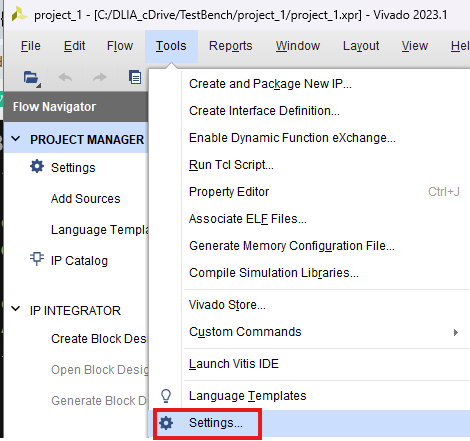

- Tools 클릭 후 Setting

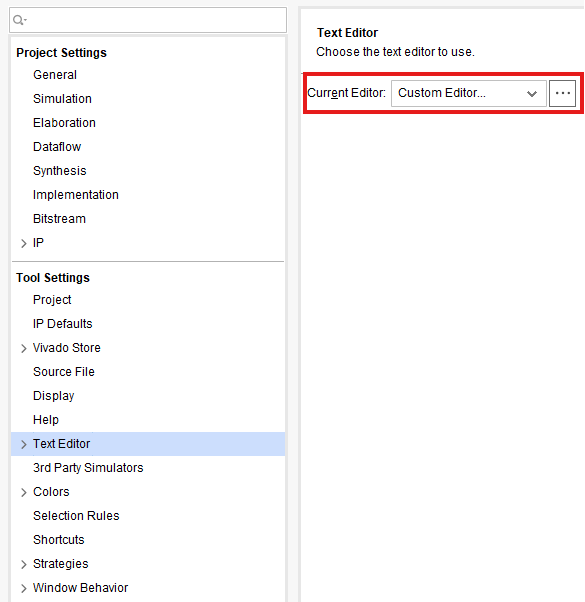

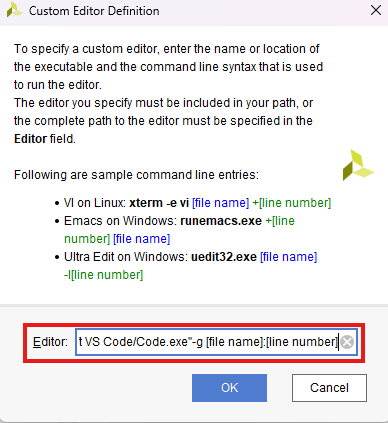

- Text Editor - Current Editor - Custom Editor 클릭

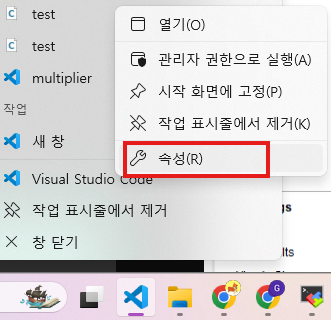

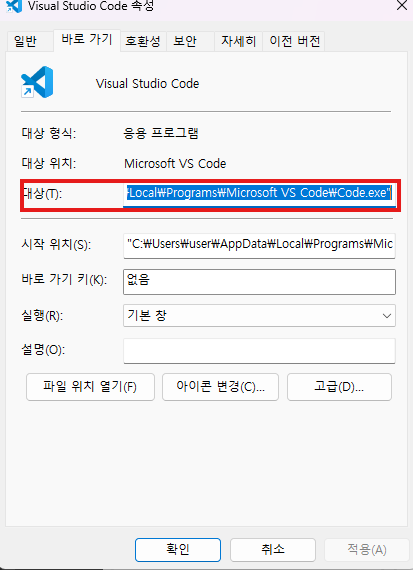

- VS CODE 대상 위치 복사

- 복사한 경로 + -g [file name]:[line number] 붙여 넣기

"VS Code 대상 주소" -g [file name]:[line number]Linux

.c 파일 실행 (c 코드) / Makefile

<Makefile 코드>

# the compiler: gcc for C program, define as g++ for C++

CC = g++

# compiler flags:

# -g adds debugging information to the executable file

# -Wall turns on most, but not all, compiler warnings

CFLAGS = -g -Wall

# the build target executable:

TARGET = test (타켓 파일명!)

all: $(TARGET)

$(TARGET): $(TARGET).c

$(CC) $(CFLAGS) -o $(TARGET) $(TARGET).c

clean:

$(RM) $(TARGET) *.txtMakefile은 C 코드를 컴파일하고 실행 파일을 생성할 때 컴파일 과정을 자동화하는 데 사용됩니다. 여러 소스 파일이 있거나 특정 빌드 옵션을 설정할 때, 매번 복잡한 컴파일 명령어를 입력하지 않고 make 명령어 한 번으로 필요한 작업을 수행할 수 있게 해줍니다.

구조

wavedrom.com / Timing Diagram 그리기

Timing Diagram 그리기

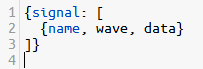

기본적인 틀은 아래 사진과 같다.

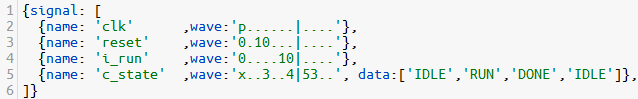

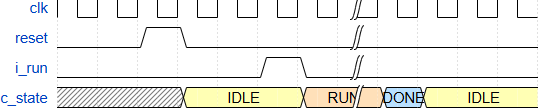

. : 이전값 유지

p : positive edge , n : negative edge

| : 시간이 지났음을 표현 (물결)

이같이 나타낼 수 있다.(FSM)

FSM, Finite State Machine

FSM은 현재 상태를 정확하게 명시하고 입력에 의해서 동작을 시키도록 기술되기 때문에, Control 로직을 설계할 때 용이하게 사용할 수 있다. : 하나의 FSM 로직은 하나의 상태(State) 만을 가지게 되고, 어떠한 사건 EVENT에 의해 현 상태에서 다른 상태로 변화할 수 있으며 이를 Transition(전이)라고 한다. [ IDLE - RUN - DONE ]

++ Moore/ Mealy Machine

Test Bench / DUT(Design Under Test)

TestBench는 DUT의 검증을 위해 사용된다.

(주의) 테스트 벤치는 하드웨어 모듈이 아니다. 테스트 벤치가 실제로 FPGA나 ASIC 같은 하드웨어로 구현되지 않는 소프트웨어적 구성 요소임을 뜻하는데, 테스트 벤치는 하드웨어 설계 자체를 검증하는 시뮬레이션 환경이기 때문에, 설계의 일부로서 하드웨어에 직접 포함되지 않는다.

BRAM-FPGA / SRAM-ASIC

메모리의 20번째 Address에 Data를 쓰고싶어 or 메모리의 0번째 Address에 있는 Data를 읽고 싶어!BRAM

-

Single Port RAM(SPRAM)

: 메모리를 READ / WRITE 하기위한 PORT가 하나이다.(1Cycle에 메모리에 접근해서 할 수 있는 동작인 READ OR WRITE/ 동시에 불가) -

Dual Port RAM

: 1Cycle에 Read/Write 동작이 가능하다.

[Read] Address 0번지의 Data를 read하고 싶어 : en=1, we=0, address=0 으로 설정하면 dout에 Read Data가 올라온다.

[Write] Address 2번에 Write 하고 싶어 : en=1, we=1, address=2로 설정 후 din에 write하고 싶은 data를 만들어 준다.

1. 메모리 / 데이터 비트

parameter DWIDTH = 16;

parameter AWIDTH = 9;

parameter MEM_SIZE = 512;

512개의 16비트 메모리 셀을 가지게 되며 메모리의 전체 크기는 512×16비트가 됩니다.MEM_SIZE

: 주소 비트 폭(AWIDTH)에 따라 결정되며, AWIDTH가 9일 경우 2^9 = 512개의 메모리 셀을 사용할 수 있습니다.

DWIDTH

: 데이터의 비트 폭을 결정하는 역할을 하며, 메모리의 용량(셀의 개수)**에는 영향을 주지 않습니다. 대신, DWIDTH는 각 메모리 셀에 저장되는 데이터의 크기를 정의합니다.

2. reg / wire

reg , 동기적 로직( ex: always @(posedge clk) )에서 사용하는 변수

: 클럭 신호에 동기화된 값을 저장하거나 always 블록 내에서 값이 갱신될 때 사용됩니다.(주기적으로 값을 기억하고 필요한 순간에만 값이 갱신)

wire

: 조합 논리에서 사용하는 변수로, 즉시 계산된 값을 출력 항상 다른 신호나 배선의 값에 의해 설정되며, 클럭이나 다른 신호에 의해 동기화X always 블록 안에서 값을 할당할 수 없습니다.

주석 처리

여러줄 주석처리 : 주석 처리 할 문장 드래그 + Ctrl + /

여러줄 주석처리 해제 : 주석 처리된 문장 그래그 + Ctrl(누른 상태 계속유지) + K 누른 후 U

자주 사용하는 Flow

- 시간 단위와 시간 정밀도 정의

`timescale <시간 단위> / <시간 정밀도>

ex) timescale 1 ns / 1 ps

1 ns: 시뮬레이션의 기본 시간 단위가 **1 나노초(ns)**로 설정됩니다. 즉, 시간 지연이나 대기 시간(# 지연) 등의 모든 시간 단위가 1 나노초 단위로 해석

1 ps: 시간 정밀도가 **1 피코초(ps)**로 설정됩니다. 시뮬레이션에서 시간 계산의 최소 단위가 1 피코초 단위로 설정되므로, 모든 시간 값은 1 피코초 단위로 표현2.' module ' 기능적 하드웨어 블록을 정의하고, 입출력 포트를 통해 다른 블록과 연결되며, 재사용성과 계층화