디지털 시스템 설계

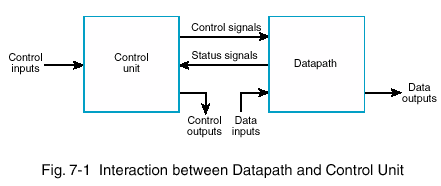

디지털 시스템의 구성

- data path 모듈: 데이터 처리, 레지스터, 연산기, MUX, …

- control unit 모듈: 제어신호 발생, 연산의 순서지정

RTL(Register Transfer Level) operation

- reg 데이터 이동/처리

- reg set, operation, sequence control

micro-operation (uo)

- reg에 저장된 데이터에 대한 기본연산 단위

- 보통 1 클럭 동안에 수행

레지스터 전송(RT) 연산

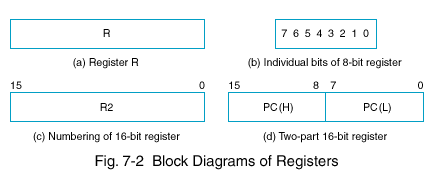

레지스터 표기 : 기능을 상징하는 대문자

- AR : address register

- PC : program counter(program: 메모리 주소)

- IR : instruction reg

- R2 : 2번 reg, …

8비트 reg

- R1(7:0) : little endian, LSB가 오른쪽에서 끝남

- R1(0:7) : big endian

레지스터 전송

- R2 <- R1 R1을 R2에 복사, R1 불변

- R1 : source reg R2 : destination reg

- 하드웨어 : R1 출력이 R2 입력으로 가는 경로와 병렬load 기능을 가진 R2

enable 신호를 가진 이동

- if (K1=1) then (R2 <-R1) : K1 : R2 <-R1

- K1이 클럭에 동기되어 t 시간의 클럭 에지에서 1이 되고 t+1의 에지에서 0

- R2는 t+1의 에지에서 K1이 1이 되어 있어 R1 load <- F/F의 setup/hold time이 있기 때문이다.

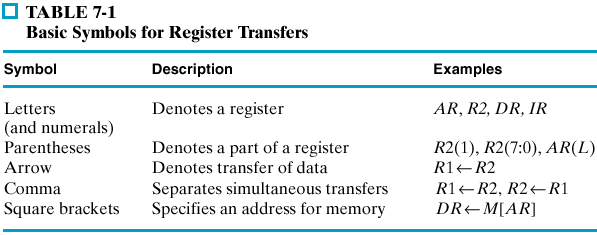

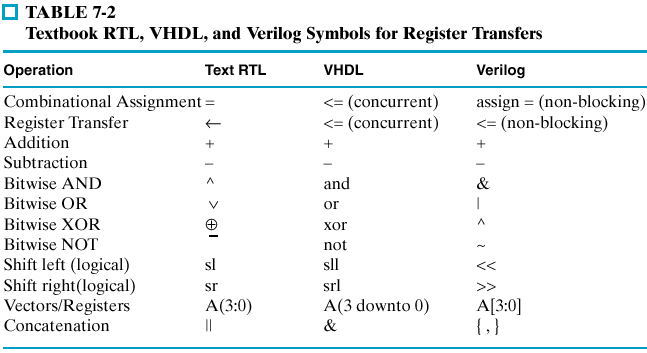

레지스터 전송 기호 표기법

여러 가지 RTL 표시방식

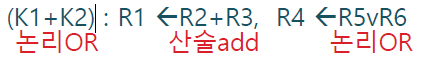

Micro 연산

- micro가 기본 단위

- 이동, 산술, 논리, 시프트

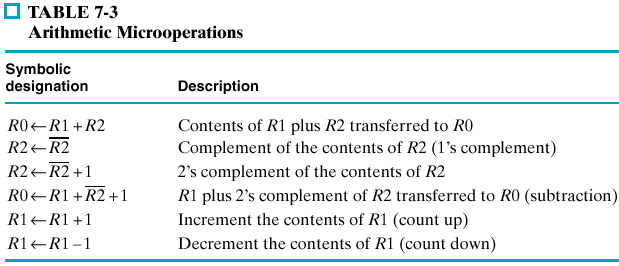

산술마이크로 연산

-

R0 <- R1 + R2 ; add and store to R0

-

1 증가/감소 회로 : 상승-하강 카운터 또는 가산기/감산기

-

곱셈/나눗셈 : 기본 마이크로 연산이 아닌 결합된 uo로 구현 <- 작은 하드웨어, 느린 연산인 1 uo로 구현 <- 큰 하드웨어 규모, 빠른 동작

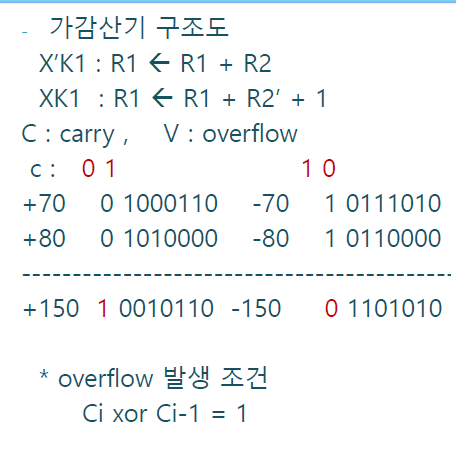

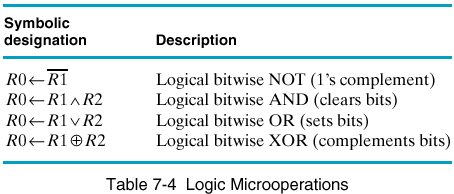

산술마이크로 연산 하드웨어

- 가감산기 구조도

- :앞에 있는 값은 연상을 하기위한 조건

- X'은 X = 0

- K1은 K = 1

- X'K1 = (X = 0 and K = 1) = (X = 0 & K = 1)

- <-는 할당 연산자

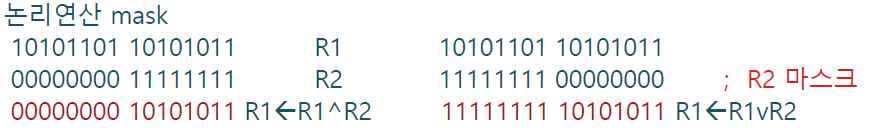

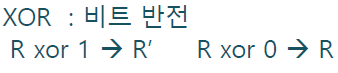

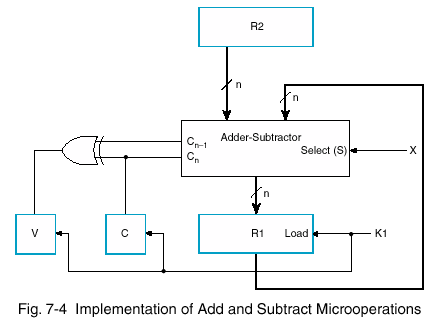

논리마이크로 연산자

종류

RT표현(레지스터 단위에서 연산을 표현)

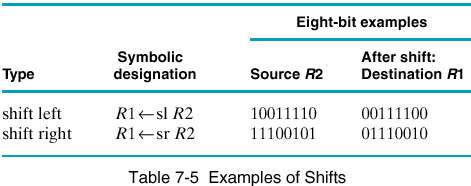

Shift 마이크로 연산

- shift 마이크로 연산 표현

R0 <- sr R0 shift right, same source and destination, change R0

R1 <- sl R2 shift left, no change R2

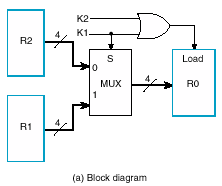

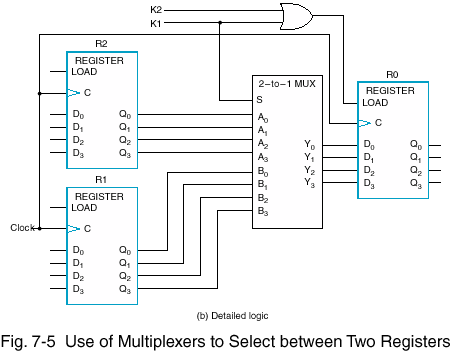

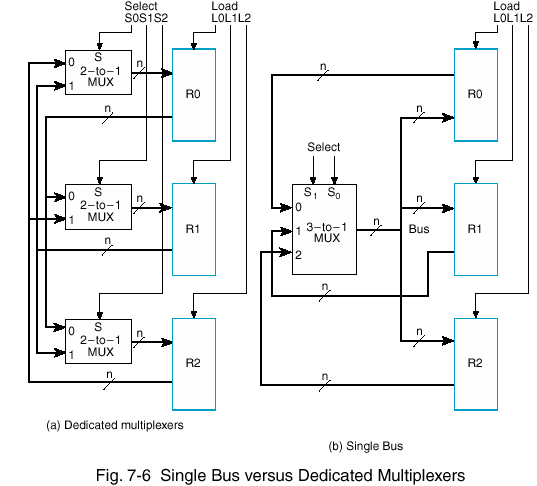

MUX를 활용한 전송 연결

- source reg가 여러 개 일 때

if (K1=1)

(R0 <-R1)

else if (K2=1)

(R0 <-R2)위와 아래는 같은 동작을 의미

K1 : R0 <-R1, K1’K2 : R0 <- R2- 2 to 1 MUX를 이용한 연결

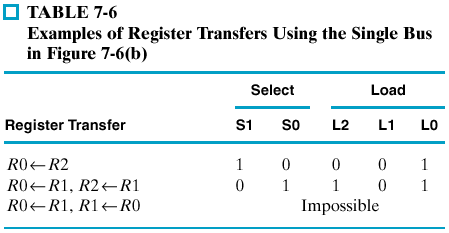

버스 방식 연결

H/W 비교

(a) 2n개 AND, n개 OR : 9n gates, 6n개 input wires

(b) 3n개 AND, n개 OR : 4n gates, 3n개 input wires

- a는 각 레지스터마다 MUX가 붙어있기 때문에 연산의 자유도가 높댜.

- But, b에 비해 Mux의 양이 많기 때문에 Resource 소모가 크디.

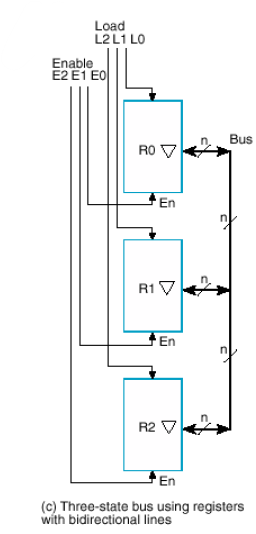

3상태 버스 사용한 연결 : wire 감소, H/W 감소

- 많은 fanin이 있는 회로에서는 이 방식 사용

R0 <- R1, R2 <- R1

E0E1E2=010

L0L1L2=101

- 위의 방식은 메모리에서 많이 사용됨

- tri state방식은 inout port를 이용한 방식과 등가적으로 사용가능

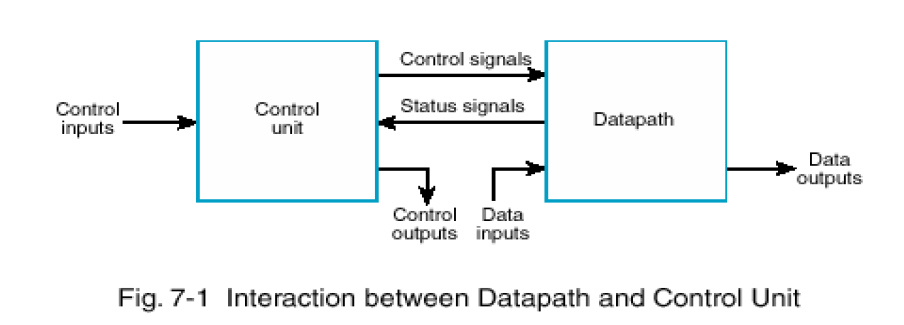

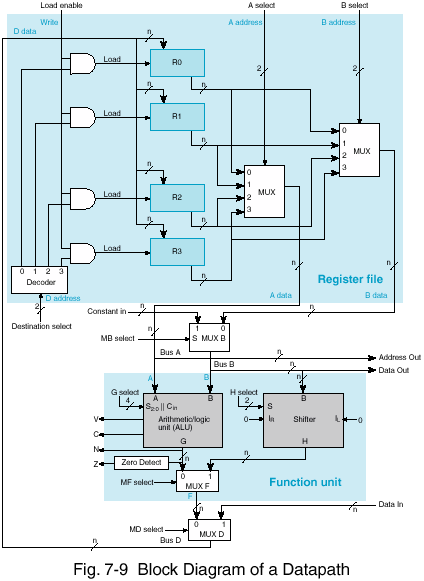

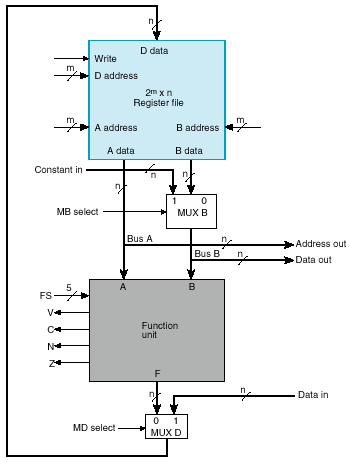

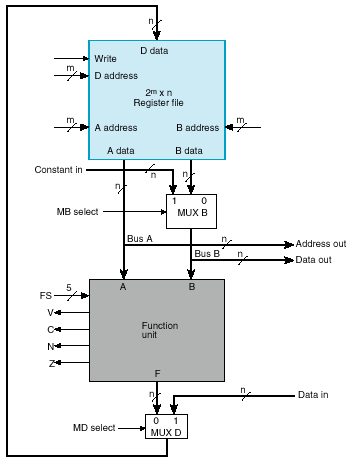

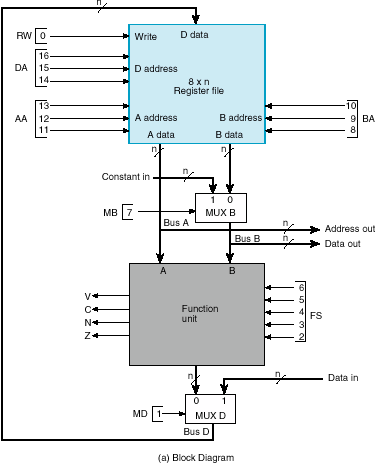

Data Path

- 위의 그림은 버스가 하나를 공유하는 siungle bus구조

- A select, B select 신호를 통해 출력을 결정하는 4:1 MUX를 통해 두개의 register를 선택

- 마이크로 연산(uo) 실행 장치 : ALU

- ALU 구성

조합연산회로와 accumulator(reg)

실행시간 : 1 uo /1ck

2 operand 입력, 1 출력 - CPU 주요 구성부

(1) 데이터패스 블록

ALU, shifter 레지스터(SR,LR,PB,PL,BS), MUX, decoder,버스 연결회로 등으로 구성

(2) 제어신호

uo을 수행하기 위한 적절한 신호발생

R1 <-R2 + R3 (2 operand)

(2) B select=11, R3 B버스, MB=0

(3) G -> A+B연산 선택

(4) MF=0, ALU 출력선택

(5) MD=0, MUX F -> D bus

(6) D select=01, R1 선택

(7) load enable=1, clock edge에서 R1에 값 저장

-> 1clk에 실행(1uo/1clk)

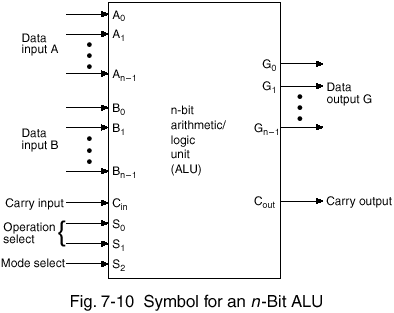

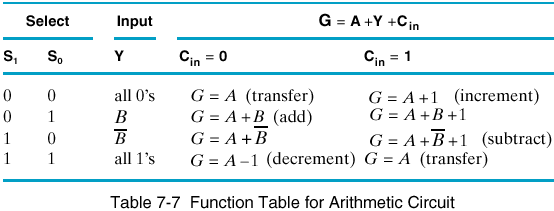

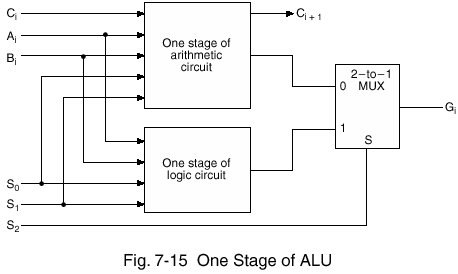

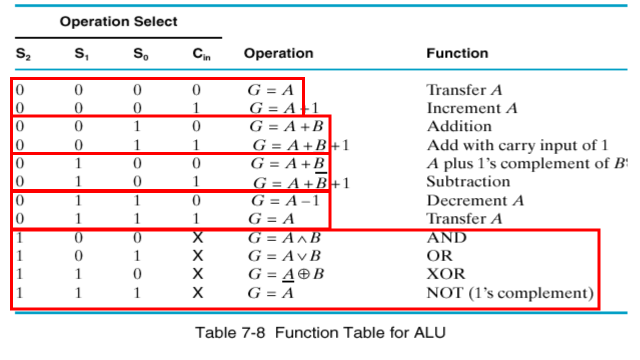

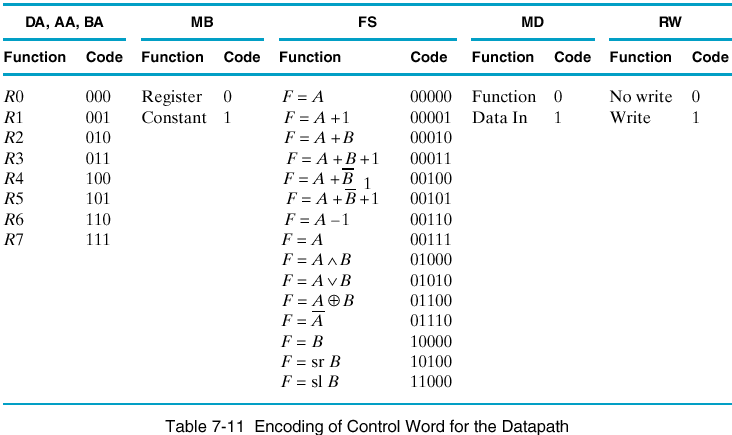

산술/논리 연산장치

ALU

- 산술/논리연산

- N 비트 입출력

- carry 입력 및 출력

연산종류 선택

- S 신호

-> S2: 산술/논리, mode select

-> S1S0 : 각 4가지 연산종류

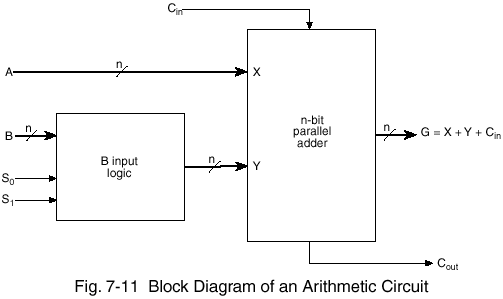

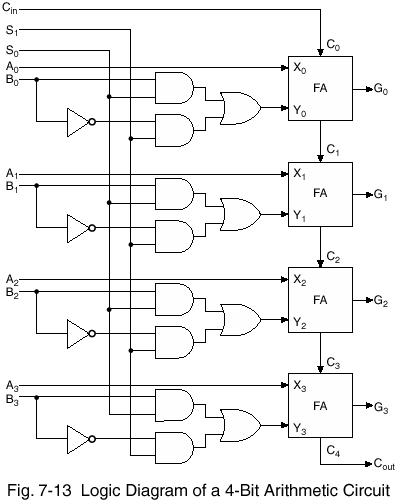

N 비트 병렬가산기이용

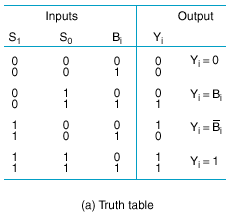

- Y 입력의 다중 선택회로

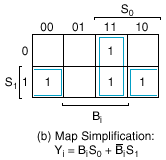

- S1S0 <- 4가지 연산 종류 설계

- 각 1비트에 대한 B 입력 논리회로

- S1S0에 대한 4 to1 MUX

-> Bi 입력과 동시 최적화 : 2 to 1 MUX

- 4비트 산술연산논리도

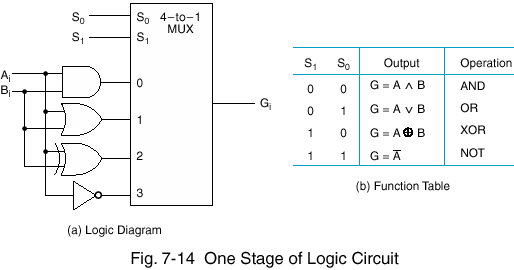

논리연산회로

- 비트별 연산

S1S0: 4개 연산 선택

-> 4 to 1 MUX

ALU : 산술 + 논리

- mode 선택: S2

- n 비트 ALU : 가산기의 ripple carry에 의한 전파 지연시간 발생

- 빠른 ALU : LAC(Look Ahead Carry) 사용

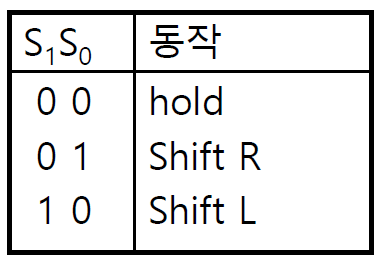

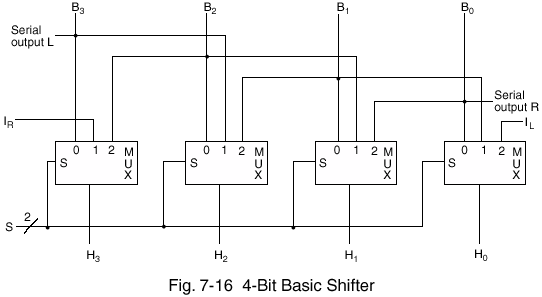

Shift 회로

- 기본 shifter회로 : sl(shift left), sr(shift right)

- Bidirectional shift reg with parallel load

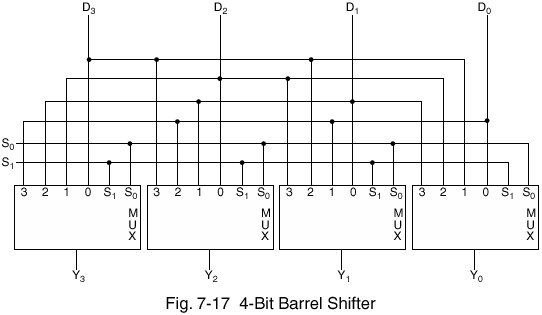

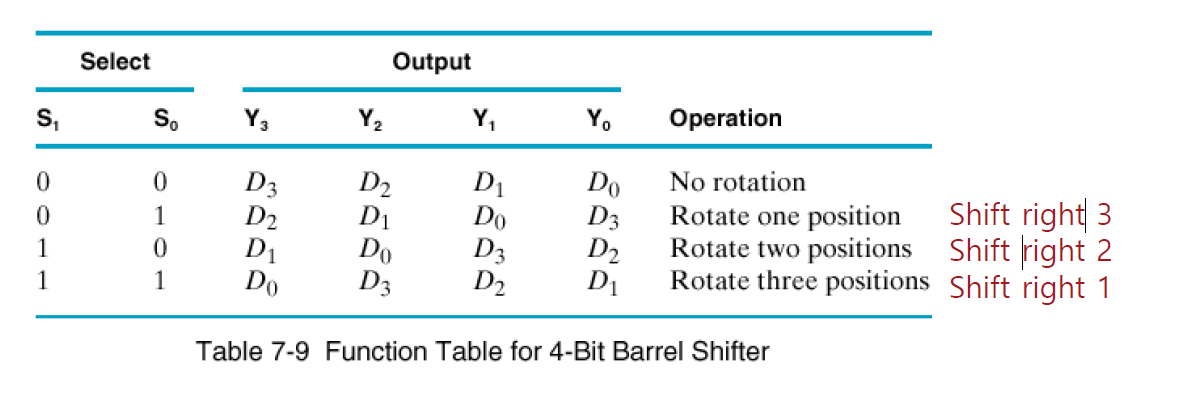

Barrel Shifter (BS)

- 한 클럭에 n비트 이동

- shift left with rotation

- 2n 비트 입출력 BS

- 2n 입력, n 선택선

- 2n 개의 MUX

- 이동수 : 0 ~ 2n -1

- RR1 = RL3

- RR2 = RL2

- RR3 = RL1

- 한 방향의 Bs로도 양쪽 방향의 shift구현이 가능하다

레지스터 파일

operand, dest. reg 독립적 R/W : addr, data, write signal

ALU + shifter + MUX : 연산 함수 및 MUX 선택 신호

status : V,C,N,Z(process status register)

- V: Overflow 검출

- C: Carry 검출

- N: 음수 검출

- Z: 0을 검출

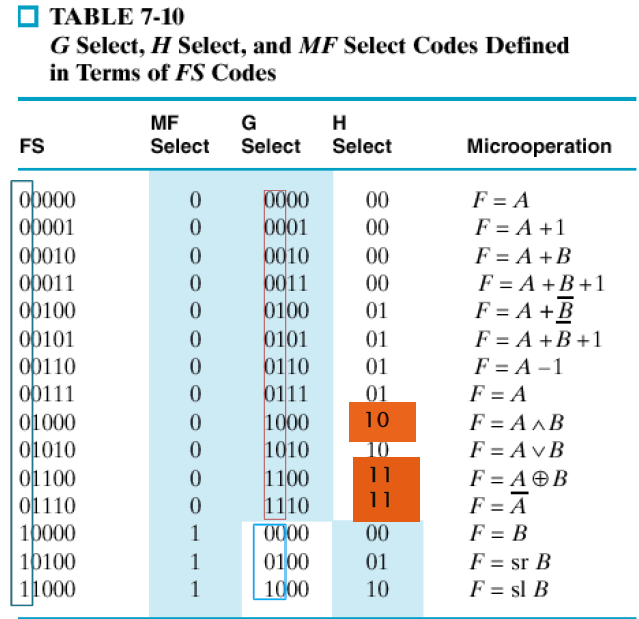

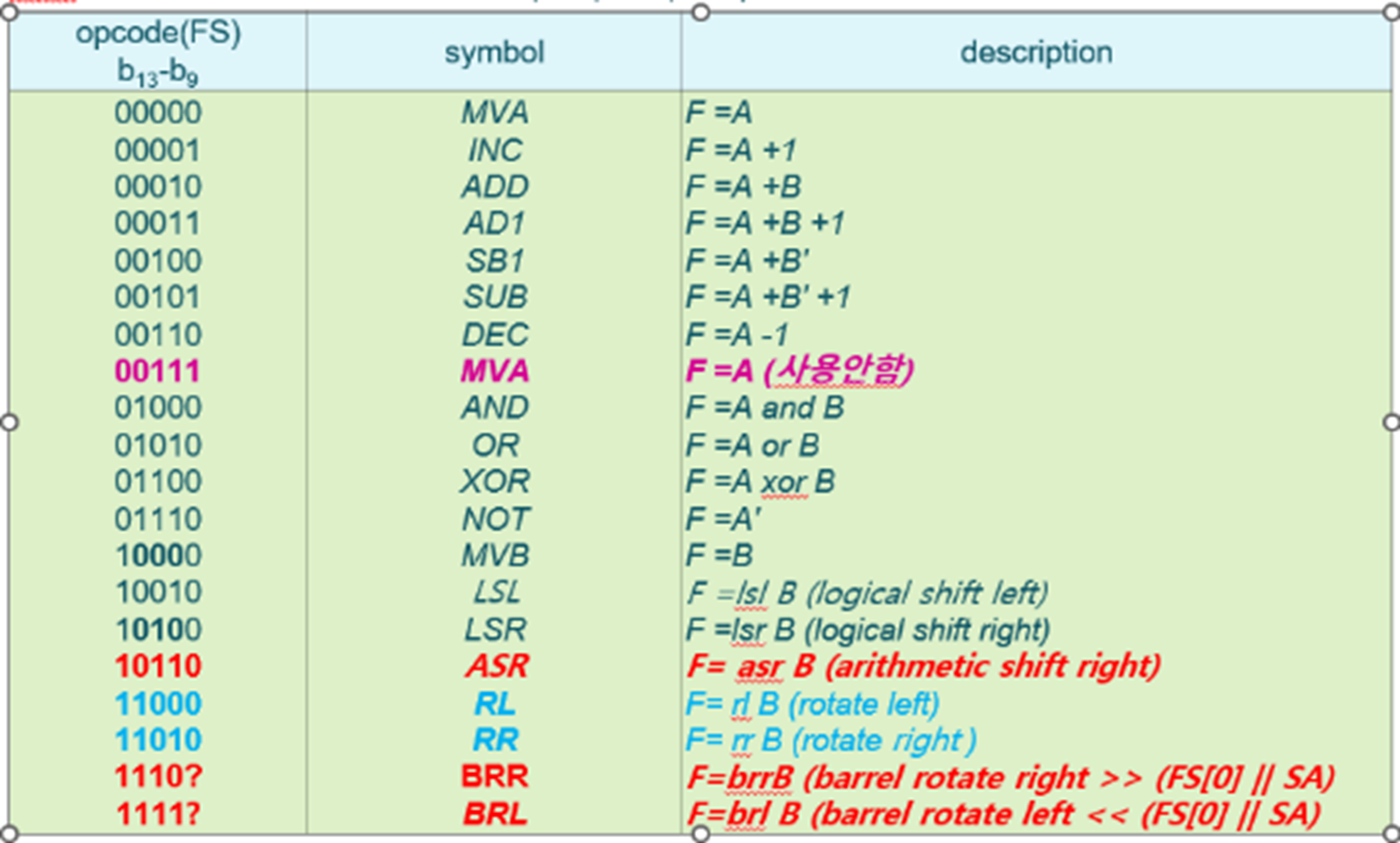

FS: ALU, Shift를 어떻게 이용할 것인지를 결정

- MS Select: Shift를 쓸건지 ALU를 쓸건지 선택

- G Select: ALU 연산

- H select: Shift 연산에서의 연산을 결정

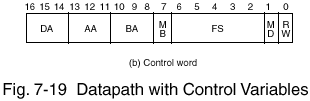

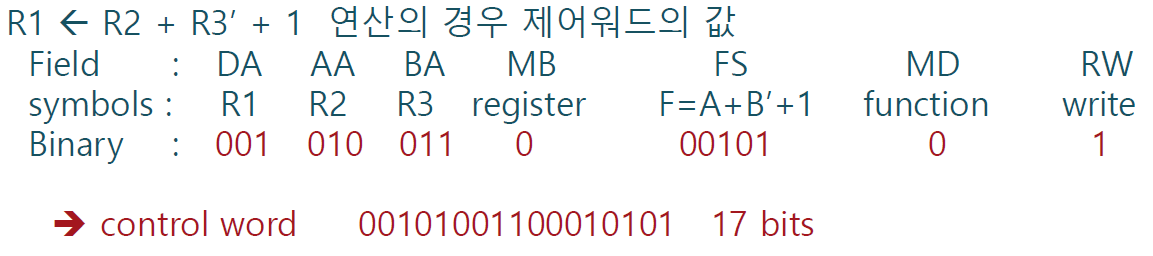

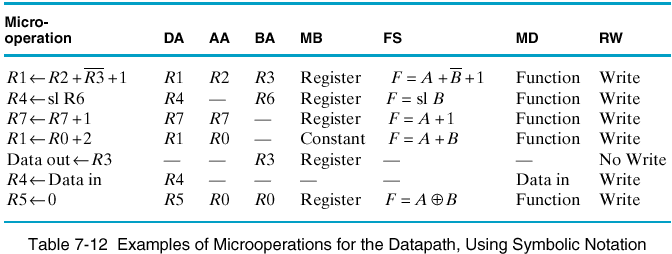

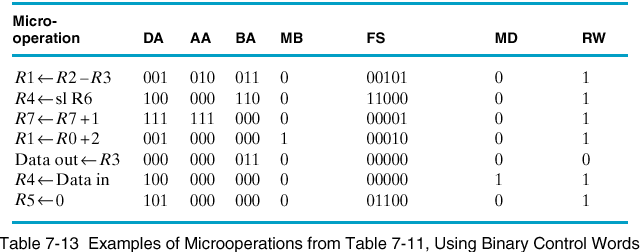

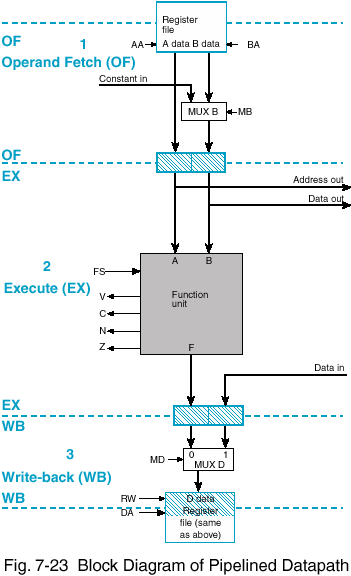

Control Word

- 마이크로 연산의 데이터처리에 필요한 제어신호로 구성

- 8개의 레지스터 파일을 가진 DP에 대한 제어 워드 형식

- 제어워드 필드구성

- 17 비트

-> dest 주소, 2개의 operand 주소

-> FS, MB, MD, RW

- DA: D address(Destination select: 레지스터 선택) ->

- AA: Openand A address

- BA: Openand B address

- MB: OPR B Select-> 상수, reg(Mux)값 중에 Select

- FS: 연산자 선택

- MD: Memory 값 또는 Function 값 선택

- RW: Register의 Write, not write를 결정

데이터처리 마이크로연산에 대한 제어워드 코드

위의 이론을 바탕으로 추후에 설계할 CPU 연산 테이블이다.

ASR: 산술 Right Shift(Shift 할 때마다 LSB에 1이 채워짐)

마이크로 연산의 실행

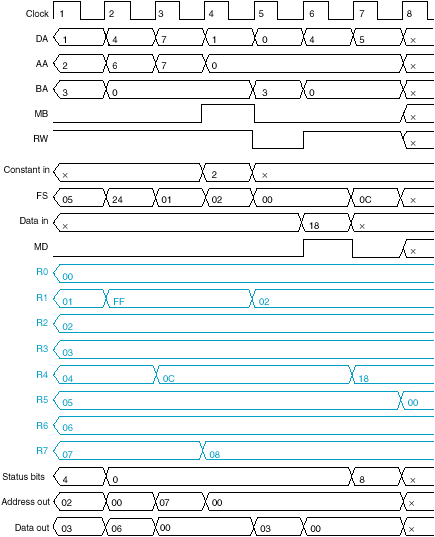

- 실행 시뮬레이션 파형

-> 각 uo 연산에 대한 destination

-> reg에 저장시 다음 클럭의 에지에서 발생되는 것에 유의!!

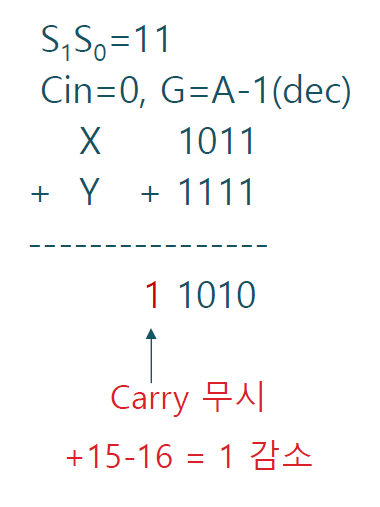

※ 0을 빼줄 경우,carry를 반전하여 발생하는 carry를 무시해준다.

※ 양수 연산에서 - 연산을 할때, carry를 반전시켜 무시한다.

파이프 라인

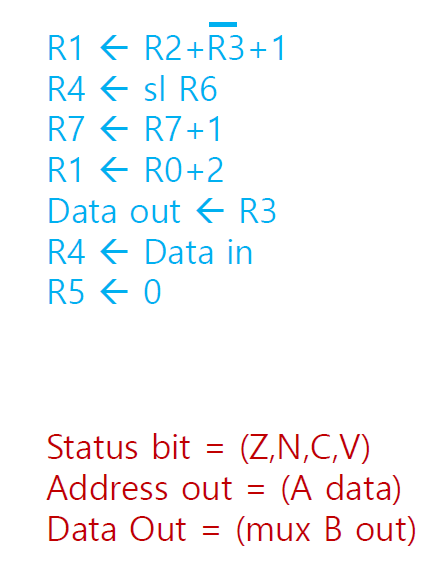

uo 실행의 처리속도와 단위시간 당 처리비율(thruput)

한 개 uo의 실행시간과 최대 주파수

- 기존 구조

->12 ns -> 83.3 MHz - 파이프라인(pipeline)구조

-> 5 ns -> 200 MHz

파이프라인: 연산의 실행시간이 긴 경로에 레지스터를 넣어 연산 시간을 짧게 하여 데이터처리

-> thruput를 높이는 하드웨어 구조

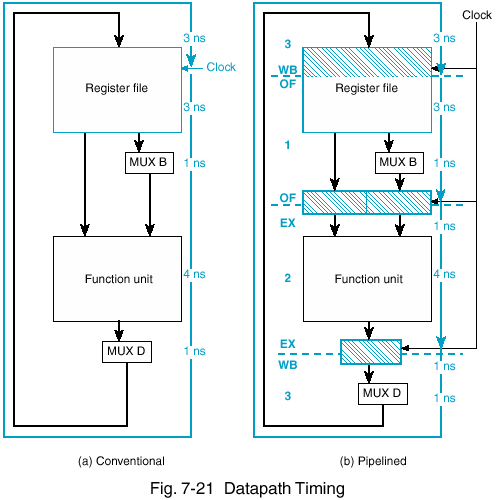

파이프라인 처리 장치 구분 예

- uo의 실행을 3단계로 분리수행

operand fetch(OF)

execute (EX)

write-back(WB) - 각 단계 사이에는 클럭 필요

- 중간 데이터를 (파이프라인 platform) 레지스터

에 저장

-> 추가적인 레지스터 사용으로 H/W 증가 - 각 단계의 실행시간은 짧아진다.

-> 동작주파수의 증가