순차진행과 제어기

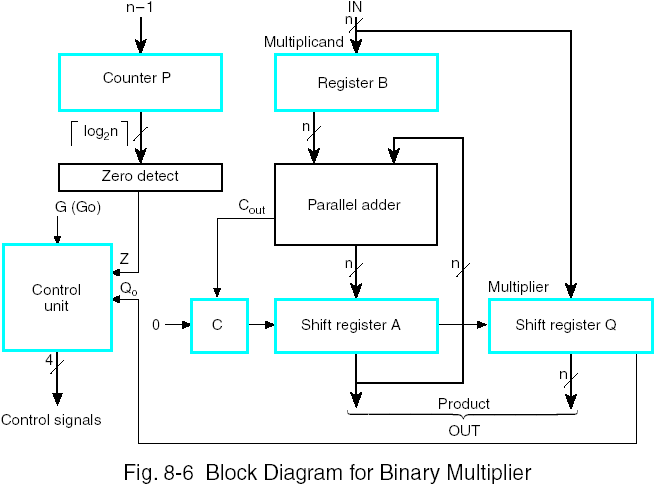

CAQ : carry, product(AQ), 승수(Q)

- shift right 레지스터

P 카운터

- shift 연산마다 down counter, 초기값 (n-1)

제어기

- 입력 : G, Z, Qo

- 출력 : 상태 및 모드 제어신호

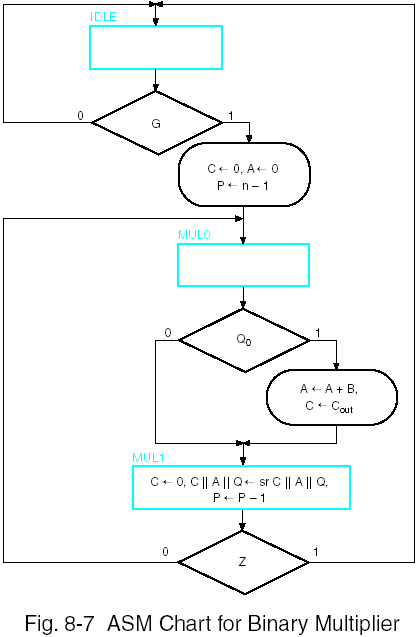

승산기 ASM

초기연산 : B <-피승수, Q <- 승수

- 3개의 상태

IDLE

- 외부입력 if G=0 이면 차기상태는 IDLE, else C,A,P초기화, MUL0로 천이

MUL0

if Q0=1 이면 addition C, A <- A+B, goto MUL1

MUL1

C || A || Q <- sr C || A || Q, C<-0

P <- P-1

if Z=1 goto IDLE

else goto MUL0

- loop n, P가 갱신되기 전의 값으로 Z 판단

데이터처리장치기능

A 레지스터 :병렬로드, 시프트, 동기클리어

Q 레지스터 :병렬로드, 시프트

C 플립플롭 : 로드, 동기클리어

B 레지스터 :병렬로드

P 카운터 :병렬로드,하강카운터

예시

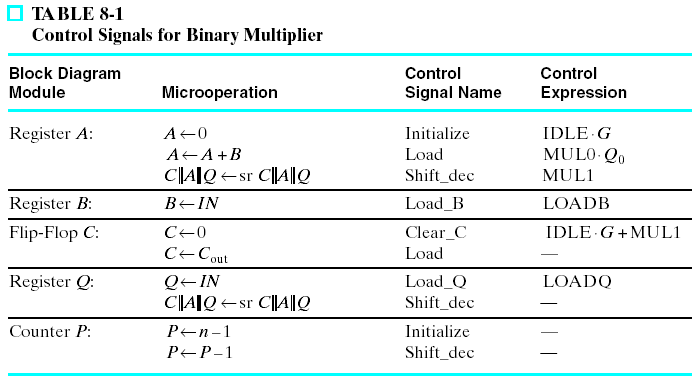

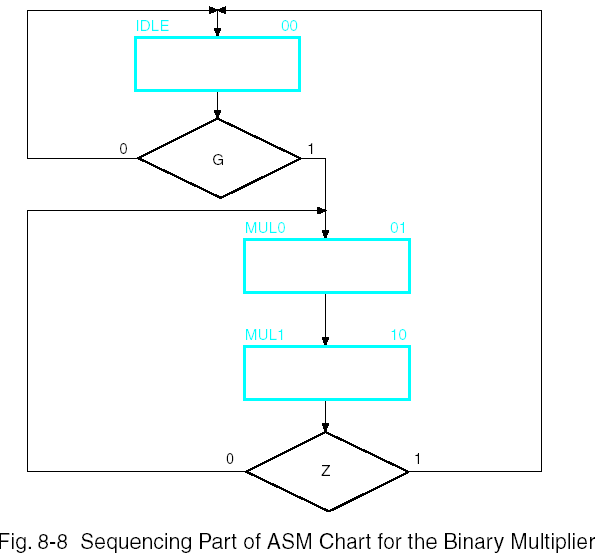

Control sequencer

- 데이터패스 모드제어신호 발생

- 제어순서 상태신호 발생

모드제어신호

- 각 마이크로연산 제어

- 레지스터 동작제어

- 상태 및 제어입력에 의한 논리식

상태신호

- 상태박스와 상태천이를 변화시키는 판별박스로부터 상태변화 유도

- 상태도와 유사

컴퓨터 구조

- 프로그램 가능한 제어구조기 사용

Instruction

- 컴퓨터의 프로그램정보

- 프로그램 메모리에 저장

- 1개 이상의 마이크로연산 실행

- instruction set : 컴퓨터의 전체명령어

-> 연산종류,오퍼랜드 정보포함

-> 명시적(explicit) 오퍼랜드

-> 묵시적(implicit) 오퍼랜드

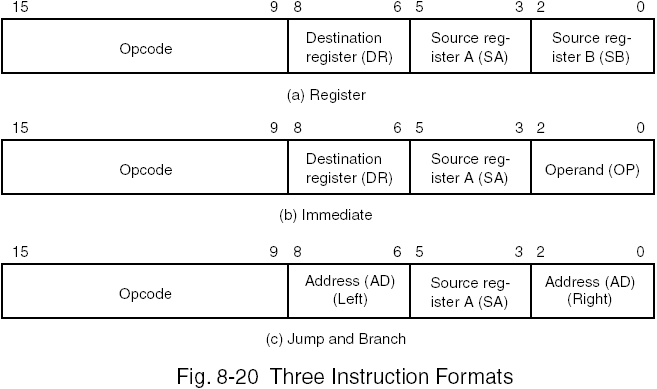

Instruction format

- opcode, DR, SA, SB등의 오퍼랜드 정보필드 포함

- 각 연산에 따른 format 차이

- 8개의 레지스터세트를 가정할 때, 각 오퍼랜드는 3비트 사용

-> 레지스터방식 : R1 <- R2 – R3 (sub)

-> immediate방식 : R2 <- R7 + 011

-> jump and branch 방식 : R 또는 메모리내용 변화 무

-> 명령어의 실행순서 변화 : PC값 변화 - PC 상대주소지정방식: PC를 기준으로 주소 offset을 2의 보수 형태로 저장

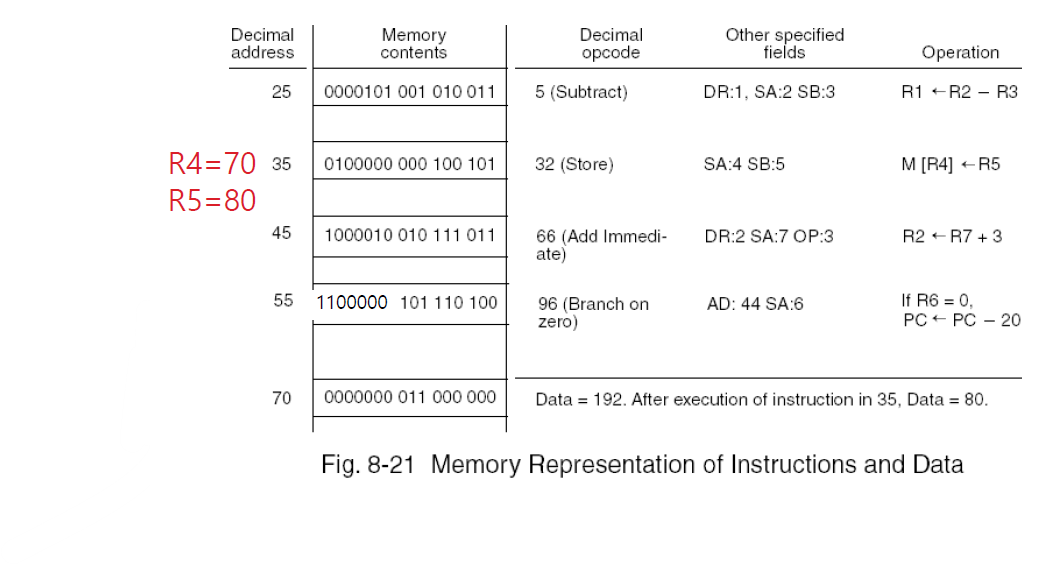

ex)

branch-on-zero R6(SA) 35(AD) <- 현재 PC가 55일때 –20을 AD에 저장, R6값이 0이면 55+(-20)으로 PC는 35

가 되고 R6=0이면 PC=56번지

*** AD주소를 자리확장시 부호비트를 확장(sign extension)함에 유의

7비트 opcode 명령어 + 9비트 operand

- 16비트 명령어형태

더 큰(32~64)비트 컴퓨터

- 한 워드의 길이와 동일

- 한 개의 즉시오퍼랜드 길이

- 메모리 주소 길이

- 레지스터 개수

- 명령어워드의 확장

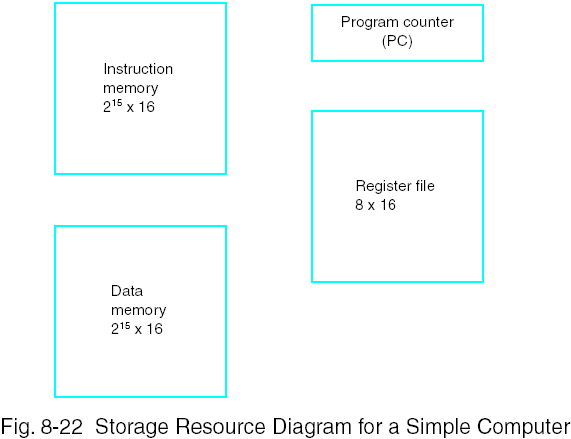

간단한 컴퓨터의 메모리 구조

사용자의 입장에서 사용할 수 있는 저장자원

-Instruction memory : CPU 명령어 저장

-Data memory : 프로그램실행시 데이터저장

-16비트 PC

-8개의 16비트 레지스터

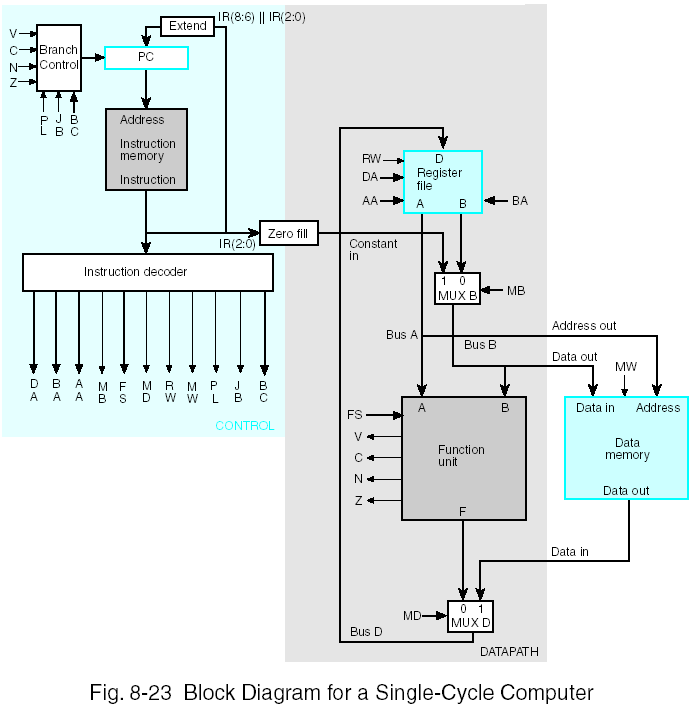

한 클럭 사이클에 한 개의 명령어 실행

- PC ( 현재 실행 명령어주소 저장)

- instruction memory(명령어인출)

- instruction decoder

-> 명령어해독, 연산종류, 오퍼랜드결정, 제어신호발생

-> 오퍼랜드로부터 ALU 연산 -> data 메모리에 R/W

-> 레지스터에 저장

-> 모두 한 개의 클럭 사이클에 실행됨

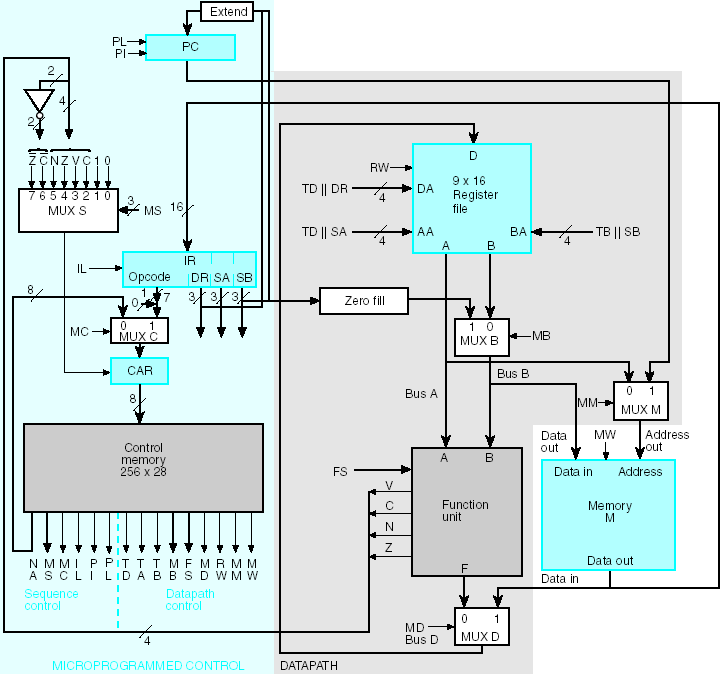

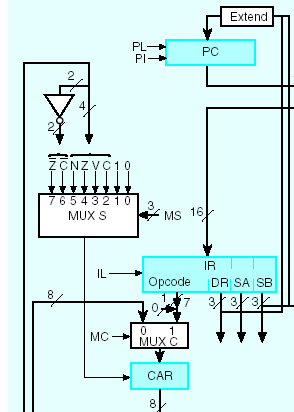

Multi cycle 마이크로 프로그램 제어

Multi cycle computer의 구조적 변화

M 메모리 : 데이터 및 명령어 저장

- MM mux로 주소 선택

- MB mux로 데이터 입력선택

- MD mux로 데이터 출력선택

레지스터 파일

- 기존 8개에 tmp reg R8 추가

- 오퍼랜드주소선 비트(TD,TA,TB)

- 다수사이클 실행데이터 임시저장

IR (instruction register)

- 현재 실행되는 명령어저장

- IL(instr load)

- 현재의 DP오퍼랜드(DR,SA,SB) 포함

-> 제어워드에서는 이를 생략하여 제어워드 구조가 단순화 됨

PC 제어신호

- PI : instr read시 1증가

- PL : PC PC+se AD

=> *se : sign extension

Control memory

- uI에 대한 제어워드 저장

CAR : CM의 주소값 지정,

- 아래 mux에 의해 CAR은 load/inc 동작

- MC mux : IR 또는CM 에 의한 주소

- MS mux : status에 의한 주소

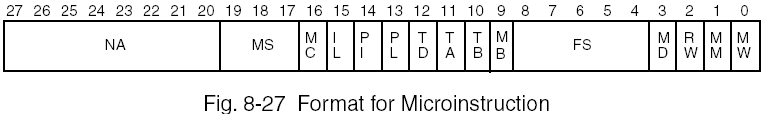

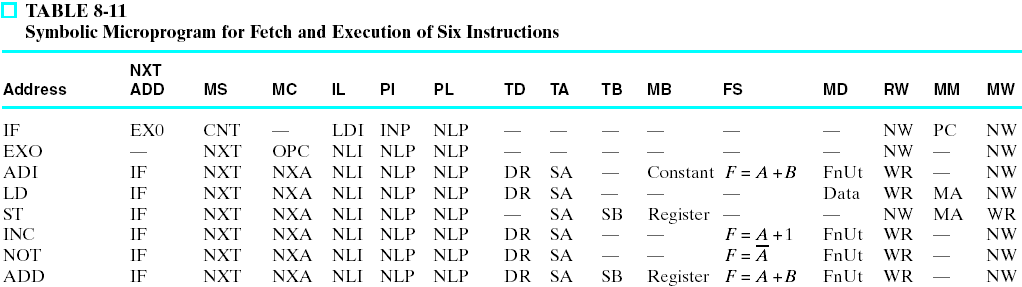

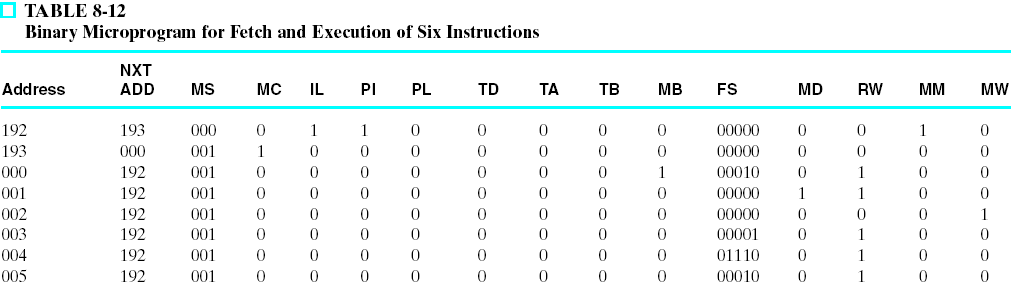

다수사이클 컴퓨터에 대한 마이크로 명령어의 형식

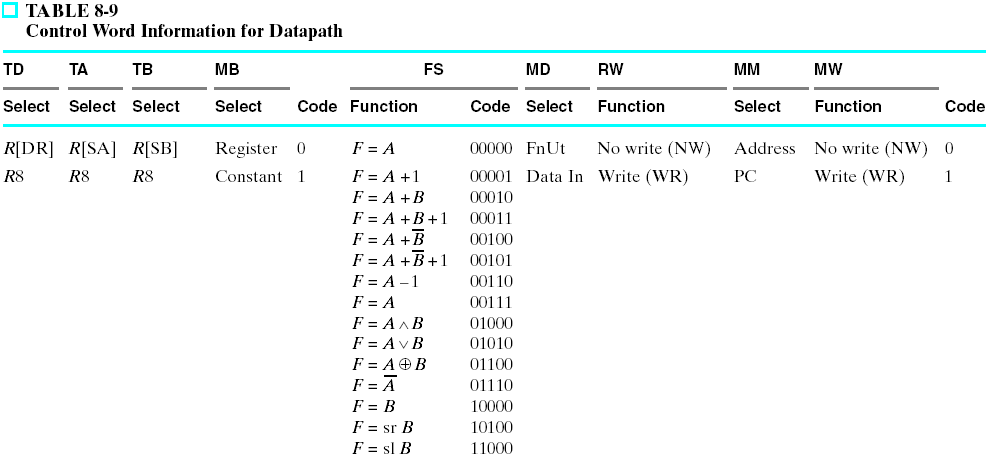

ALU 코드와 관련 DP 제어신호

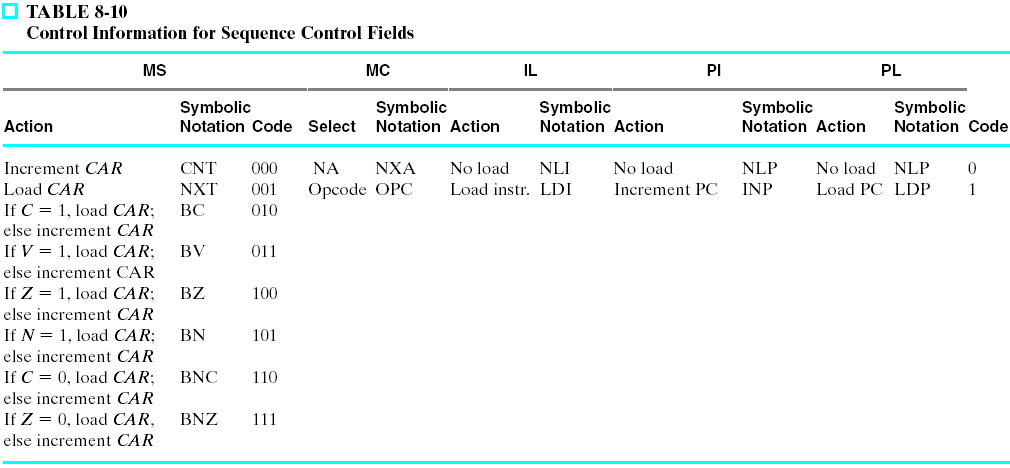

MUX S에 대한 선택값과 제어정보

마이크로 명령어 실행 단계

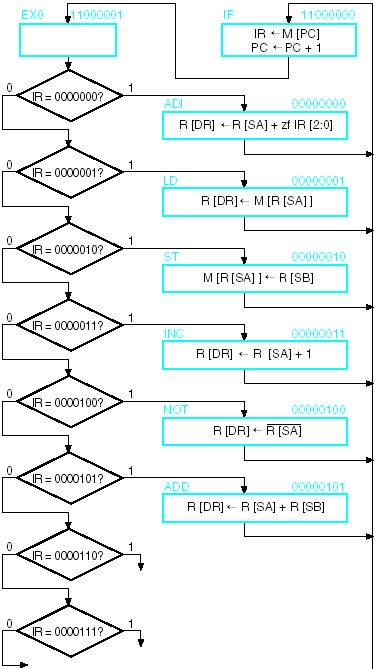

uI에 대한 ASM

- instr fetch(read) 상태 : IF

- instr 실행 상태 : EX0

IF 상태

- IR <- M[PC] , PC 지정주소에서 instr read

- PC <- PC+1 , 다음 instr을 위해 자동증가

EX0 상태

- IR값에 따라 instr decoding

- opcode 값에 따라 필요한 마이크로 연산 실행상태로 분기

- 7 bit opcode

-> 128 uI

-> 128 실행상태 분기

그림 예는 3개 사이클에 한 명령어 실행하는 ASM

각 Instruction에 대한 마이크로프로그램과 이진코드값 예

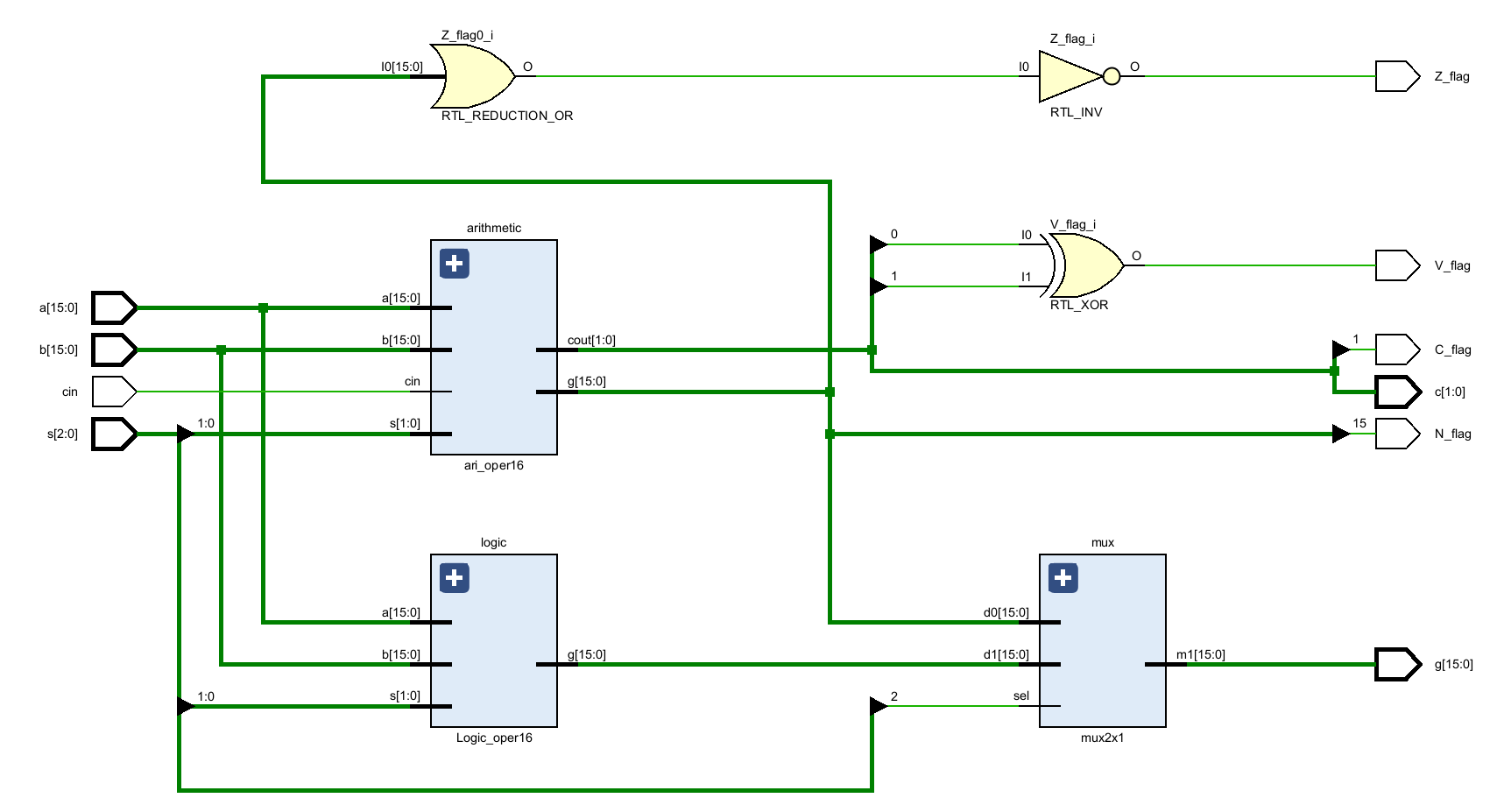

실습 ALU 설계

ALU는 산술 연산과 논리 연산 중 하나의 모드를 선택하며, 이때, Z(0), V(오버플로우), N(음수), C(캐리)의 여부를 출력한다.

우선 산술연산자를 설계해보자

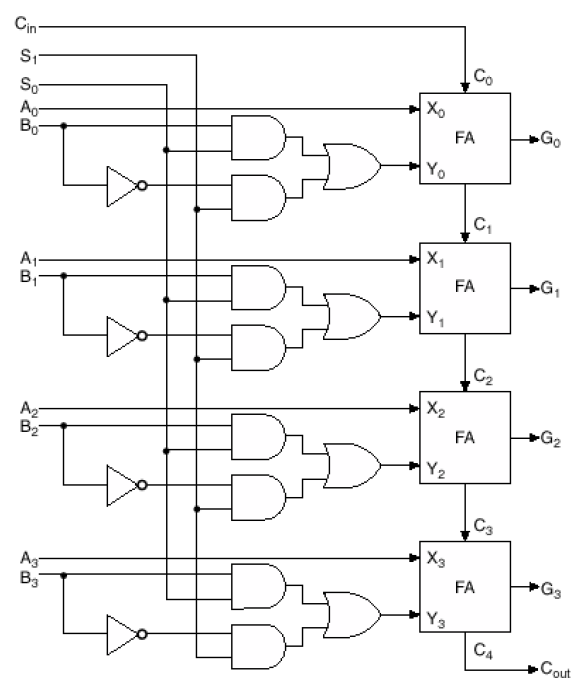

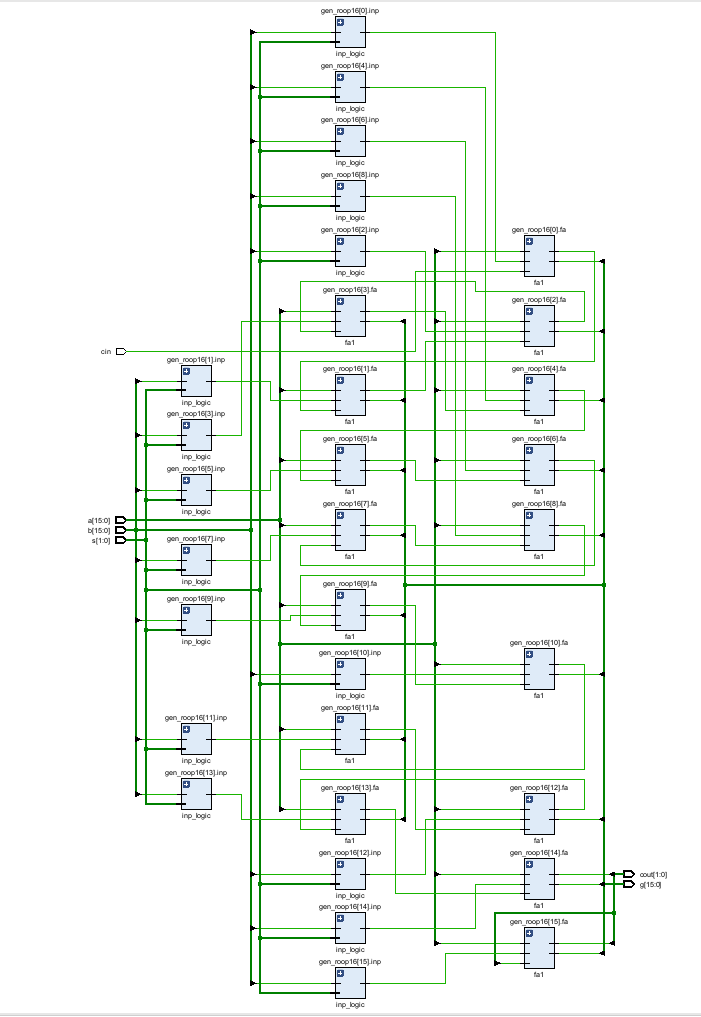

산술 연산자는 조합회로와 Full adder로 이루어져 있다.

조합회로 code

module inp_logic (s, b, y);

input b;

input [1:0] s;

output reg y;

always @ (s,b) begin

case(b)

1: if(s == 2'b11)begin

y = 1;

end

else if(s == 2'b01)begin

y = 1;

end

else if(s == 2'b10)begin

y = 0;

end

else begin

y = 0;

end

default:

if(s == 2'b11)begin

y = 1;

end

else if(s == 2'b01)begin

y = 0;

end

else if(s == 2'b10)begin

y = 1;

end

else begin

y = 0;

end

endcase

end

endmodulefull adder 코드

module fa1 (a, b, ci, co, s);

input a, b, ci;

output co, s;

assign co = (a&b) | (ci&a) | (ci&b);

assign s = a^b^ci;

endmodule산술 연산자

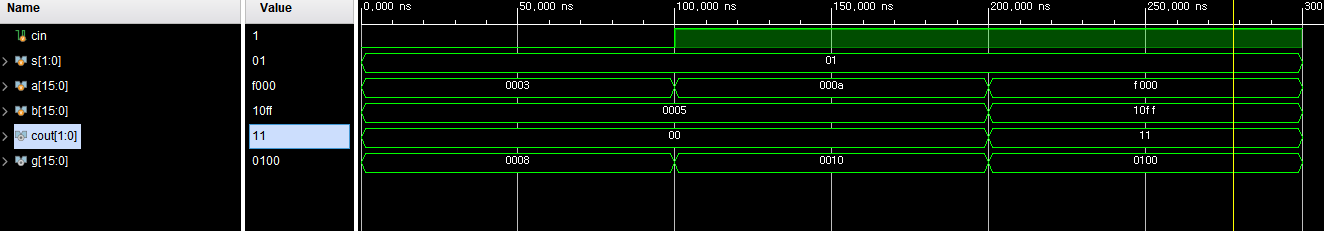

테스트 벤치를

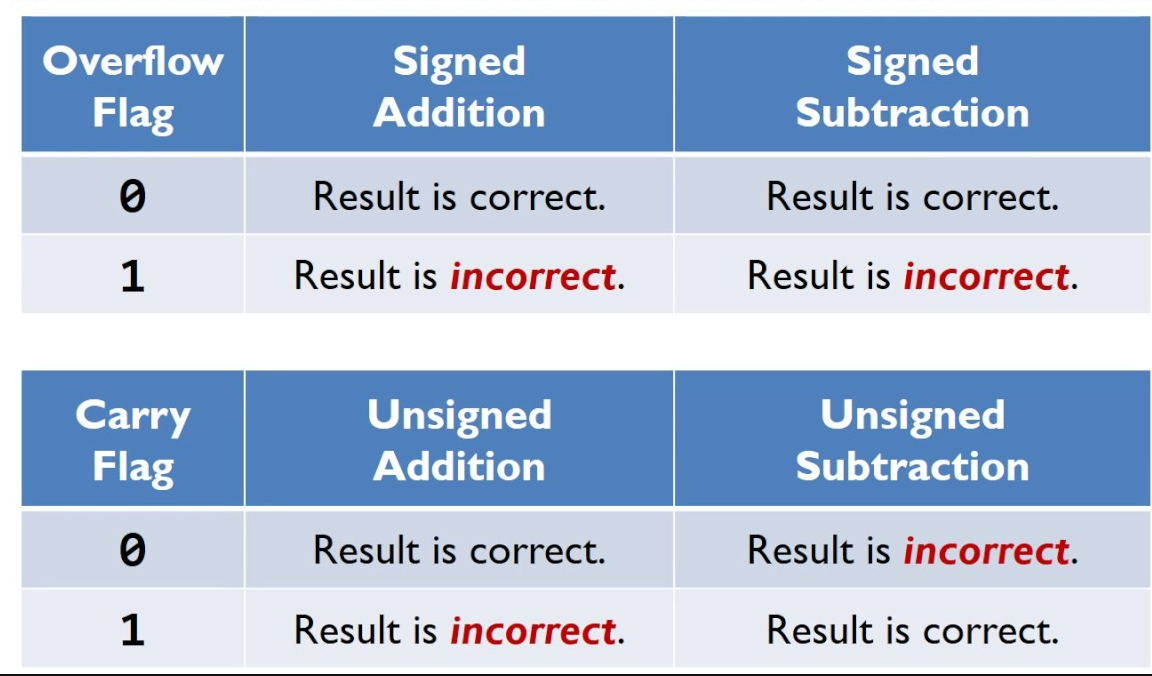

Falg에서 Overflow를 판독해야하는 V flag에 대한 의문이 생길 수 있다. 왜 이전 carry와 현재 carry가 1일 경우, 0으로 하여 over flow라고 하지 않는지 의문이 생긴다.

-> 이는 몰루?

ex) 1 - 0을 해보면 0001 + {1111 + 0001}(0의 2의 보수)일때, 0001이며, 이때, 최상위 carry와 그 이전 carry가 발생한다.

unsinged에서 덧샘을 할 경우, carry가 발생하면

unsigned의 경우, 계산이 옳고 그름의 여부를 C flag를 통해 판독하며, signed의 경우, V flag를 통해 연산의 옳고 그름을 판단한다.