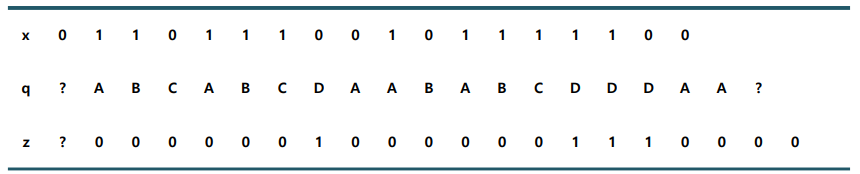

Programmable Logic Arrays

- ROMs

ROM 이라는 것은 모든 address가 사용되는 경우가 ROM이라고 볼 수 있음. 예를 들어서 3 input에 대해서 모든 input 패턴이 사용되는 경우를 ROM이 필요하다고 이야기 함

각각의 input pattern에 해당하는 것을 minterm이라고 볼 수 있다.

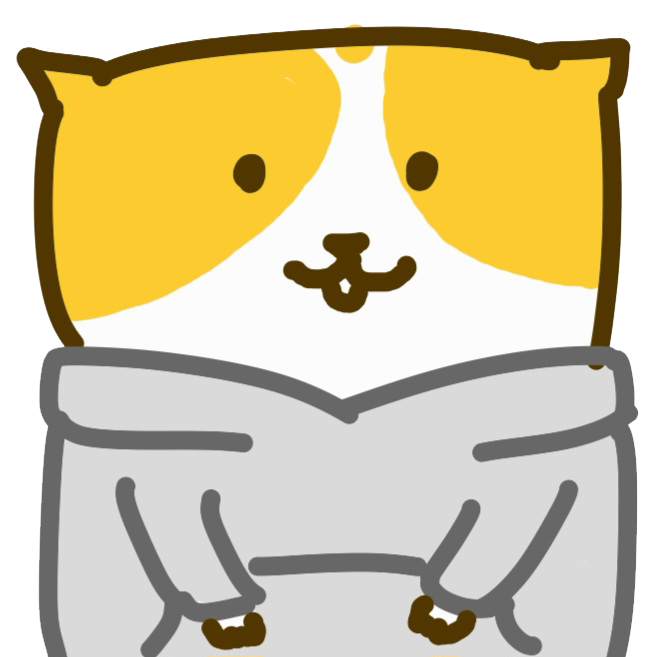

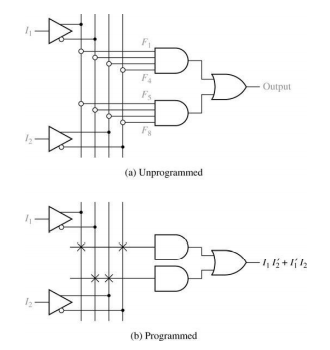

PLA는 모든 minterm이 사용되지 않고 일부의 minterm 혹은 product form으로 4개의 input만 들어와도 그 중 2개의 input만 사용되어 product라고 할 수 있다.

n개의 input이 들어오면 k개의 단어만 생성 된다는 것이 PLA로 AND array와 OR array모두 programmable하다고 할 수 있다.

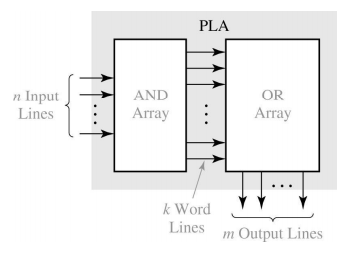

Designing with Programmable Logic Arrays

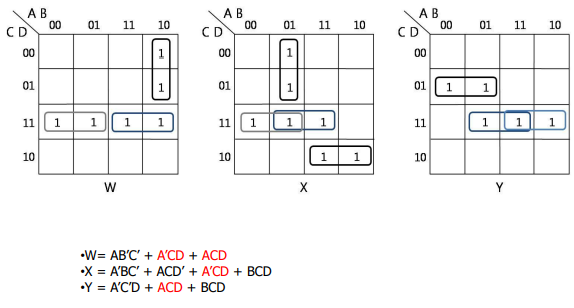

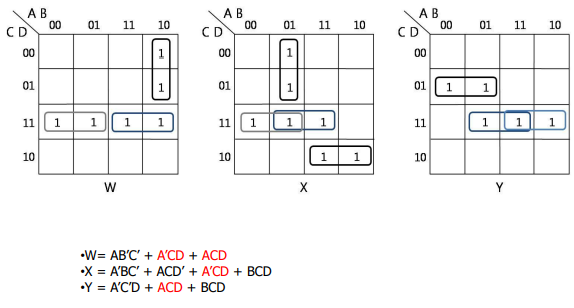

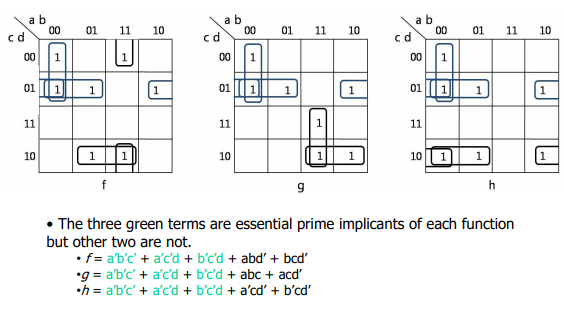

위와 같이 카르노맵을 구성할 수 있는 sum of minterm이 존재한다고 할때.

PLA example

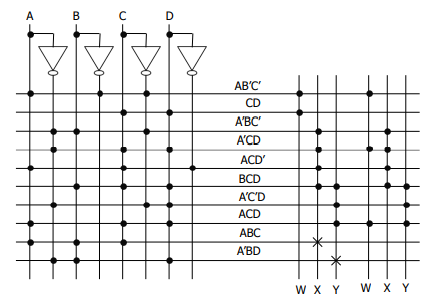

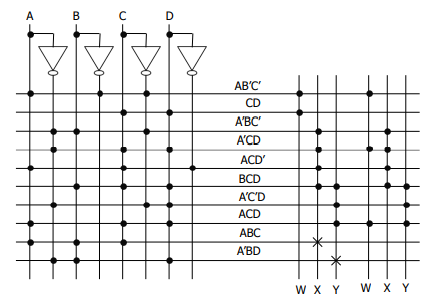

그래서 위에서 나온 카르노맵을 PLA화 시킨다.

위와 같이 적절한 행과 열을 구성하여 Logic Implementation한다. 그래서 우리는 PLA는 사오고 최대한 많은 로직 Function을 구성한다.

그래서 minterm이나 product term을 최대한 share 할 수 있다면 좋은 것이다. 이를 위해서 카르노 맵을 아래와 같이 바꾸게 된다.

위와 같이 구성하면 좀 더 겹치는 부분이 많기 때문에 최적의 PLA가 나오게 될 것이라 예상이 된다.

실재 결과로 나온 식 또한 겹치는 것이 많기 때문에 적은 수식으로 식을 구성할 수 있다는 것을 이해할 수 있다.

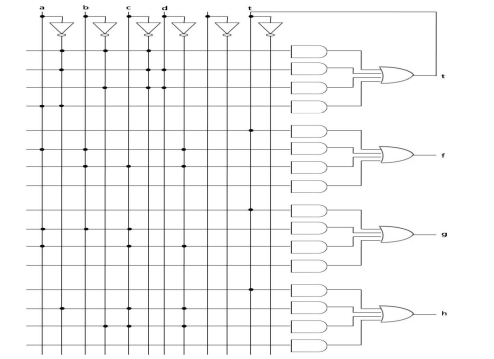

그래서 나온 PLA가 아래와 같다.

- Solution

이때 X로 표현된 부분은 이 친구를 선택할 수도 혹은 다른 친구를 선택할 수도 있다는 이야기 이다.

WXY 좌 우로 나뉘어져 있는데 왼쪽은 원래의 카르노맵을 그대로 사용한 경우 오른쪽은 최적화한 결과를 PLA 화 한 것이다. 실재 이어진 term의 갯수는 오른쪽이 많을지 몰라도 재사용 된것이 보다 많은 것을 확인할 수 있다.

Programmable logic array(PAL) devices

그렇다면 도대체 ROM, PLA, PAL 과 같이 다양한 디바이스를 제작하는 것인가? 그것은 반도체 기술에 따라 만들 수 있는 디바이스가 다르기 때문이다.

- ROM

- OR Array prgrammable (AND array => decoder)

- PLA

- AND & OR Array programmable

- PAL

- AND Array prorammable (OR array fixed)

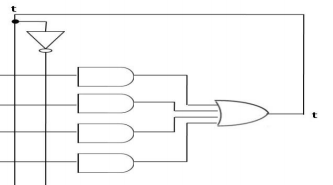

위의 그림을 봐보자 위의 부분에서 AND 게이트가 이전에 나오는 부분에서 programmable 하여 AND 게이트에 들어가 최종 결과는 FIX 된 OR 게이트에 들어가게 된다.

아래쪽은 실재로 program 해본 결과물이다.

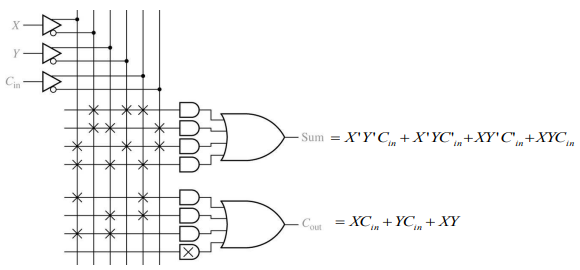

Implementation of a Full Adder Using a PAL

그래서 PAL을 활용하여서 Full Adder을 구성하면 위와 같이 구성할 수 있게 된다.

Eample 4.11

쫌 더 복잡한 예제를 확인해 보자 카르노 맵을 맵핑해보면 위에서 보이는 것과 같이 연두색 EPI 들이 등장하게 될 것이다. 그런데 이 친구들은 다시 생각해 보면 overlapping 된 것으로도 볼 수가 있다.

- solution

문제는 위와 같이 구성할 경우 AND 게이트가 단 4개이기 때문에 식이 5개인 function을 커버할 수 없다.

그래서 새롭게 계속 사용될 녀석을 만들어 놓고 새로운 input으로 사용하는 것이다.

Ch 5 Analysis of Sequential Systems

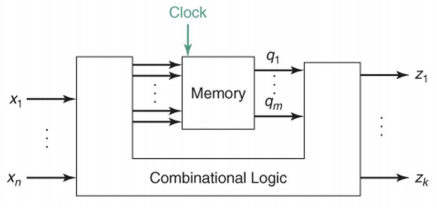

Sequential System은 메모리가 존재하는 회로를 이야기 한다.

그래서 출력값이 현재의 입력과 과거의 정보를 이용하게 된다.

구성을 보면 입력에 대해 Combinational Logic에서 process해서 Memory에 저장이 되고 Output을 만들때 input과 memory를 합치어서 만들어진다.

또한 Clock을 사용한다.

Synchronous system이라고 부르며 Clock에 동기화 된 시스템이다. Clock이 존재하지 않으면 우리가 언제 데이터를 쓰고 읽을지가 불분명해지기 때문에 존재한다.

Sequential System은 Machine이라고 부르기도 하며 대표적으로 두가지가 존재한다. 하나는 Moore machine이다. 다른 하나는 Mealy machine이다.

Clock

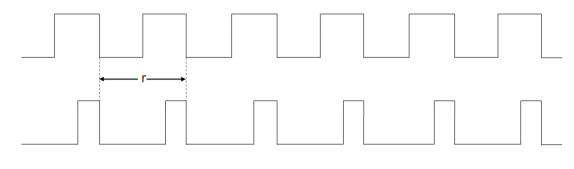

Logic Level이 0과 1이 반복하는 것을 이야기 한다. 이 경우 Voltage 즉 Clock이 만들어지게 된다.

그렇다면 Clock을 어떻게 만들어지는 것인가? 이것은 컴퓨터 내부에 크리스탈이라고 하여서 주기적으로 진동을 일으키는 것이 존재한다. 이것이 진동을 일으켜서 CLOCK을 만들어내는 것이다.

이때 r이 Clock period이다.

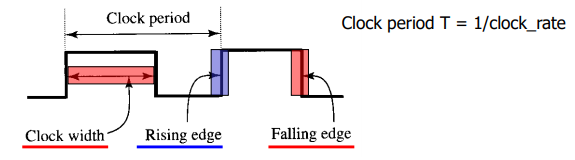

그리고 진동 사이의 폭이 Clock width, 올라가는 클락을 Rising edge, 떨어지는 클락을 Falling edge라고 부른다.

그래서 Clock period T = 1/clock_rate 이다. 예를 들어서 클락이 1Ghz=10^9라고 하면 T=1ns 이다.

Moore machine

Sequential System을 디자인 할때는 Moore machine 혹은 Mealy machine을 사용한다.

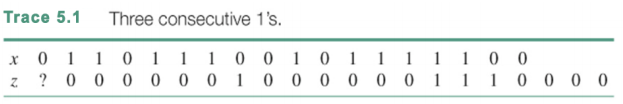

Moore Machine : 입력 x와 출력 z가 존재할때. z=1일때 연속적인 시간에서 1이 연속 3번 나타났을 때 output이 1이 된다.

위에서 z가 ? 인 부분이 존재한다. 이것은 이전에 무엇이 있었을지 예상할 수 없기 때문이다.

그것을 제외한 부분들을 보면 3개의 비트가 1이 나타난 경우에 그 다음 z에 1이 출력되는 것을 확인할 수 있다.

- Output이 현재 input이 아닌 이미 일어난 input에 대해서 출력을 생성한다.

Mealy machine이 나중에 나오겠지만 moore machine과의 차이점은 출력되는 순간이 moore machine에 비해 즉시 반응한다는 것에 있다.

Moore machine(State table, State diagram)

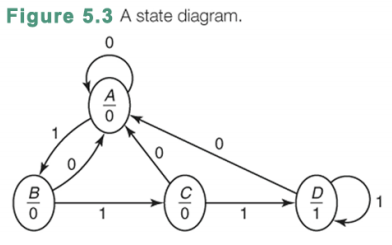

Sequential Circuit은 State Diagram으로 제작하게 된다.

위의 그림에서 동그란 부분들은 State들을 나타내고 State라는 것은 특정한 일을 수행하기 위해서 필요한 기억해야할 State를 이야기 한다.

화살표는 입력값을 이야기 한다. 그래서 입력값에 따라서 State가 변화하는 것을 이야기 한다.

동그라미 안에있는 숫자들은 output을 이야기 한다. 앞에서 Moore Machine도 State에 따라서 출력값이 달라진다고 한 것과 같이 State Diagram에서도 State에 따라 다른 Output을 보여주고 있다.

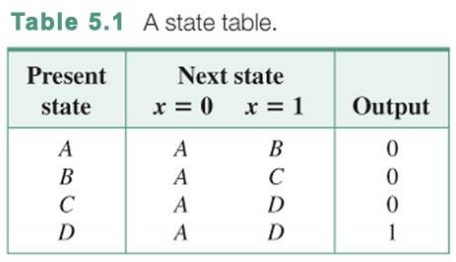

또한 위의 state diagram을 state table로 표현할 수도 있다. 마치 지리표와 같은 형태의 state table은 현재 state에서 입력이 무엇인가에 따라 state 변화와 출력값이 결정되는 것을 확인할 수 있다.

예시를 하나 보면 아래와 같이 표현될 것이다.