20) 디지털회로개론

1.디지털 회로 개론 자료출처

https://prezi.com/bupsk17gkg67/2/?frame=7cb045804cf33f3585fc21ade3b85d88ef2080ab

2.디지털 회로 개론 00

숙제나 과제는 영어로 받음이론 배경 : 조합 논리 회로와 순차 논리회로의 설계 및 분석을 다룬다.디지털 회로의 구조 및 구성 원리를 이해하여 설계 할 수 있는 능력을 갖도록 한다.과제각 단원에 대한 연습문제를 푼다.연습문제에 풀 때 계산과정 및 풀이과정을 보인다.

3.디지털 회로 개론 01 (Digital Systems and number systems)

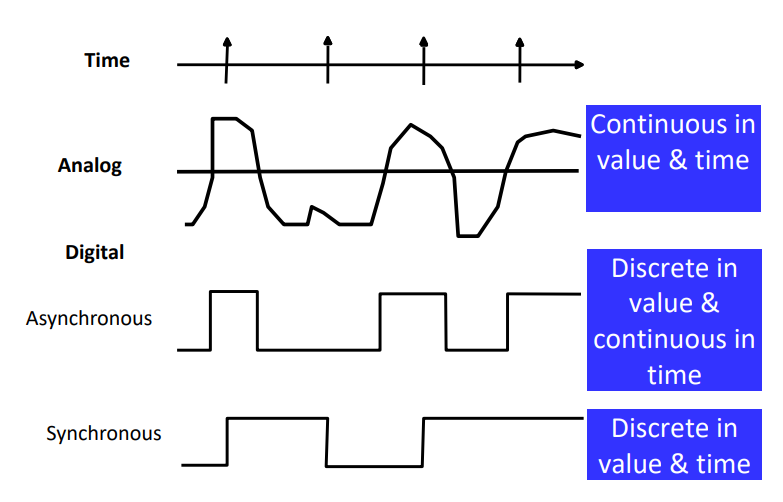

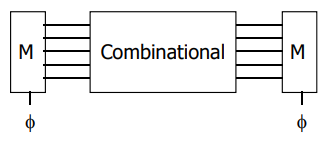

디지털 시스템에는 두가지 종류의 시스템이 존재한다고 함두 시스템을 나누는 기준은 저장장치가 존재하는가에 있다고 함Output = Function(Input)사실상 입력 넣는데로 출력이 나오는 Combinational 회로Sequential 회로는 두가지로 나뉘는데 Sy

4.디지털 회로 개론 02(2진수 보수와 연산)

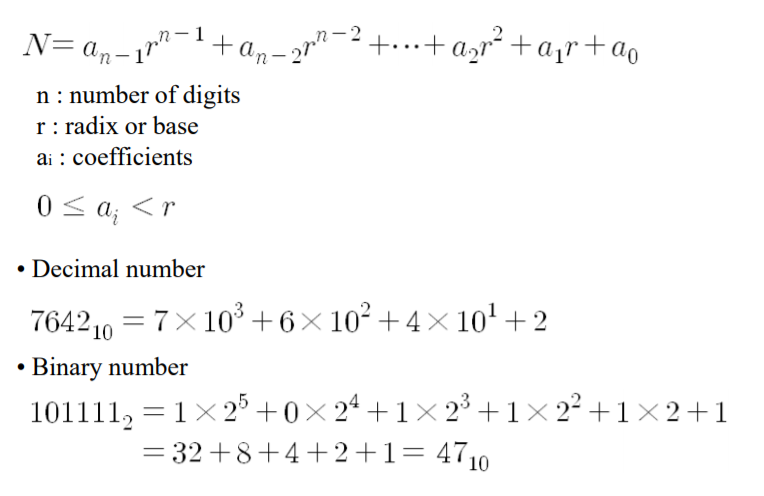

이제 컴퓨터가 데이터를 받을 수 있도록 데이터 변환방식에 대해서 생각해 보도록하겠다.Number System은 대표적인 2,8,16 진수의 꼴로 데이터를 표현하는 방식으로 0과 1만의 데이터를 읽는 컴퓨터에 이어서 매우 필요한 방식이다.10진수 / 2진수 / 실수 /

5.디지털 회로 개론 03(디지털 코드, 불대수)

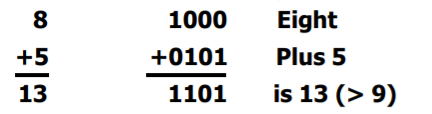

BCD 코드

6.디지털 회로 개론 04(불 대수)

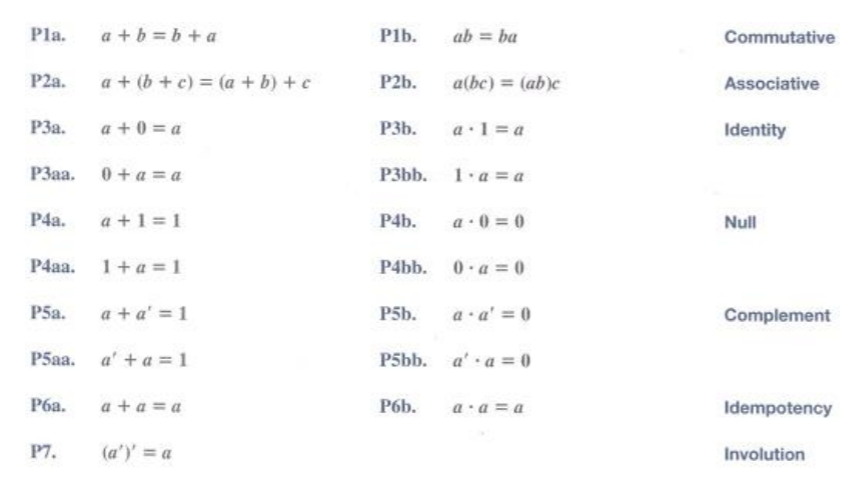

어떠한 디지털 로직을 만든다면 원하는 input과 output이 주어졌을 때 어떻게 시스템을 디자인해서 우리가 원하는 시스템 output을 만들어 낼 수 있는가를 step을 밟아 가면서 만드는 과정을 배우게 됨Computer design : CPU(Central Pro

7.디지털 회로개론 05(불대수-드모르간, 최소항)

(x+y)'=x'y'A+A' = 1 is complement를 이용한 증명let (x+y) + (xy)' = 1x+y+x'y' = (x+y+x')(x+y+y') x+yz=(x+y)(x+z)=(1+y)(x+1) = 1·1 = 1A·A' = 0 을 이용한 증명let (x+

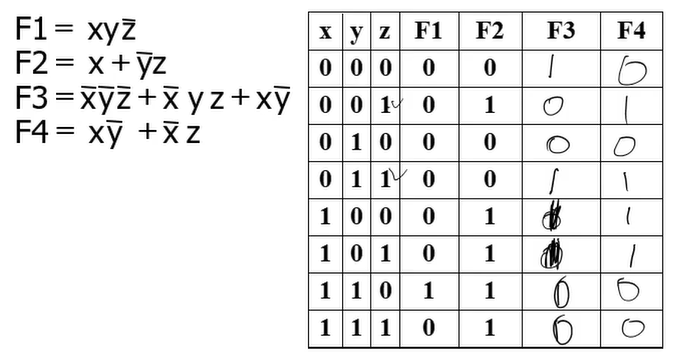

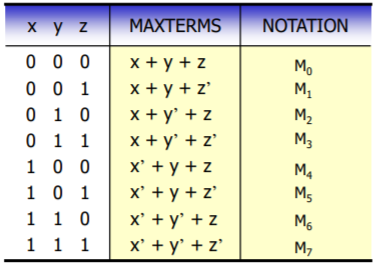

8.디지털 회로 개론 06(불 대수-최대항)

Canonical Forms - Maxterm

9.디지털 회로 개론 07(논리게이트, 논리식의 간소화)

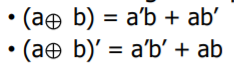

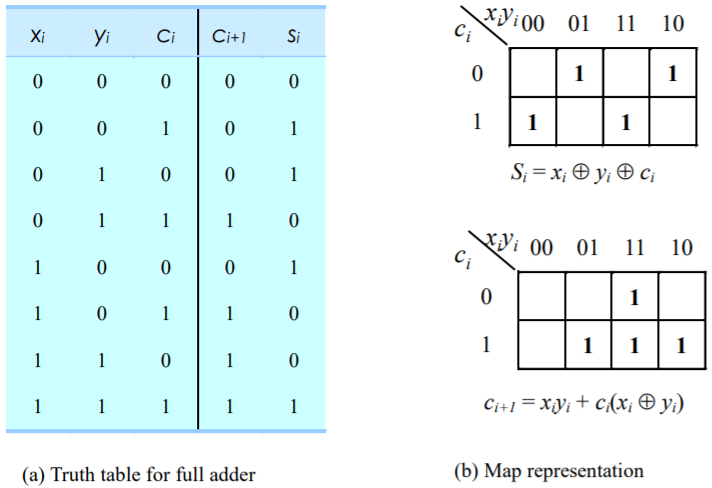

XOR 게이트홀수 개의 1의 입력된 경웨 출력은 1이 되고 그렇지 않으면 출력이 0이 된다.불 대수식은 다음과 같다.F = (a⊕b) = a'b+ab'F' = (a⊕b)' = a'b'+ab반가산기는 2진수 한 자리 덧셈을 하므로 아랫자리에서 발생한 캐리를 고려하지 안기

10.디지털 회로 개론 08(카르노맵1)

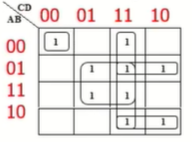

카르노 맵은 1953년 모리스 카르노가 소개하였습니다. 카르노 맵은 함수에서 사용할 최소항들을 각 칸 안에 넣어서 표로 만들어 놓은 것이다. 2변수일 때는 4개, 3변수일때는 8개, 4변수일 때는 16개의 칸이 필요하다.변수가 5개, 6개 정도 되면은 힘들지만 추후에

11.디지털 회로 개론 09(카르노맵 2)

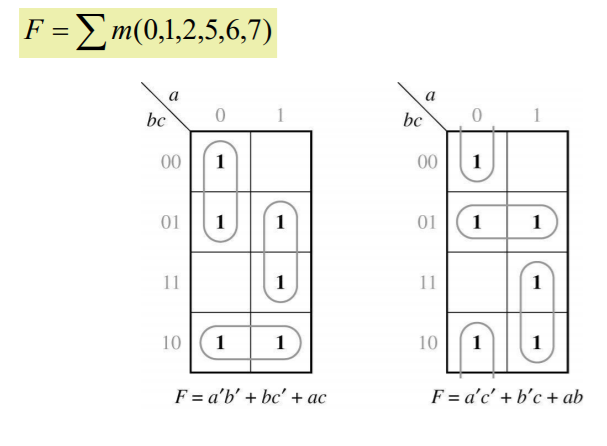

6.2 3변수 카르노 맵 예를 들어서 x'yz'+x'yz+xy'z'+xy'z+xyz 가 있다고 하면 다음과 같이 묶으면 된다. 2번 방법은 PI가 아님에도 따로 남기어 두었기 때문에 제대로 Implicant를 구성하였다고 볼 수 없다.

12.디지털 회로 개론 10(카르노맵 3, 조합논리회로)

k-map with Don't Cares 세븐 세그먼트를 보면 중간 중간 x가 있는 것을 볼 수 있다. 이것은 이 곳에 0 또는 1이 들어와도 상관이 없다는 표시이다. 혹은 digit가 없어서 dont care 처리한 것도 확인할 수 있다. 그래서 dont car

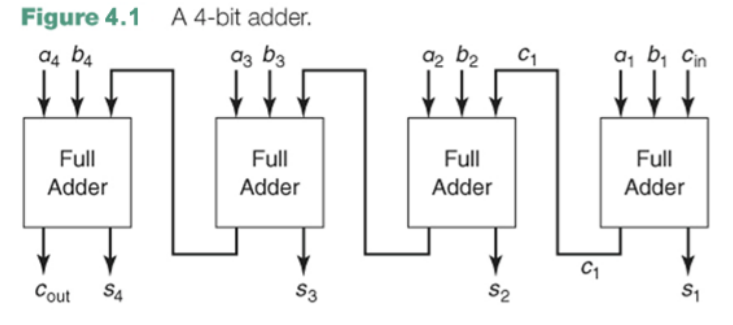

13.디지털 회로 개론 11(조합논리회로-가산기, 고속가산기)

(ripple carry) 아래와 같은 병렬가산기를 리플-캐리라고 한다.critical path delay = longest path delay => clockcycle time을 결정그런데 이게 리플-캐리는 속도가 빠르지 않기 때문에(딜레이가 O(n)정도 걸린다.)

14.디지털회로개론 12 (디코더, 멀티플랙서, CLA Delay)

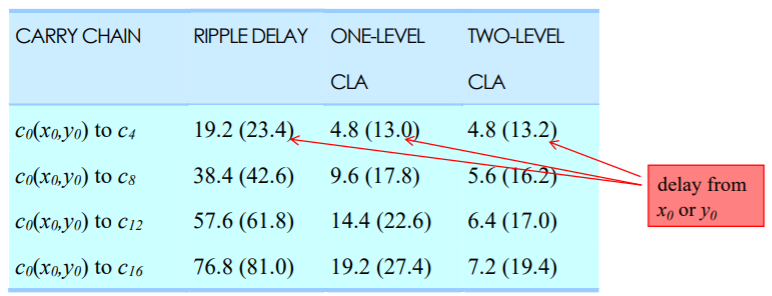

CLA의 Delay의 계산 결과를 보면 위와 같이 계산되는 것을 확인할 수 있다. 보면 알겠지만 원래 가산기 회로에 비해서 속도가 점차 빨라지는 것을 확인할 수 있다. 이것은 이미 기존에 값을 게산해 두었기 때문에 속도가 빨라진 것을 확인할 수 있다.A와 B에 n비트의

15.디지털 회로개론 13(BUS, ROM, buffers)

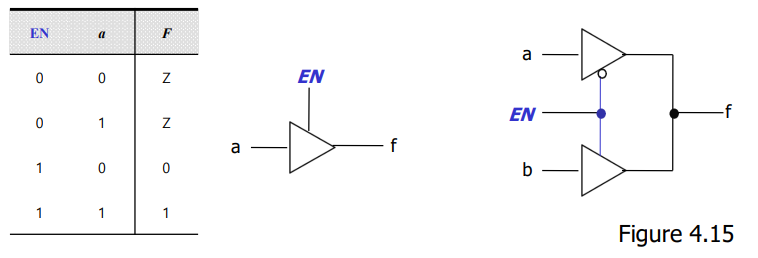

Three state gates : Tri-state buffer 이라고 부른다. 이때 output이 Z, 0, 1 세가지 중 하나로 결정하며 Z는 High Impedence state이다. 이는 곧 아무 상태에도 연결이 되어 있지 않다는 것을 이야기 한다. 그렇기에

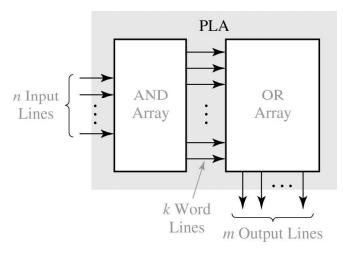

16.디지털 회로 개론 16(PLA, PAL, Moore Machine)

Programmable Logic Arrays ROMs 모든 address가 사용되는 경우

17.디지털 회로 개론 17 (Mealy machine, Latch, Flip Flop)

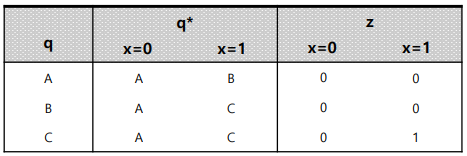

Mealy machine output이 state와 input에 동시에 dependent 한 machine을 이야기 한다. State Diagram을 보면 위와 같이 그려진다.

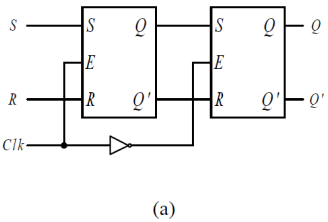

18.디지털 회로 개론 18 (SR Flip Flop, JK Flip Flop, T Flip Flop, D Flip Flop)

두개의 SR Latch로 만들어지는 플립플롭이다. 심볼은 위와 같이 사용한다.이때의 입력에 따른 변화를 보여주는 behavior table을 보면 이때에도 SR이 11이 나오는 경우는 허용되지 않는다. 이때 앞에서는 CLK를 꼭 명시해주었으나 behavior table

19.디지털 회로 개론 19 (JK Moore, Mealy Model, Design procedure)

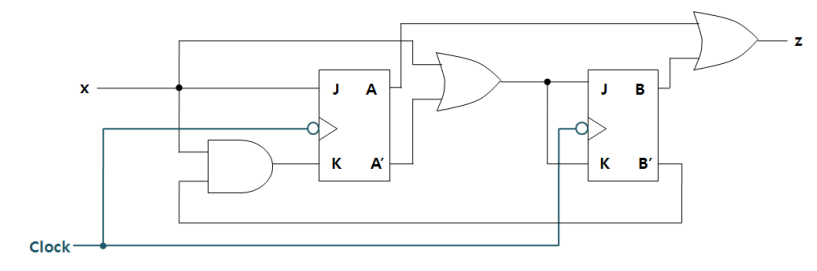

JK 플립플롭을 사용한 Moore model circiuit을 살피어 보자 위의 회로를 통해 Boolean Equation을 구성해 보면JA=XKA=xB'JB=Kb=X+A'z=A+BJK 플립플롭의 behavior table을 살피어 보자. 왼쪽 단순화된 식을 보면 이전

20.디지털 회로 개론 20 (State Table)

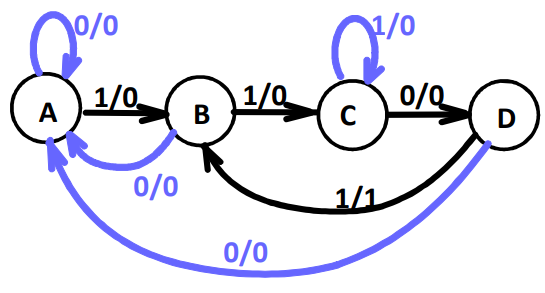

이전 단원에서는 1101을 찾는 state들을 명확하게 나타내었으나 중간에 우리가 원하지 않는 패턴이 들어왔을 때 어디로 돌아가야 하는지에 대해서는 생각해 보지 않았다.그래서 우리가 고려하지 않은 경우를 작성해 보면 위와 같이 그려지는 것을 확인할 수 있다.그 다음 단

21.디지털 회로 개론 21 (Finite State Machines, synchronous counter)

FSM은 State Diagram을 만들때 본 것과 같이 FSM을 이용해서 State Diagram이 만들어 진다.– I is a set of input combinations– O is a set of output combinations– S is a set of s

22.디지털 회로 개론 22(synchronous counter, MOS Transistor, CMOS Circuit)

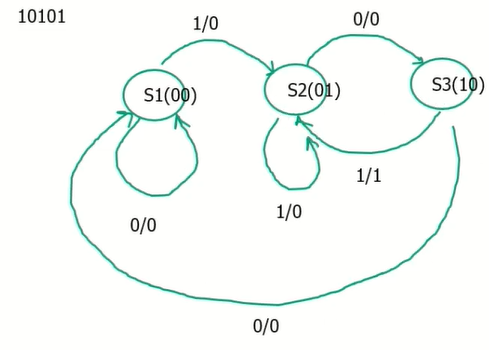

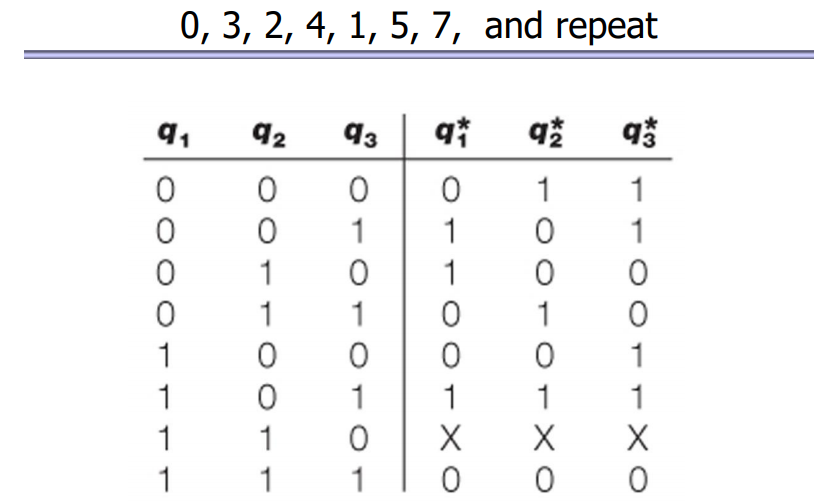

위에 보이는 것은 0->3->2->4->1->5->7->0 이 반복해서 카운트 하는 카운터이다. 그래서 6은 카운트하지 않기 때문에 만들어지면 안되는 숫자라는 의미에서 결과값이 모두 X로 처리되어 있다.그래서 이것을 D 플립플롭으로 디자인하게 되면 D 플립플롭이 따로

23.디지털 회로 개론 23 (ASIC and CAD, Circuit Classification, Circuit design, Circuit Design Constraints)

ASIC : 특정 기기를 위한 특별한 회로로 시장이 수요가 충분히 커야지 만들어 낼 수 있다.그래서 다음의 사항들을 고려하게 된다.volume of salesfast design timelow design costdesign quality measured by perf

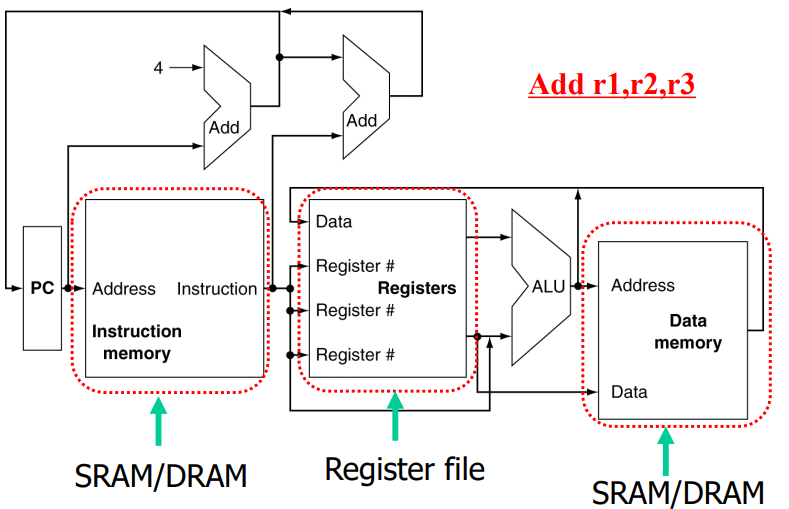

24.디지털 회로 개론 24 (CPU, register file, memory, ram)

cpu가 어떻게 구성되는지를 보여주는 block-diagram으로 assembly code가 있으면 우리가 assembly code를 순차적으로 실행하게 된다. 주소를 가지고 특정 assembly code를 읽어온다. 그리고 그것을 Register file에서 번역해서