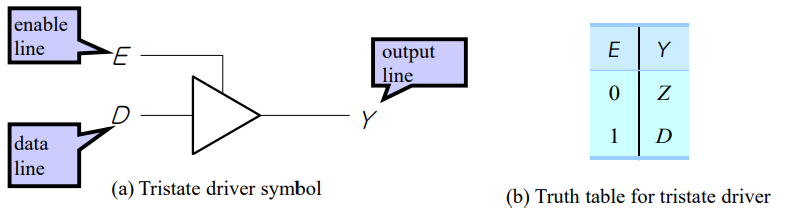

Three state gates (buffers)

Three state gates : Tri-state buffer 이라고 부른다. 이때 output이 Z, 0, 1 세가지 중 하나로 결정하며 Z는 High Impedence state이다. 이는 곧 아무 상태에도 연결이 되어 있지 않다는 것을 이야기 한다. 그렇기에 Z는 어떠한 상태인지 우리가 알 수 없다.

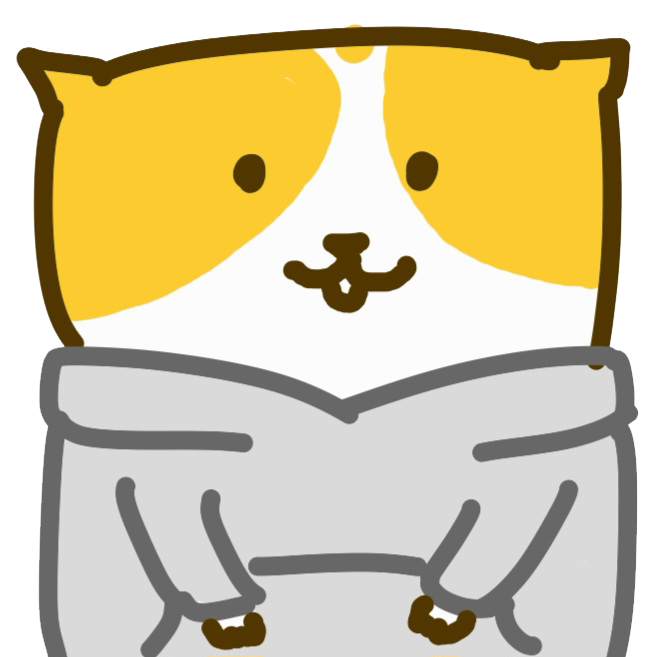

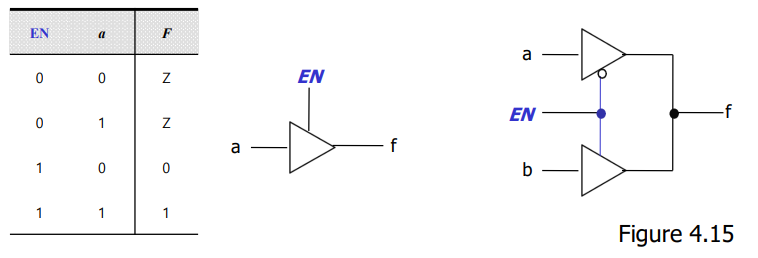

위 그림의 표에서 보는 바와 같이 EN의 상태에 따라 출력값이 결정되는 형태의 구조이다.

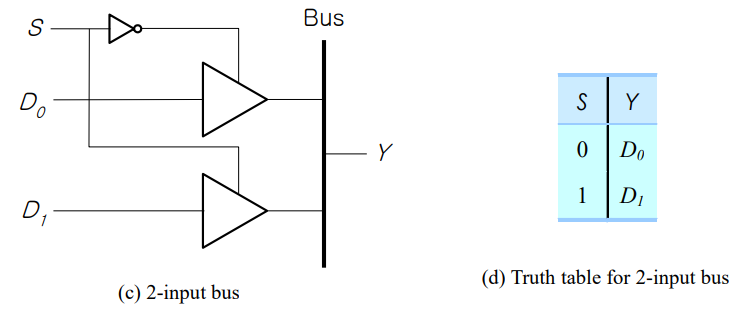

또한 위의 구조를 조금 더 활용하여 Three state output을 보다 많이 만들어 낼 수 있다.

혹은 위와 같은 구조로 제작하여 EN의 상태에 따라 a 혹은 b 만이 입력되도록 바꿀 수 있다. 어떤 의미에서 멀티플렉서의 형태를 띈다고 볼 수 있다.

그러면 만약에 게이트 없이 와이어를 연결하면 어떻게 될까? 그 경우 a혹은 b 와이어 모두 전류를 보내어 누전현상이 발생할 것이다. 그래서 일부러 게이트를 사용하여 회로를 구성하는 것이다. 그리고 이 순간 bus라는 개념이 등장하게 된다. bus는 데이터를 A에서 B 지점으로 저송하는 일련의 선들을 이야기 한다.

BUS(중요)

이게 기본적인 논리이다.

하지만 버스는 한 개 이상의 비트를 보내기 위해 제작되었으며 기호는 다음과 같이 사용한다.

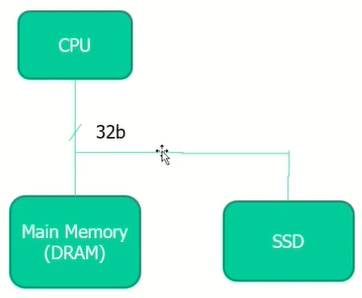

예시를 위해 다음과 같은 그림이 있다고 하면 DRAM과 SSD로부터 데이터를 CPU로 전송하는 전선이 많이 필요한 경우가 생기게 된다. 하지만 한번에 모든 데이터를 보내면 안되기 때문에 버스를 이용하여서 이를 분리하게 된다.

그래서 위 그림과 같이 S값에 따라서 출력값이 선택되고 BUS에 타게 된다.

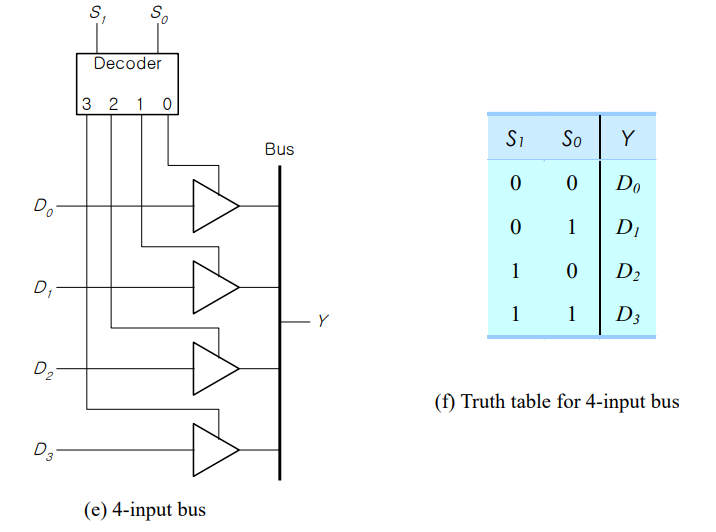

이러한 BUS의 개념을 활용하여서 Decoder을 활용한 BUS를 제작해 볼 수도 있다. 어찌보면 멀티플렉서와 같지만 여기에서는 BUS라는 개념을 사용하여서 멀티플렉서에 비하여 설계가 다소 간편하다는 것을 알 수 있다.

Read-Only Memory(ROM)

read만을 위해 존재하는 메모리이다. write는 오직 한 번만 가능하고 후에 read만 가능하도록 제작된 메모리라고 생각할 수 있다.

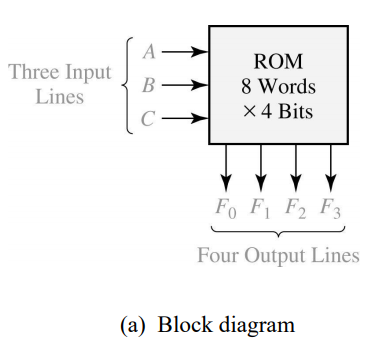

이제 4Bit 짜리 출력을 결정하는 3 Input의 8개의 Word를 출력하는 Decoder과 같은 ROM이 존재한다고 할때

출력결과로 나온 값들을 읽어들여서 이게 어떤 words인지 맞추는 작업을 마지막에 수행하게 된다. 그리고 이때 나온 F 시리즈들이 ROM에 저장되게 된다.

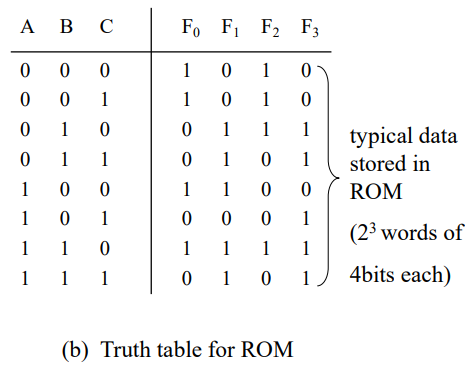

그래서 일반적인 ROM은 위와 같은 구조를 가지게 된다.

AN 8-Word x 4-Bit ROM

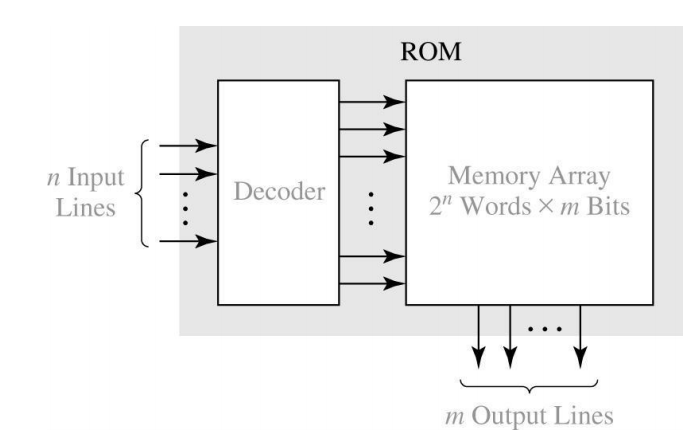

위 그림에서 오른쪽 아래로 향해 있는 화살표는 수직 선과 연결되어 있다는 것을 의미한다. 이때 Decoder의 특징에 따라 출력되는 Output들 중 1이 되는 것이 있고 연결된 수직선이 있다면 해당 수직선으로 HIGH 전압을 보내게 된다.

그래서 위의 그림을 minterm으로 표현하면 오른쪽에 표현된 것과 같은 식들이 나오게 된다.

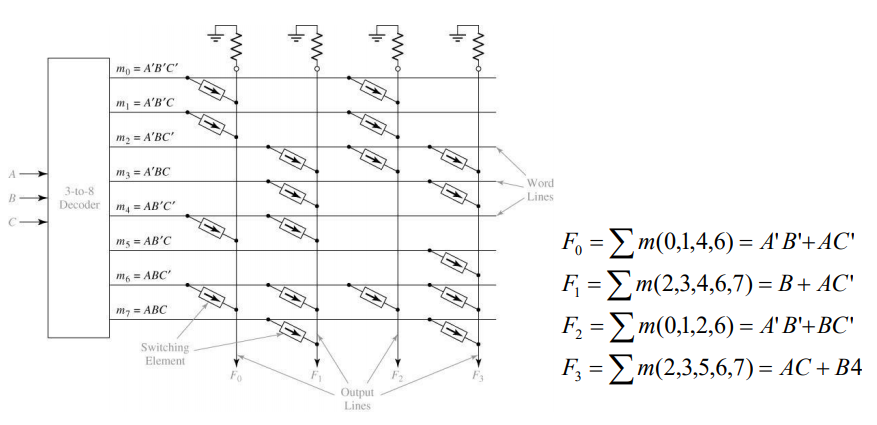

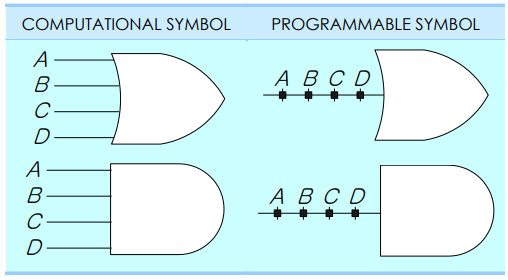

programmable versions of the conceptional AND and OR gate

ROM이라는 것을 다시 생각해보면 program 할수 있는 AND, OR 게이트이다. 이제 ROM 칩을 만들게 될때 제작단계에서 퓨즈를 연결하거나 태워버림으로써 위와 같은 논리식을 제작할 수 있는 것이다.

이러한 것을 위와 같이 선과 점으로 표현하게 된다.

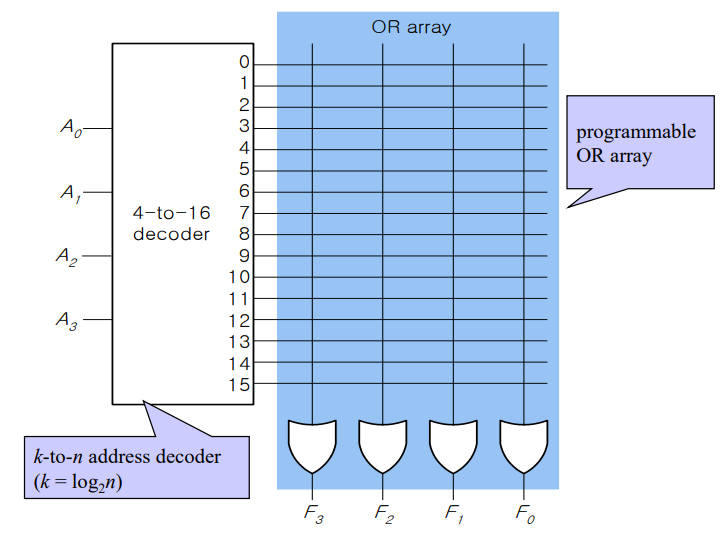

16x4 ROM

위의 전체가 ROM인데 보통은 위와 같이 기타줄들을 늘여 놓고 그리게 된다.

예를 더 들어보면 위와 같은 Boolean Function이 있을때 ROM을 위와 같이 제작할 수 있다.

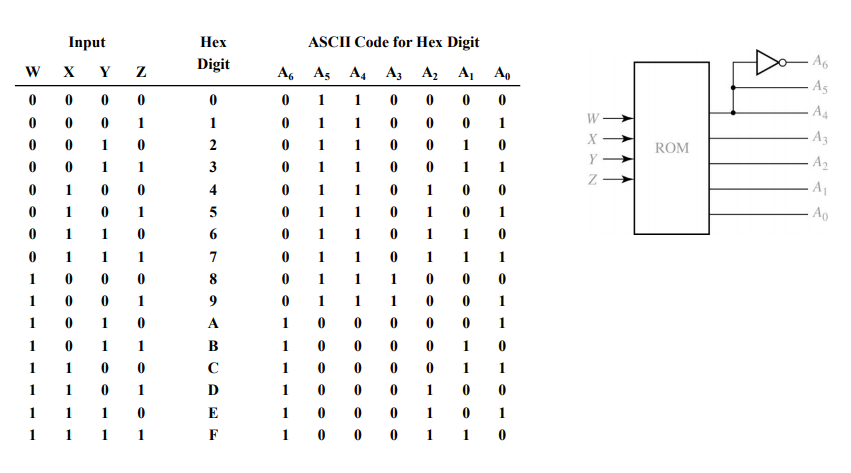

Hexadecimal to ASCII Code Converter

한가지 예시를 더 봐보자 16진수를 ASCII Code로 변환하면 다음과 같은 표가 만들어지게 된다.

Programmable Logic Arrays(PLA)

하드웨어적으로 보다 코스트가 적게 만들 수 있는가를 고민하여 만든것이 Programmable logic arrays(PLAs)라고 부른다.

PLA는 ROM의 INPUT이 많아짐에 따라서 Decoder에서 n 개의 Input에 따른 수십개의 FULL Decoder 출력이 나오게 된다. 하지만 실재 사용되는 것은 생각보다 많지 않기에 이러한 문제를 해결하기 위해서 나온 개념으로 볼 수 있다.

그래서 PLA의 장점은 ROM만큼이나 flexible하고 random logic에 대해 보다 적은 비용이 들어가고, 주로 control logic에서 사용하게 된다.

반면 모든 coefficients, startup programs, test vectors and other random data을 사용하여야 한다면 ROM을 사용하여야 한다.

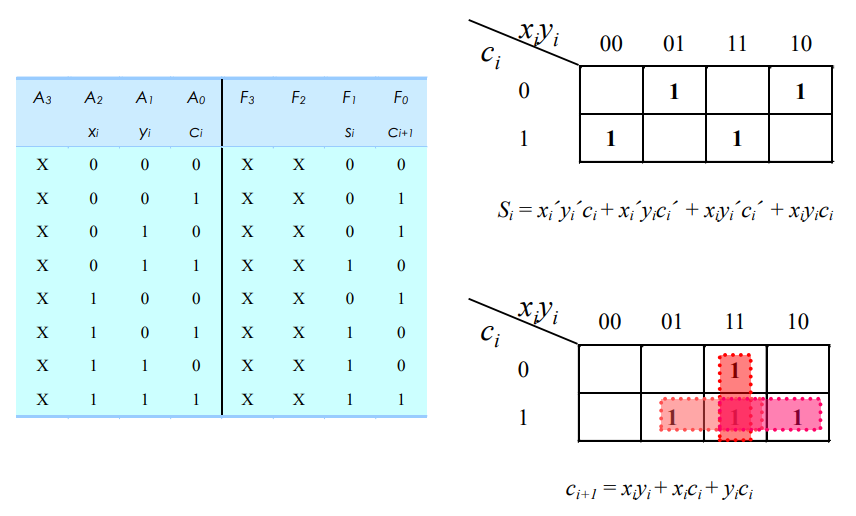

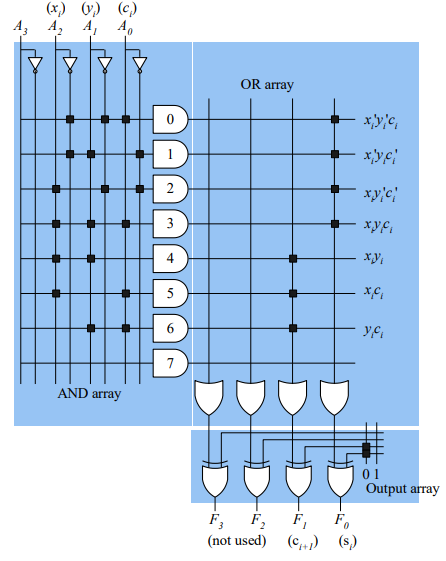

PLA implementation of the full adder

위와 같이 Full Adder을 구성하게 된다면

그냥 ROM으로 제작한다면 위와 같은 형태를 가지게 될 것이다.